Weijie Shi, Zongqiang Yu, Junhai Jiang, Yongqiang Che, Sikun Li. Computational Lithography Technology Under Chip Manufacture Context[J]. Laser & Optoelectronics Progress, 2022, 59(9): 0922001

Search by keywords or author

- Laser & Optoelectronics Progress

- Vol. 59, Issue 9, 0922001 (2022)

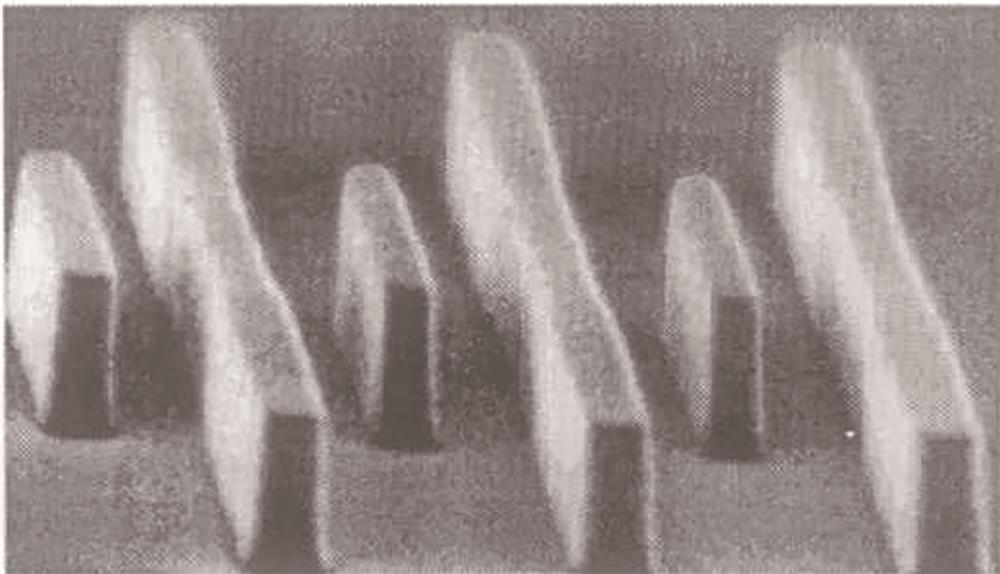

![Optical proximity effect[7]](/richHtml/lop/2022/59/9/0922001/img_01.jpg)

Fig. 1. Optical proximity effect[7]

![OPRX workflow[8]](/richHtml/lop/2022/59/9/0922001/img_02.jpg)

Fig. 2. OPRX workflow[8]

Fig. 3. OPC for line-end shorting and corner rounding[9]

Fig. 4. Source shapes of conventional illumination and off-axis illumination[10]

Fig. 5. Enhancement of isoline imaging with sub-resolution bars[11]

Fig. 6. Schematic diagram of rule-based SBAR addition method for one-dimensional and two-dimensional graphics

Fig. 7. Computational lithographic tools in modern IC manufacturing.

Fig. 8. OPC scheme [17]

Fig. 9. Lithography simulation model[17]

Fig. 10. Scheme of model-based OPC

Fig. 11. Pinch and bridging defects[18]

Fig. 12. SMO workflow[22]

Fig. 13. Full-chip SMO workflow[24].

Fig. 14. DPT process based on two graph splitting methods[25]. (a) Pattern to be split with a half period of 32 nm; (b) split graphics; (c) split patterns are placed on different masks respectively; (d) OPC for each mask; (e) photoresist pattern after exposure of each mask; (f) final photoresist pattern

Fig. 15. Rule-based DPT coloring method[27]

Fig. 16. Application of ILT for mask optimization[29]. (a) Target layout graphics; (b) curve mask pattern; (c) simplified mask pattern

Fig. 17. Images and polygons hybrid-optimization ILT flow

Fig. 18. Speed-up of full-chip ILT optimization using deep learning[36]

Fig. 19. Scheme of DTCO functions[38]

Fig. 20. ASML holistic lithography[40]

Fig. 21. From design to chip whole flow co-optimization

|

Table 1. Resolution enhancement progress with Rayleigh criteria

Set citation alerts for the article

Please enter your email address