[1] B J. Power MOSFETs Baliga. Fundamentals of power semiconductor devices. Boston, MA: Springer US, 276(2008).

[2] S Q Ji, Z Y Zhang, F Wang. Overview of high voltage sic power semiconductor devices: Development and application. CES Trans Electr Mach Syst, 1, 254(2017).

[3] J A Cooper, A Agarwal. SiC power-switching devices-the second electronics revolution. Proc IEEE, 90, 956(2002).

[4] G Y Wang, F Wang, G R Magai et al. Performance comparison of 1200V 100A SiC MOSFET and 1200V 100A silicon IGBT. 2013 IEEE Energy Convers Congr Expo, 3230(2013).

[5] T Nakamura, Y Nakano, M Aketa et al. High performance SiC trench devices with ultra-low

[6] M Sampath, D T Morisette, J A Cooper. Comparison of single- and double-trench UMOSFETs in 4H-SiC. Mater Sci Forum, 924, 752(2018).

[7] S Krishnaswami, M Das, B Hull et al. Gate oxide reliability of 4H-SiC MOS devices. 2005 IEEE International Reliability Physics Symposium, 592(2005).

[8] S M Xu, C H Ren, Y C Liang et al. Theoretical analysis and experimental characterization of the dummy-gated VDMOSFET. IEEE Trans Electron Devices, 48, 2168(2001).

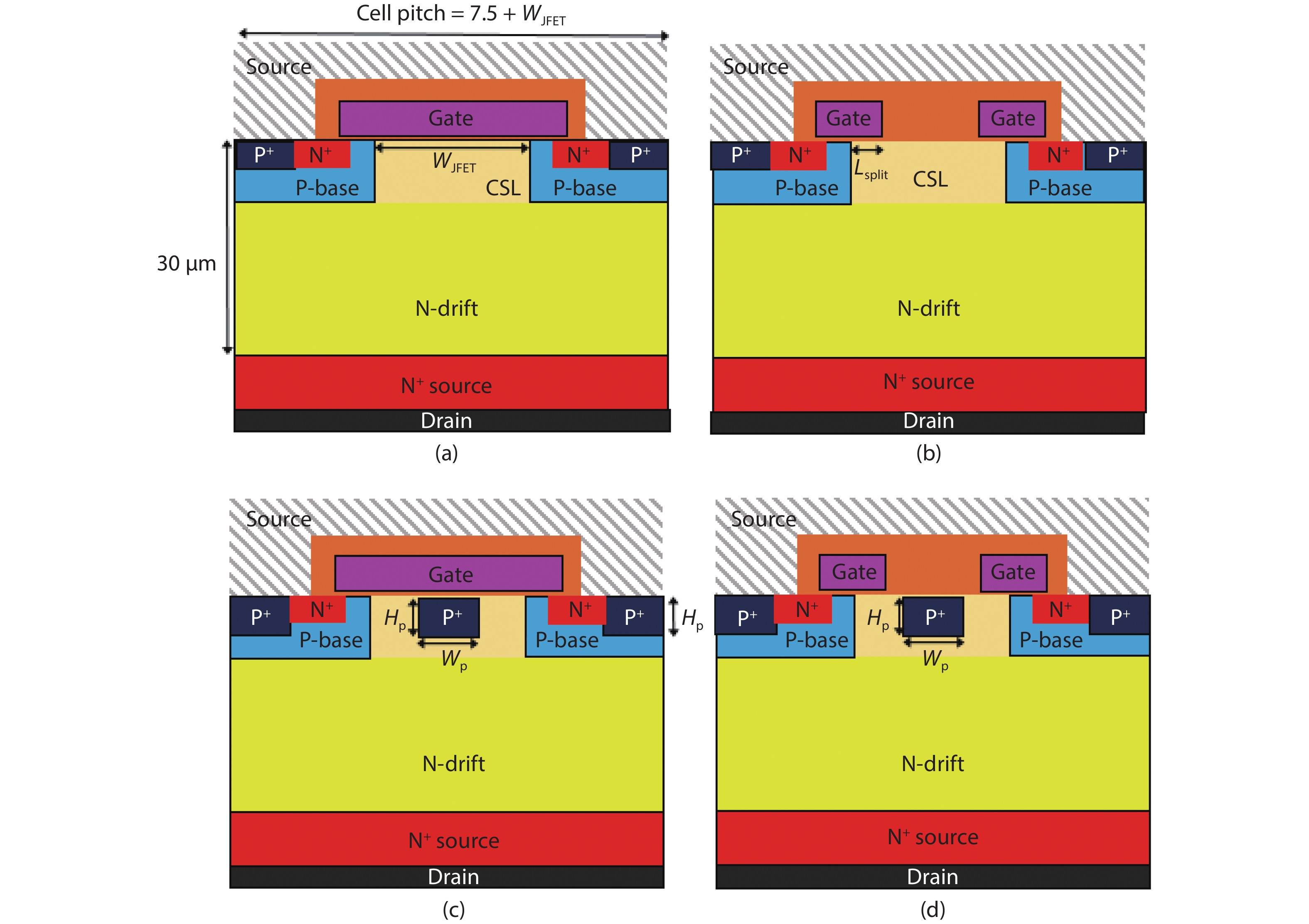

[9] A Agarwal, K Han, B J Baliga. 2.3 kV 4H-SiC accumulation-channel split-gate planar power MOSFETs with reduced gate charge. IEEE J Electron Devices Soc, 8, 499(2020).

[10] K Han, B J Baliga, W Sung. A novel 1.2 kV 4H-SiC buffered-gate (BG) MOSFET: Analysis and experimental results. IEEE Electron Device Lett, 39, 248(2018).

[11] P Vudumula, S Kotamraju. Design and optimization of 1.2-kV SiC planar inversion MOSFET using split dummy gate concept for high-frequency applications. IEEE Trans Electron Devices, 66, 5266(2019).

[12] Q C J Zhang, J Duc, B Hull et al. CIMOSFET: A new MOSFET on SiC with a superior

[13] Q J Zhang, G Y Wang, H Doan et al. Latest results on 1200 V 4H-SiC CIMOSFETs with

[14]

[15] M N Darwish, J L Lentz, M R Pinto et al. An improved electron and hole mobility model for general purpose device simulation. IEEE Trans Electron Devices, 44, 1529(1997).

[16]

[17] K Han, B J Baliga, W Sung. Split-gate 1.2-kV 4H-SiC MOSFET: Analysis and experimental validation. IEEE Electron Device Lett, 38, 1437(2017).

[18] J Wei, M Zhang, H P Jiang et al. Low ON-resistance SiC trench/planar MOSFET with reduced OFF-state oxide field and low gate charges. IEEE Electron Device Lett, 37, 1458(2016).

[19] J Wei, M Zhang, H P Jiang et al. Dynamic degradation in SiC trench MOSFET with a floating p-shield revealed with numerical simulations. IEEE Trans Electron Devices, 64, 2592(2017).

[20] M Ren, Z Chen, B Niu et al. A low miller capacitance VDMOS with shield gate and oxide trench. 2016 IEEE International Nanoelectronics Conference (INEC), 1(2016).

[21] T Basler, D Heer, D Peters et al. Practical aspects and body diode robustness of a 1200 V SiC trench MOSFET. International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 1(2018).

[22] A Maerz, T Bertelshofer, M Bakran et al. A novel gate drive concept to eliminate parasitic turn-on of SiC MOSFET in low inductance power modules. International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 1(2017).

[23] K Tian, A Hallén, J W Qi et al. An improved 4H-SiC trench-gate MOSFET with low ON-resistance and switching loss. IEEE Trans Electron Devices, 66, 2307(2019).

[24] T Morikawa, T Ishigaki, A Shima. Device design consideration for robust SiC VDMOSFET with self-aligned channels formed by tilted implantation. IEEE Trans Electron Devices, 66, 3447(2019).

[25] X T Zhou, R F Yue, J Zhang et al. 4H-SiC trench MOSFET with floating/grounded junction barrier-controlled gate structure. IEEE Trans Electron Devices, 64, 4568(2017).