Xiuxin Xia, Xiaoxi Li, Hanwen Wang. Metal–insulator transition in few-layered GaTe transistors[J]. Journal of Semiconductors, 2020, 41(7): 072902

Search by keywords or author

- Journal of Semiconductors

- Vol. 41, Issue 7, 072902 (2020)

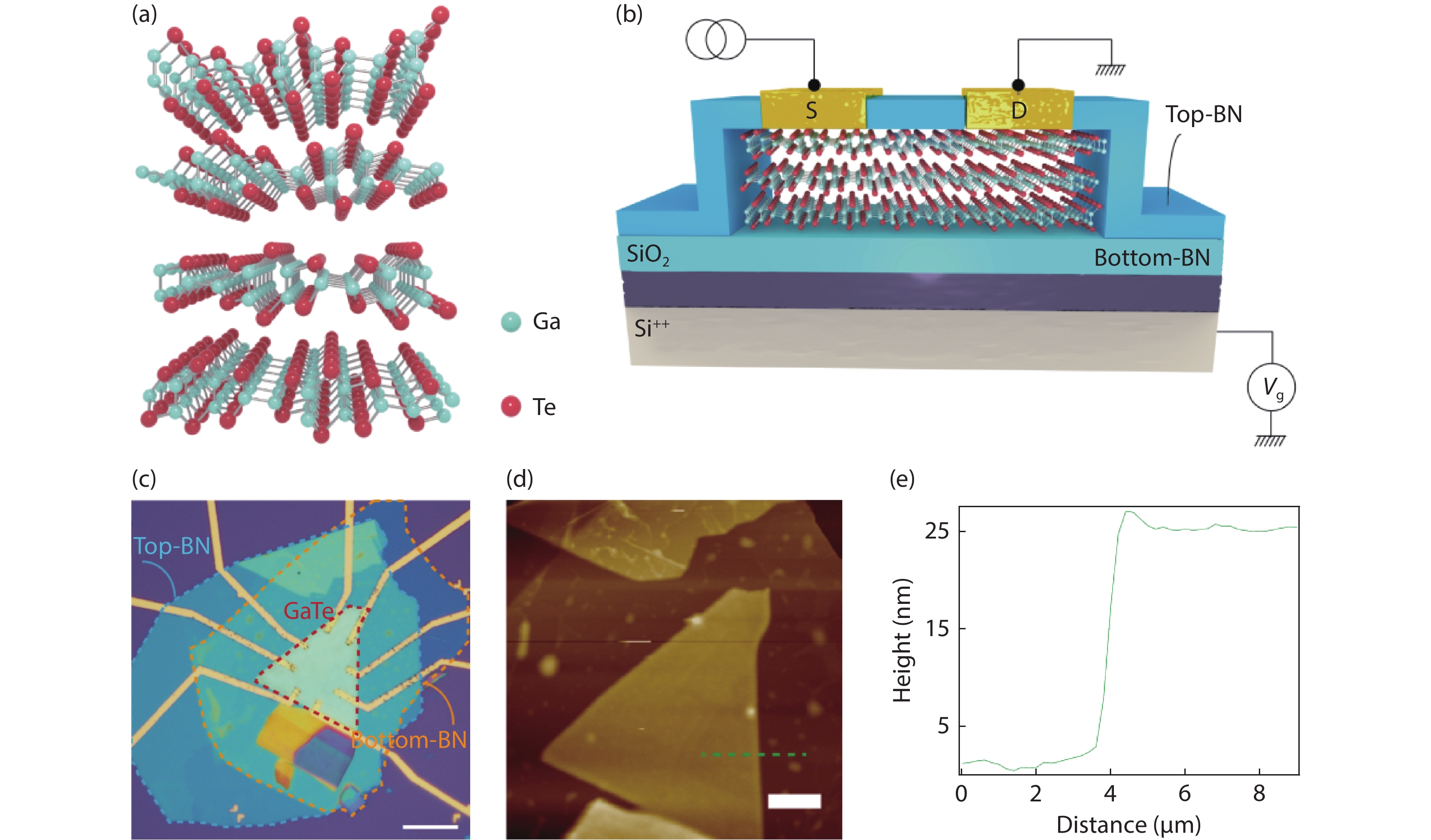

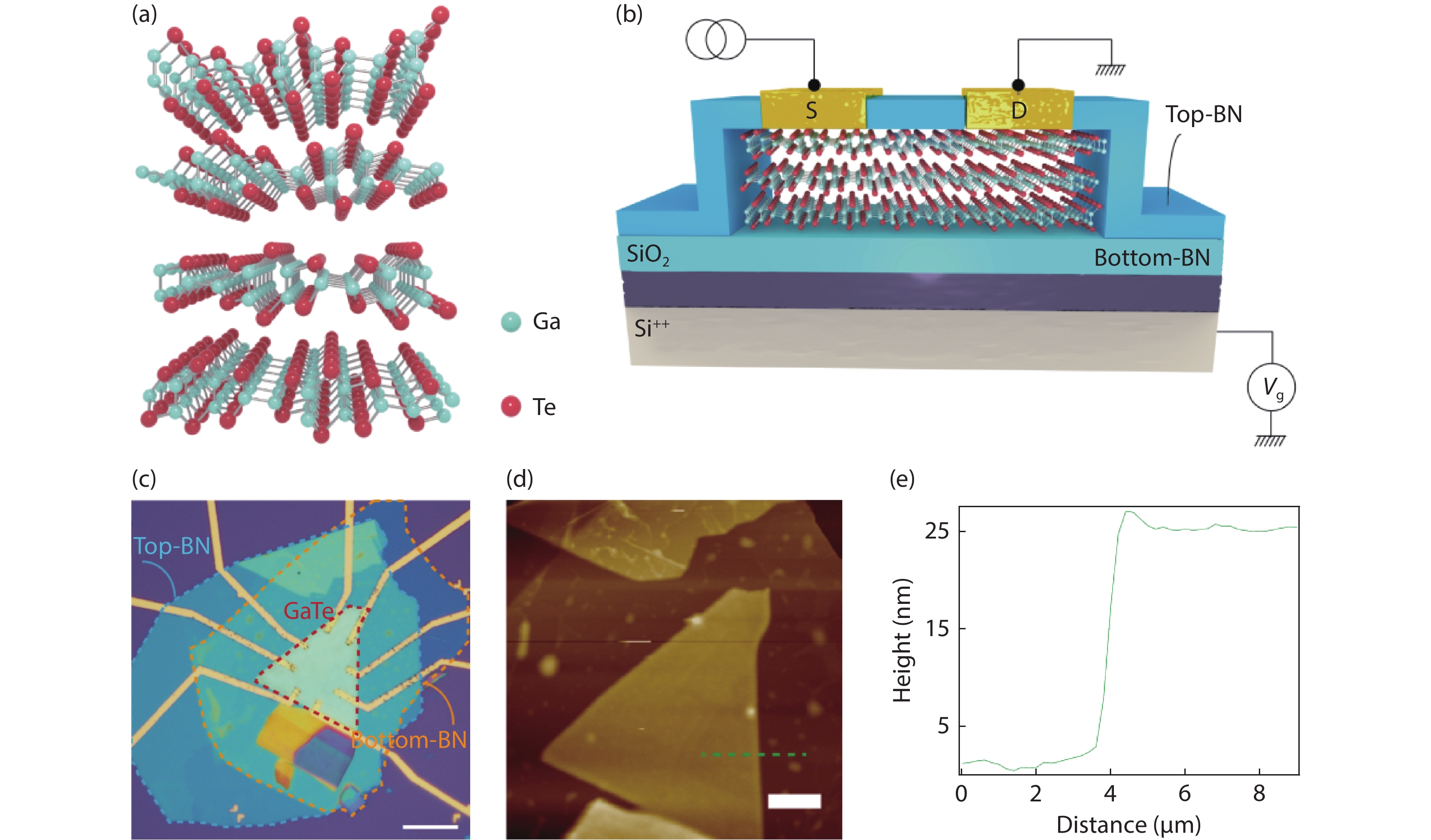

Fig. 1. (Color online) Characterizations of GaTe and a typical BN/GaTe/BN device. (a) Schematic of GaTe layered lattice, with the interlayer spacing of ~0.8 nm. (b) Schematic illustration of the device. (c) Optical micrograph of the device, the scale bar is 10 µ m. (d) AFM morphology image of the device with a height profile plotted in (e), plotted along the green dashed line in (d).

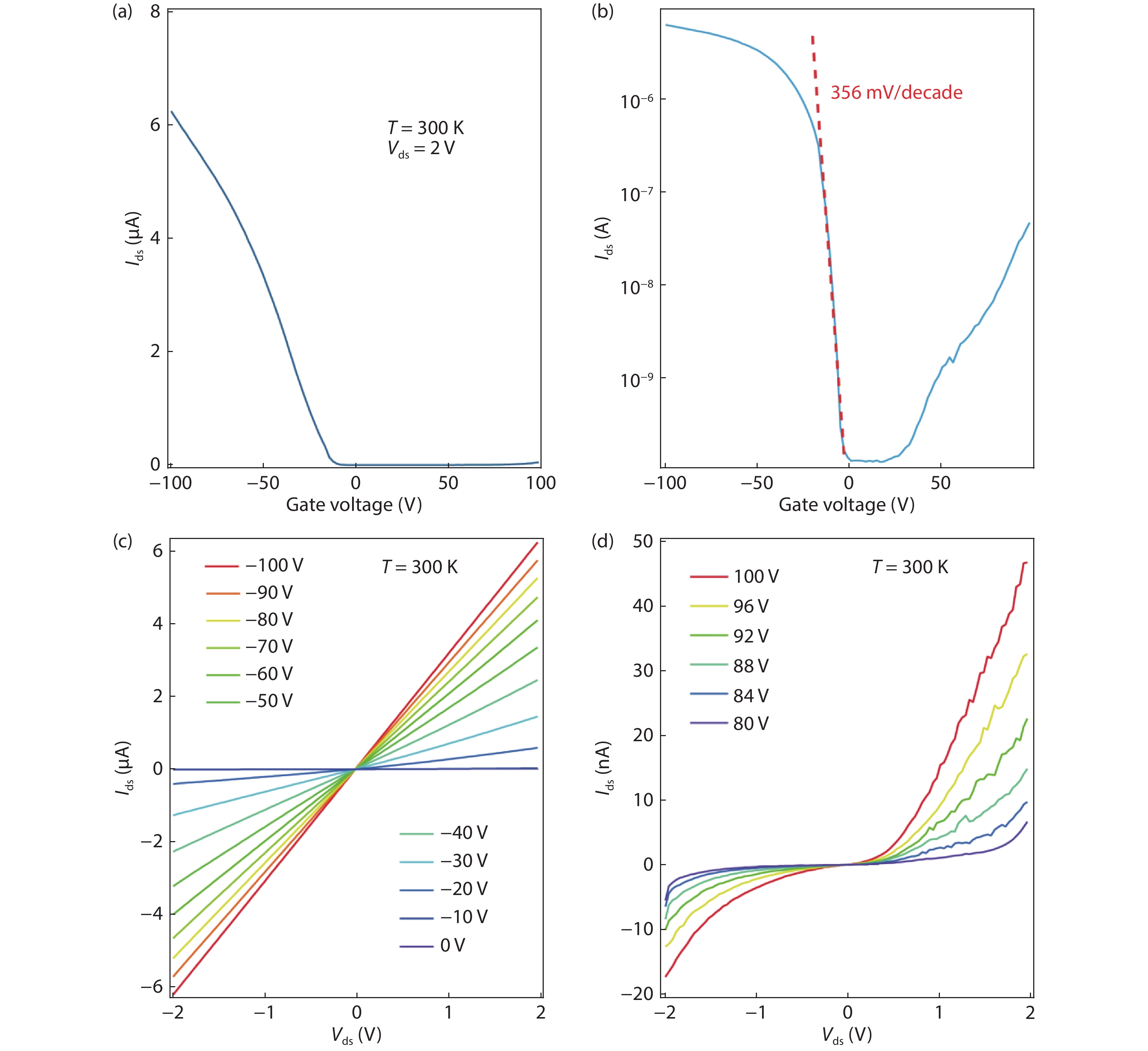

Fig. 2. (Color online) Electrical transport properties of BN/GaTe/BN devices at room temperature. (a) Field effect curve at V ds = 2 V of the device. (b) The same data plotted in a log scale. (c) I ds–V ds curves on the hole side at fixed gate voltages. (d) I ds–V ds curves on the electron side at fixed gate voltages.

Fig. 3. (Color online) Transport properties of BN/GaTe/BN devices at different temperatures. (a) Color map of I–V curves as a function of gate voltage at different temperatures. To enhance the visibility, color scales are set to cutoffs at ±1 nA. (b, c) Line cuts in (a), with output curves on hole and electron sides, respectively.

Fig. 4. (Color online) Temperature-dependent transport characteristics in few-layered GaTe device with a constant voltage V ds = 2 V. (a) T -dependence of conductivity σ for different gate voltages. (b) I ds–V g at different temperatures, I ds increases when the temperature decreases at high negative gate voltage V g < −30 V. (c) Field-effect mobility as a function of temperature. The solid black line is best fitted to the power law in the range of 100–250 K.

Set citation alerts for the article

Please enter your email address