Yifan Fu, Liuhong Ma, Zhiyong Duan, Weihua Han. Effect of charge trapping on electrical characteristics of silicon junctionless nanowire transistor[J]. Journal of Semiconductors, 2022, 43(5): 054101

Search by keywords or author

- Journal of Semiconductors

- Vol. 43, Issue 5, 054101 (2022)

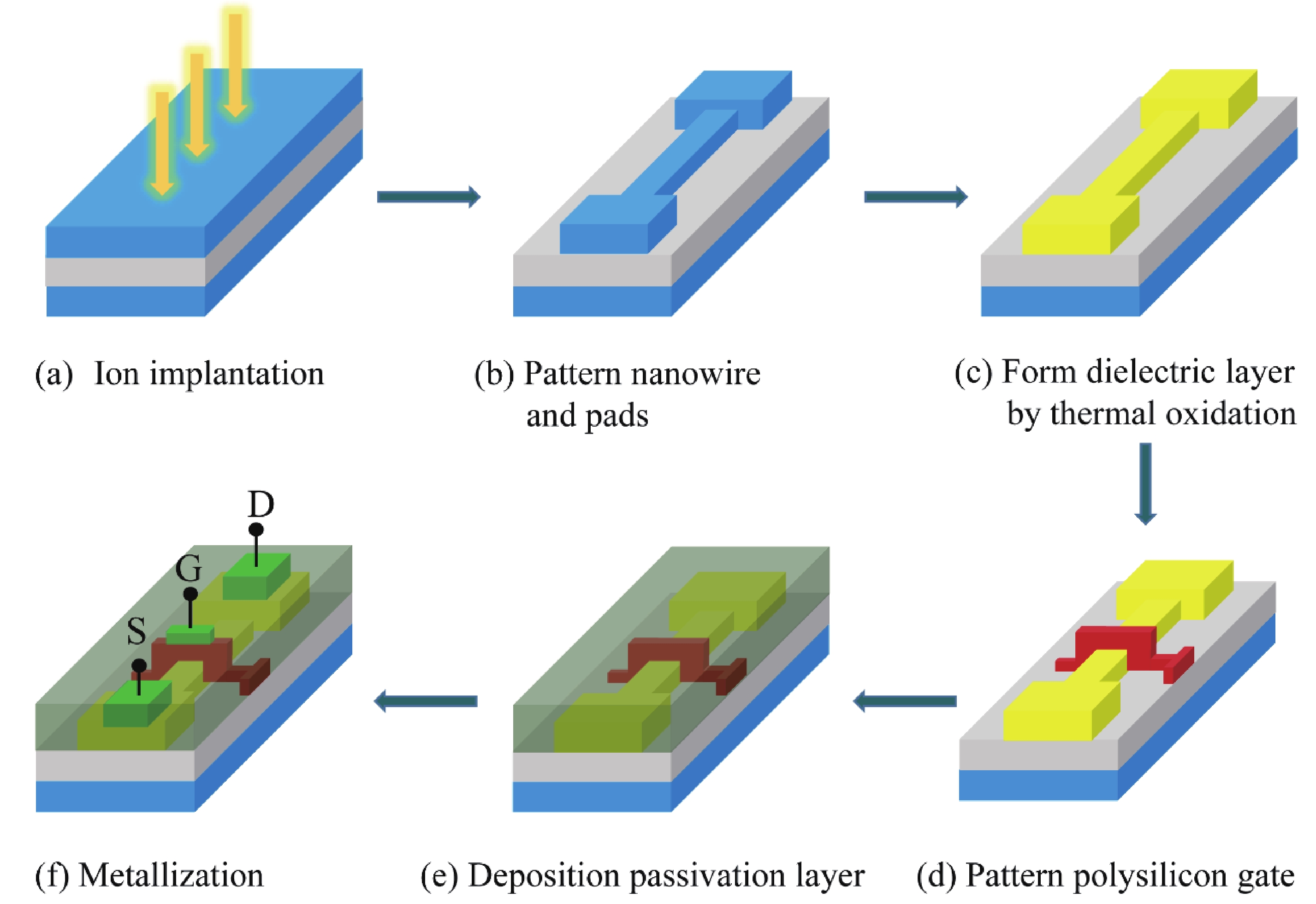

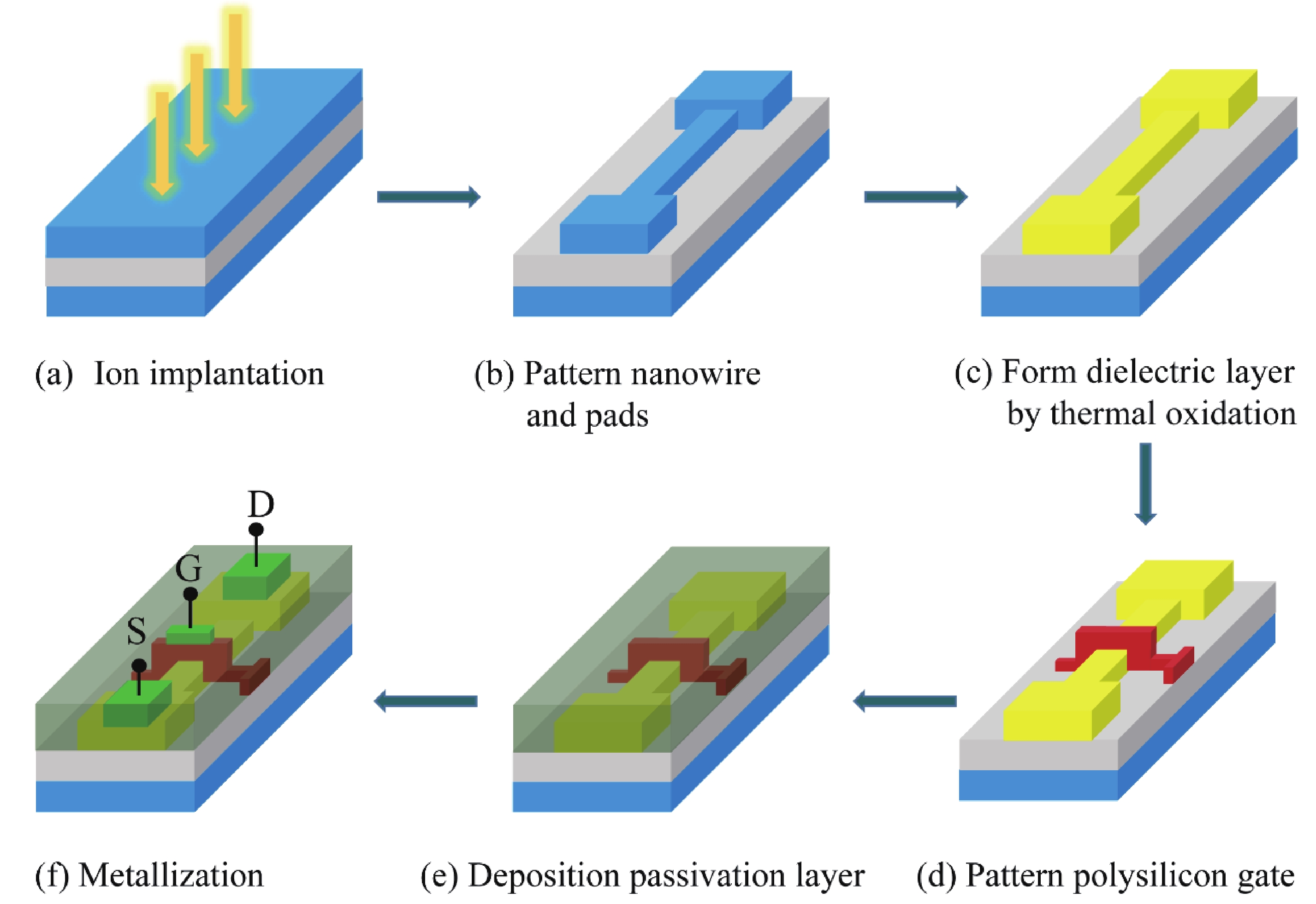

Fig. 1. (Color online) Schematic diagrams of the fabrication process for JNTs.

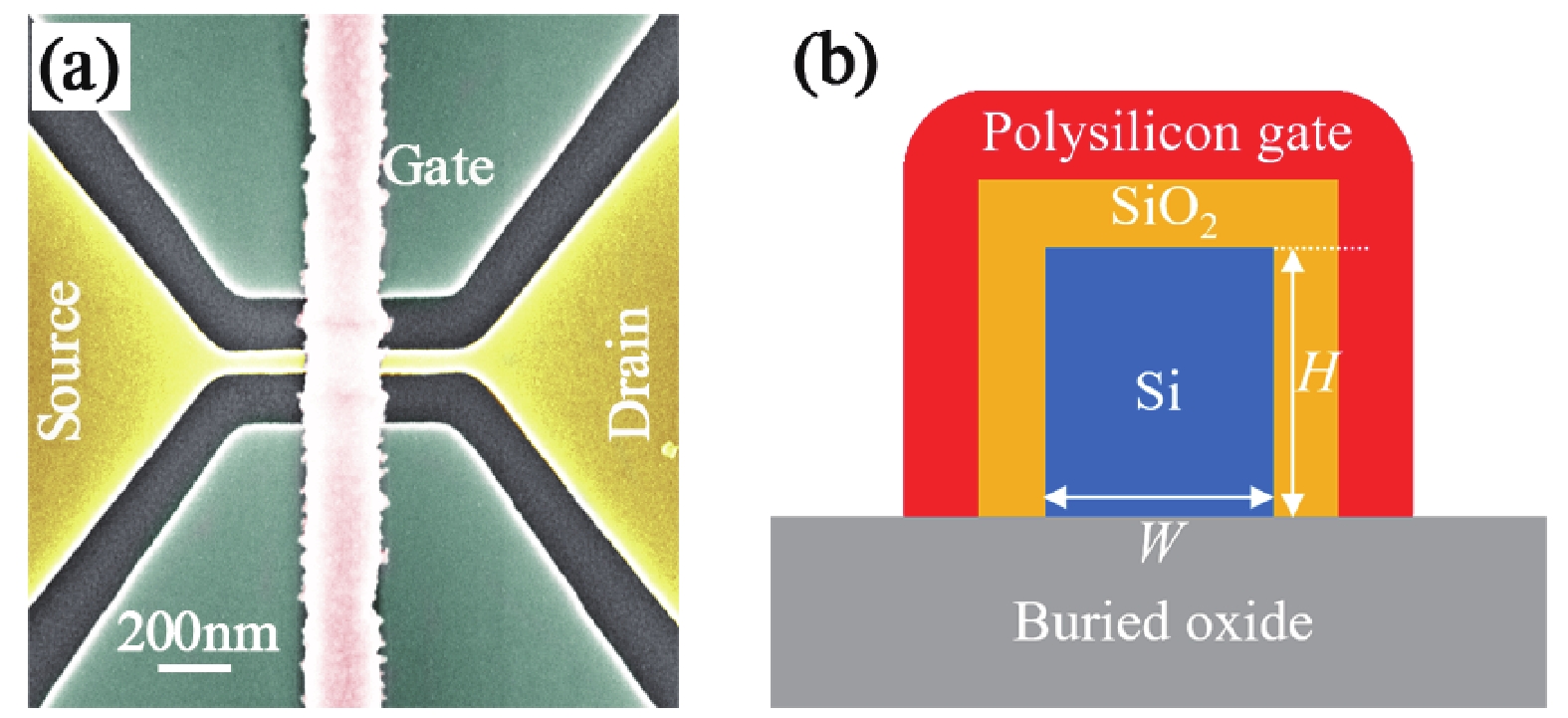

Fig. 2. (Color online) (a) The color SEM image of devices with the gate length of 280 nm. (b) The cross-section schematics of the devices.

Fig. 3. (Color online) Measured drain current characteristics at room temperature, showing (a) drain current versus gate voltage for drain voltages of 0.1 to 4.1 V with step of 1 V, and (b) drain current versus drain voltage for gate voltages from 1 to 4 V with step of 1 V.

Fig. 4. (Color online) (a) I DS–V DS output characteristics of JNT device at T = 10 K. (b) The transfer characteristics of the JNT with V GS sweep from 0 to 3.5 V and back.

Fig. 5. (Color online) (a) I DS–V GS curves for V DS values ranging from 2 to 10 mV in steps of 2 mV. The detail image in the upper left corner is an enlarged detail. (b) Time domain current levels versus time trace at V GS = 2.2 V and V DS = 10 mV.

Fig. 6. (Color online) ln(τ c/τ e) and its linear fitting. The slope is proportional to x T, the position of the traps in the oxide.

Fig. 7. (Color online) (a) Transfer characteristics at the temperatures of 100 to 300 K with the step of 50 K. (b) Measured V TH and SS at V DS = 0.1 V versus temperature. The black dashed line represents the theoretical value of subthreshold swing SStheo.

Fig. 8. (Color online) (a) Simulated I DS–V GS curves for different trap densities with the trap level equals to the intrinsic Fermi level. (b) Threshold voltage as a function of trap densities with different trap levels.

Set citation alerts for the article

Please enter your email address