Fuyou Liao, Hongjuan Wang, Xiaojiao Guo, Zhongxun Guo, Ling Tong, Antoine Riaud, Yaochen Sheng, Lin Chen, Qingqing Sun, Peng Zhou, David Wei Zhang, Yang Chai, Xiangwei Jiang, Yan Liu, Wenzhong Bao. Charge transport and quantum confinement in MoS2 dual-gated transistors[J]. Journal of Semiconductors, 2020, 41(7): 072904

Search by keywords or author

- Journal of Semiconductors

- Vol. 41, Issue 7, 072904 (2020)

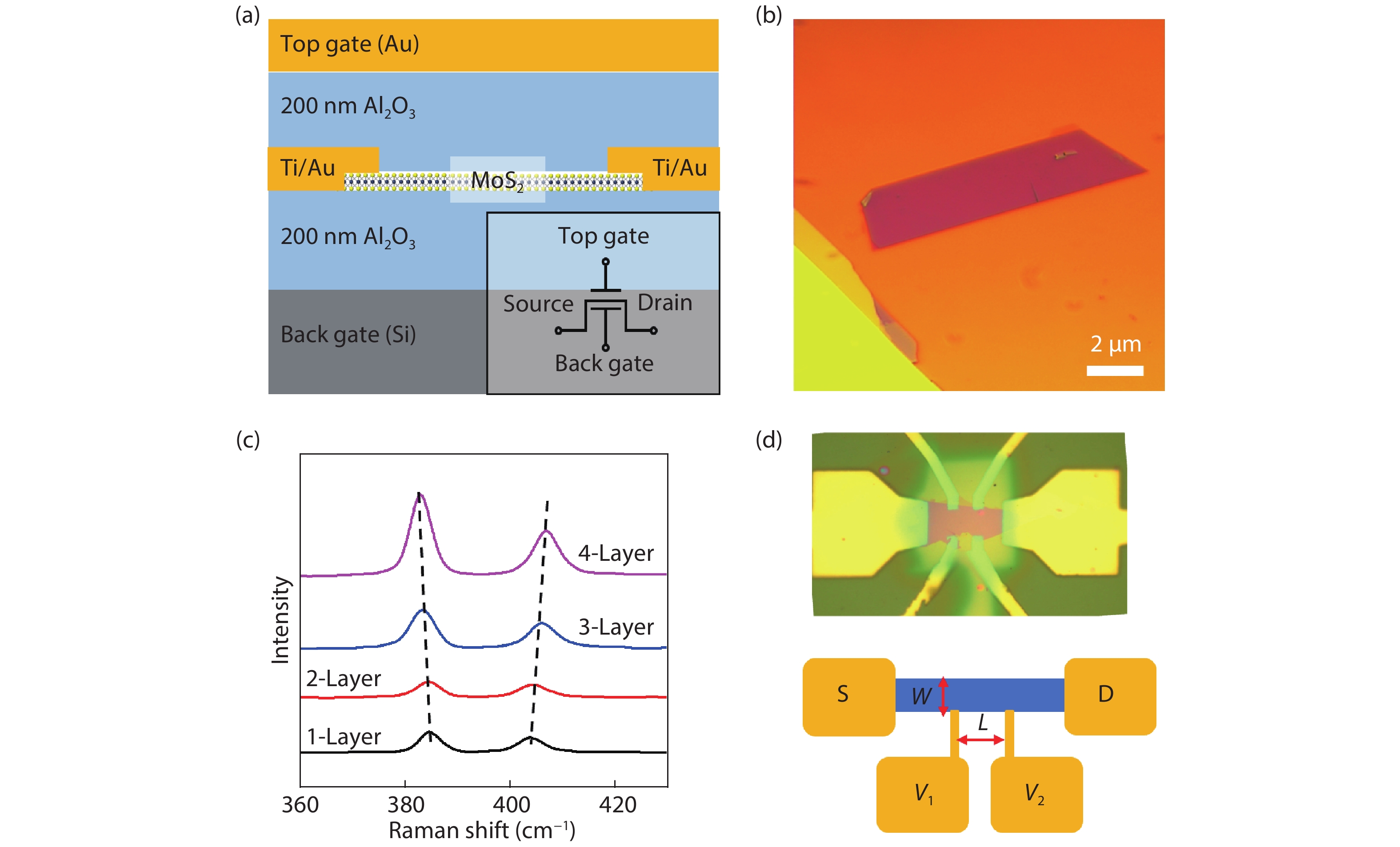

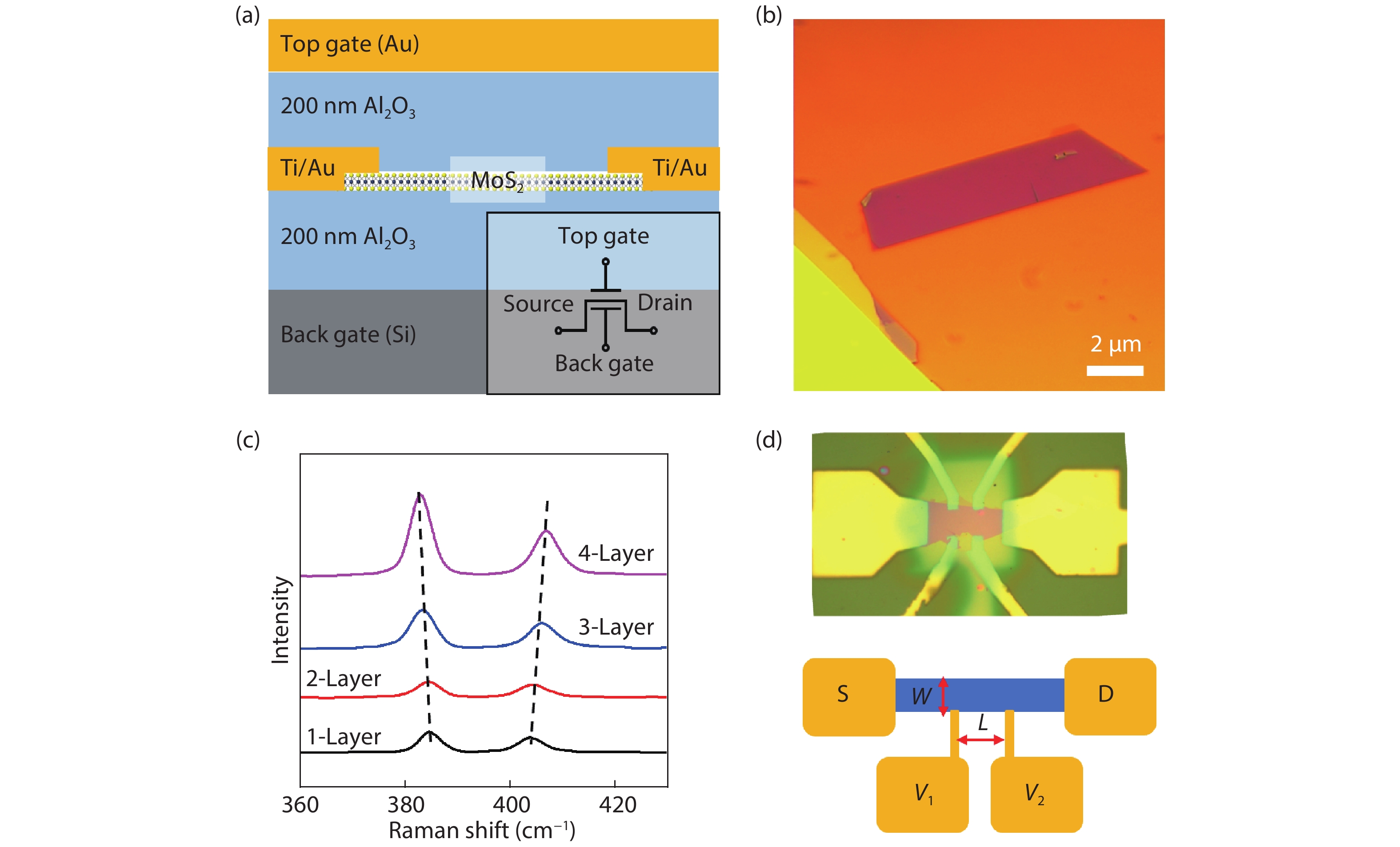

Fig. 1. (Color online) (a) Side-view schematic illustration of a MoS2 DG-FET. (b) Optical microscopic image of an exfoliated MoS2 sheet on a 200-nm-thick Al2O3 substrate. (c) Raman spectra of MoS2 sheets with thickness ranging from 1L to 4L. (d) Optical image of a typical 4-terminal device, the top gate electrode is relatively thin (15 nm) but still conductive. The lower graph is a schematic of the 4-terminal device in which W is the channel width and L is the distance between two inner pads. V 1 and V 2 are used to gauge the voltage drop between two inner contacts.

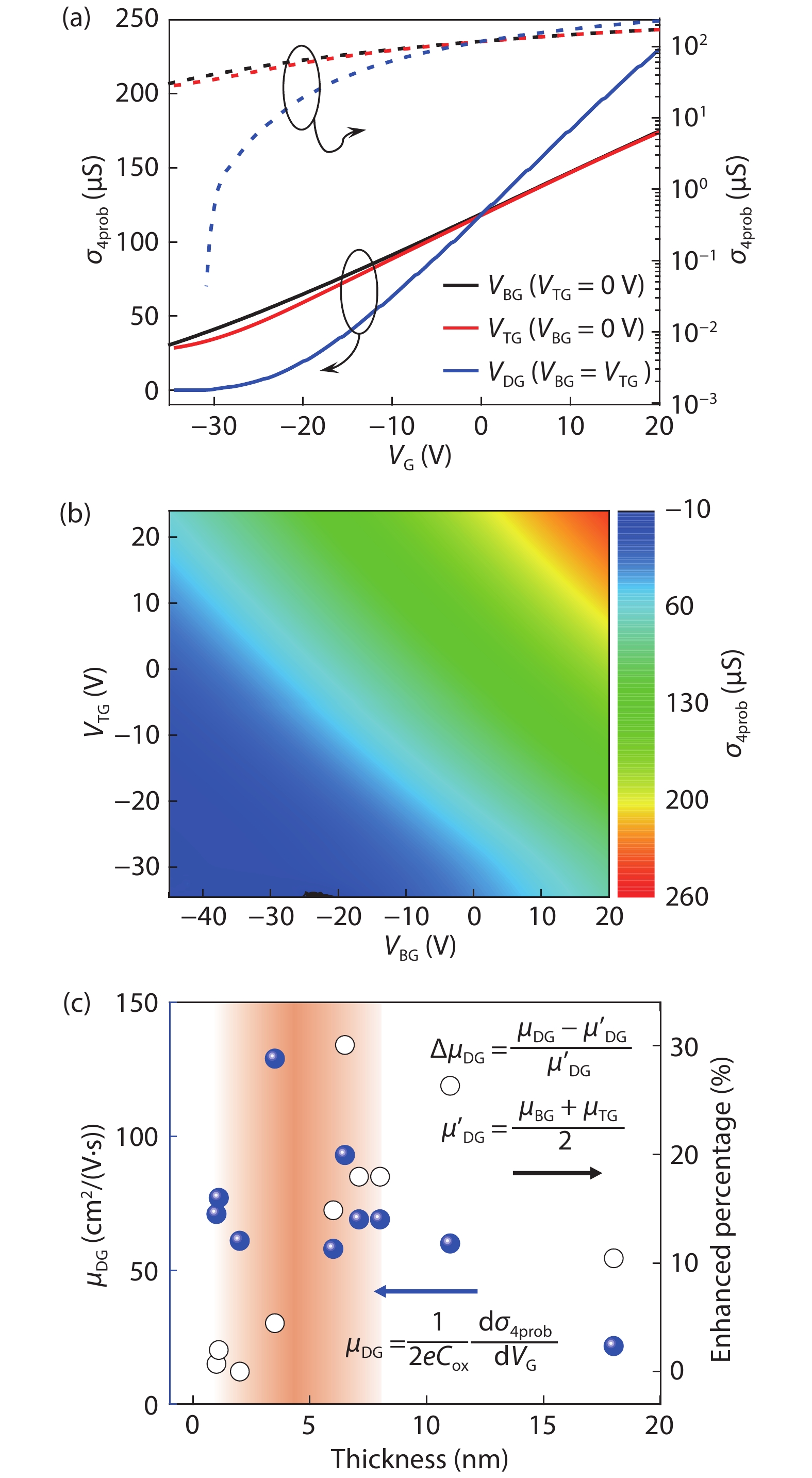

Fig. 2. (Color online) (a) Four-terminal conductivity σ 4prob as functions of BG, TG and DG voltages. Solid and dashed curves correspond to linear and logarithmic coordinates, respectively. (b) 2D contour plot of σ 4prob as functions of V BG and V TG at room temperature. (c) Mobility versus sheet thickness collected from 10 MoS2 DG-FETs work under DG mode.

Fig. 3. (Color online) (a) With and (b) without considering quantum confinement effect, the simulation results of carrier redistribution of a 2-nm-thick MoS2. The upper and lower panels show the simulation results from the SG (V BG= 10 V) and DG (V BG= V TG= 10 V) device, respectively. (c) The electron density in the channel of the DG MoS2 device versus channel thickness. The dielectric layer is 200 nm Al2O3. for all devices

Fig. 4. (Color online) Temperature dependence electrical measurement. (a) The temperature-dependent σ as a function of V DG of a four-probe device. MoS2 is ~5 nm thick with 200 nm Al2O3 of both TG and BG dielectrics. (b) The temperature-dependent mobility extracted from monolayer MoS2 (black dot) and multi-layer MoS2 DG-FET (red square). Monolayer MoS2 DG-FET is 15 nm HfO2 of both TG and BG dielectrics.

Set citation alerts for the article

Please enter your email address