Xian Zhang, Xiaodong Cao, Xuelian Zhang. A 16-bit 1 MSPS SAR ADC with foreground calibration and residual voltage shift strategy[J]. Journal of Semiconductors, 2020, 41(12): 122401

Search by keywords or author

- Journal of Semiconductors

- Vol. 41, Issue 12, 122401 (2020)

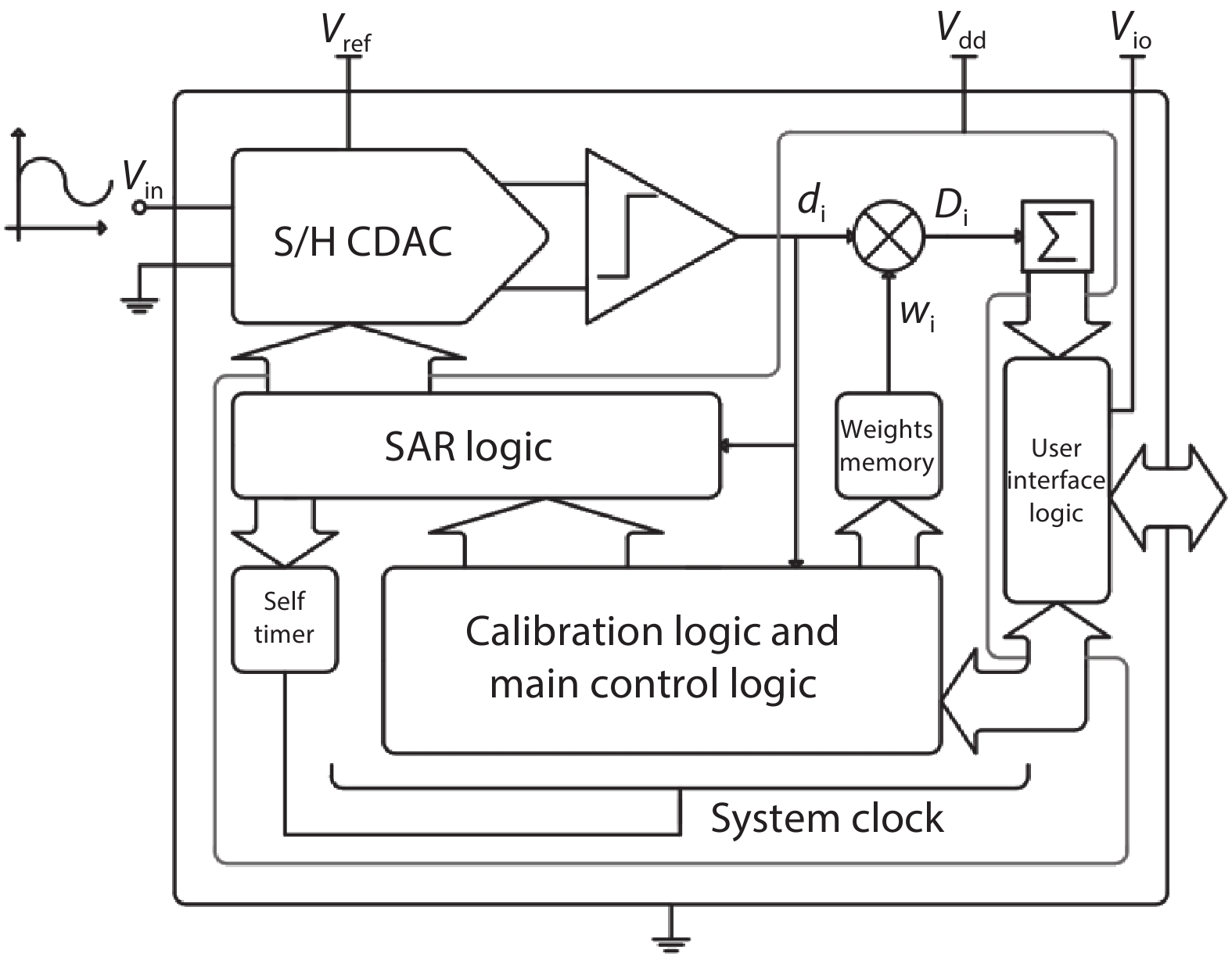

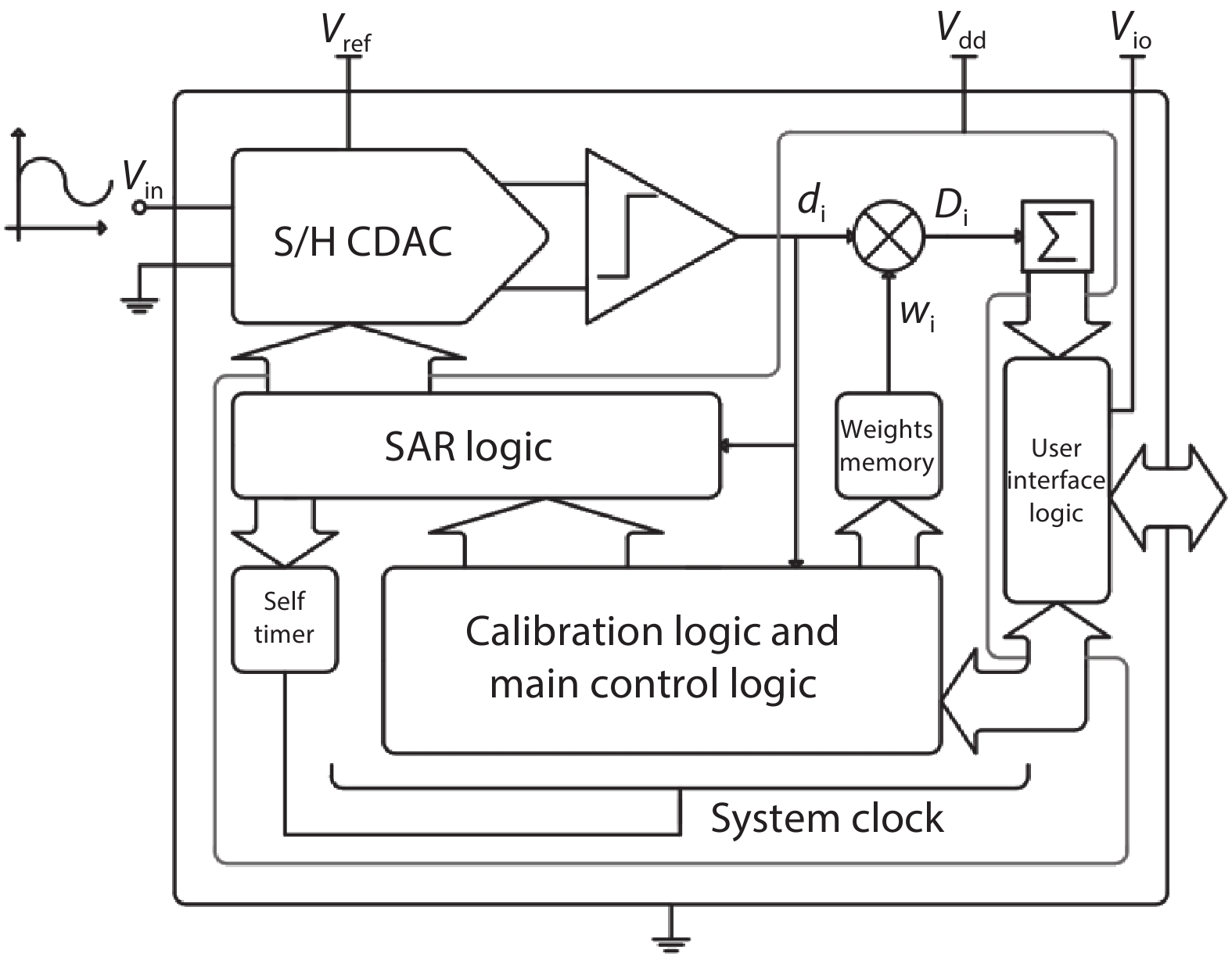

Fig. 1. The ADC system architecture.

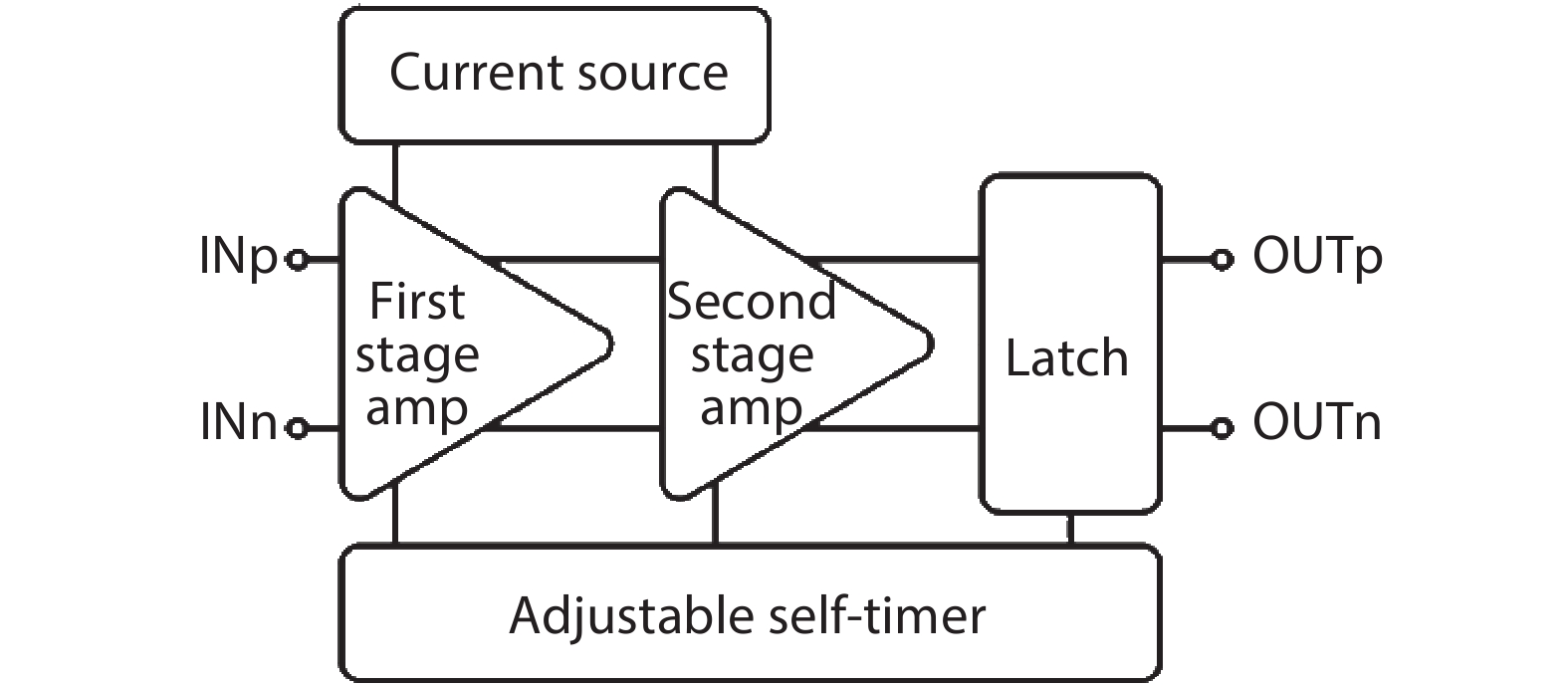

Fig. 2. Comparator block diagram.

Fig. 3. Preamplifier.

Fig. 4. Multiphase clock of the self-timer.

Fig. 5. The schematic of half CDAC.

Fig. 6. (a) Control logic circuit. (b) High-segment MUX switch circuit.

Fig. 7. (a) Weights of a 6 phase SAR ADC and the start phase. (b) Residual voltage curves of P and N curves.

Fig. 8. (Color online) (a) Simulation residual voltage with third bit error. (b) Simulation residual voltage with second bit error.

Fig. 9. Simulated noise floor level versus number of RS bits.

Fig. 10. (Color online) (a) Residual voltage curves. (b) Start phase and RS bits.

Fig. 11. (Color online) Simulated INL and DNL with/without RS strategy.

Fig. 12. (Color online) Simulated noise floor with/without RS-based dither.

Fig. 13. (a) Calibration start phase of the P bits (b) Calibration start phase of the N bits.

Fig. 14. (Color online) Simulated noise floor level versus average number.

Fig. 15. Auto-balance circuit.

Fig. 16. (Color online) Simulated results of INL and DNL with/without calibration.

Fig. 17. (Color online) Simulated results of noise floor with/without calibration.

Fig. 18. Simulated results of the average absolute value of weight errors versus temperature.

Fig. 19. (Color online) The layout of the 16bit 1MSPS SAR ADC with on-chip calibration.

Fig. 20. (Color online) The post-layout simulated result of the residual voltage.

Table 1. Weight calculation.

|

Table 2. The comparison with high-resolution and medium-speed SAR ADCs.

Set citation alerts for the article

Please enter your email address