[1] W Kim, H K Hong, Y J Roh et al. A 0.6 V 12 b 10 MS/s low-noise asynchronous SAR-assisted time-interleaved SAR (SATI-SAR) ADC. IEEE J Solid-State Circuits, 51, 1826(2016).

[2] A Shikata, R Sekimoto, T Kuroda et al. A 0.5 V 1.1 MS/sec 6.3 fJ/conversion-Step SAR-ADC with tri-level comparator in 40 nm CMOS. IEEE J Solid-State Circuits, 47, 1022(2012).

[3] P Harpe, E Cantatore, A van Roermund. A 10b/12b 40 kS/s SAR ADC with data-driven noise reduction achieving up to 10.1b ENOB at 2.2 fJ/conversion-step. IEEE J Solid-State Circuits, 48, 3011(2013).

[4] P Nuzzo, F De Bernardinis, P Terreni et al. Noise analysis of regenerative comparators for reconfigurable ADC architectures. IEEE Trans Circuits Syst I, 55, 1441(2008).

[5] B Verbruggen, J Tsouhlarakis, T Yamamoto et al. A 60 dB SNDR 35 MS/s SAR ADC with comparator-noise-based stochastic residue estimation. IEEE J Solid-State Circuits, 50, 2002(2015).

[6] J Y Zhong, Y Zhu, C H Chan et al. A 12b 180MS/s 0.068mm2 with full-calibration-integrated pipelined-SAR ADC. IEEE Trans Circuits Syst I, 64, 1684(2017).

[7] N Verma, A P Chandrakasan. An ultra low energy 12-bit rate-resolution scalable SAR ADC for wireless sensor nodes. IEEE J Solid-State Circuits, 42, 1196(2007).

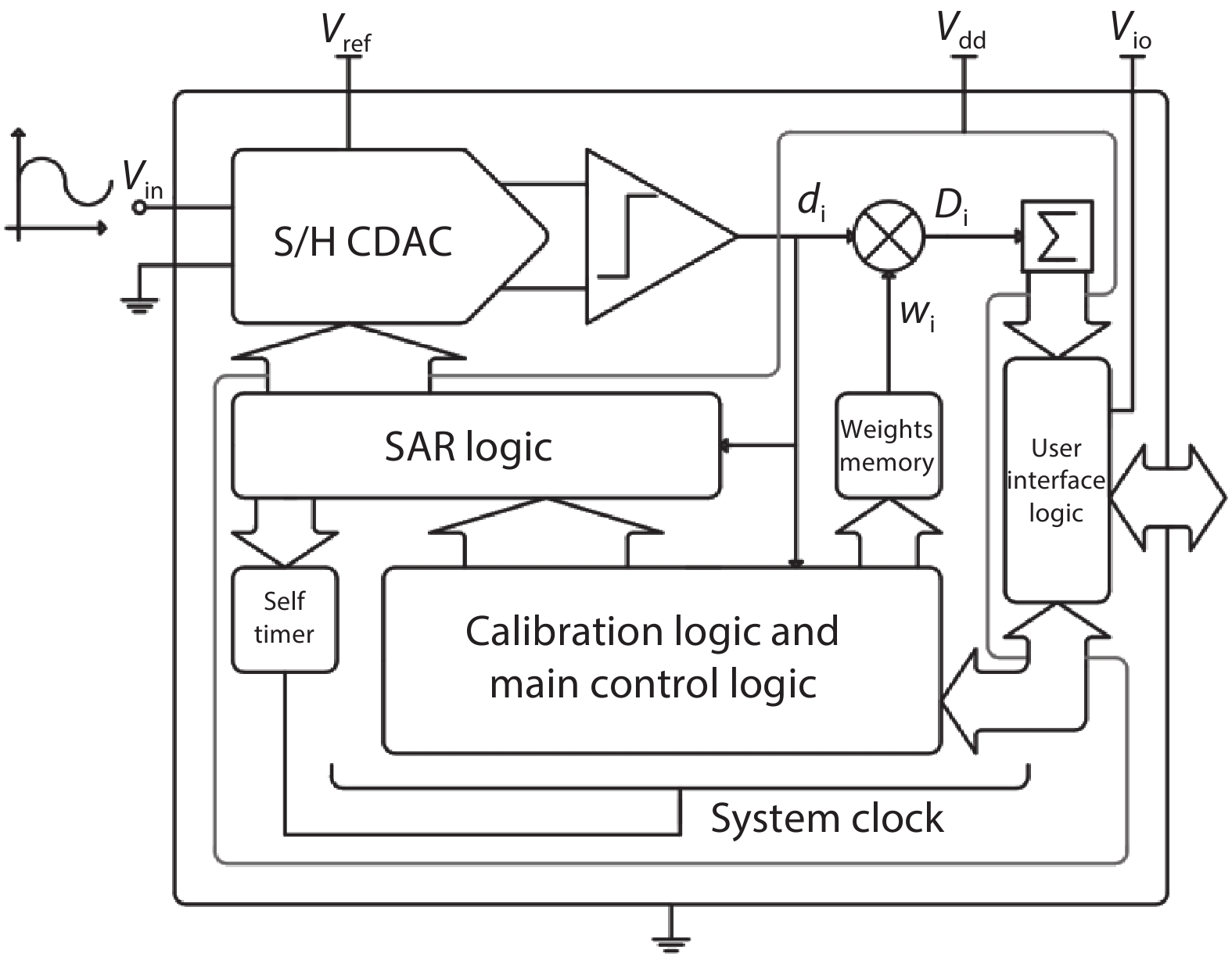

[8] J H Shen, A Shikata, L D Fernando et al. A 16-bit 16-MS/s SAR ADC with on-chip calibration in 55-nm CMOS. IEEE J Solid-State Circuits, 53, 1149(2018).

[9] Y Chen, X Zhu, H Tamura et al. Split capacitor DAC mismatch calibration in successive approximation ADC. IEICE Trans Electron, 93, 295(2010).

[10] J A McNeill, K Y Chan, M C W Coln et al. All-digital background calibration of a successive approximation ADC using the “split ADC” architecture. IEEE Trans Circuits Syst I, 58, 2355(2011).

[11]

[12] J L McCreary, P R Gray. All-MOS charge redistribution analog-to-digital conversion techniques. I. IEEE J Solid-State Circuits, 10, 371(1975).

[13] P J Harpe, C Zhou, Y Bi et al. A 26 W 8 bit 10 MS/s asynchronous SAR ADC for low energy radios. IEEE J Solid-State Circuits, 46, 1585(2011).

[14]

[15] C C Liu, S J Chang, G Y Huang et al. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J Solid-State Circuits, 45, 731(2010).

[16] P Harpe, Y Zhang, G Dolmans et al. A 7-to-10b 0-to-4MS/s flexible SAR ADC with 6.5-to-16fJ/conversion-step. 2012 IEEE International Solid-State Circuits Conference, 472(2012).

[17] M J Seo, Y J Roh, D J Chang et al. A reusable code-based SAR ADC design with CDAC compiler and synthesizable analog building blocks. IEEE Trans Circuits Syst II, 65, 1904(2018).

[18]

[19] T Miki, T Morie, K Matsukawa et al. A 4.2 mW 50 MS/s 13 bit CMOS SAR ADC With SNR and SFDR enhancement techniques. IEEE J Solid-State Circuits, 50, 1372(2015).

[20] C P Hurrell, C Lyden, D Laing et al. An 18 b 12.5 MS/s ADC with 93 dB SNR. IEEE J Solid-State Circuits, 45, 2647(2010).

[21] M F Wagdy, M Goff. Linearizing average transfer characteristics of ideal ADC's via analog and digital dither. IEEE Trans Instrum Meas, 43, 146(1994).

[22]

[23]

[24] M Maddox, B Z Chen, M Coln et al. A 16 bit linear passive-charge-sharing SAR ADC in 55nm CMOS. 2016 IEEE Asian Solid-State Circuits Conf (A-SSCC), 153(2016).