[1] H Inose, H Inose, Y Yasuda et al. A telemetering system by code modulation — Δ–Σ modulation. IRE Trans Space Electron Telemetry, 8, 204(1962).

[2] G R Ritchie, J Candy, W Ninke. Interpolative digital to analog converters. IEEE Trans Commun, 22, 1797(1974).

[3] J C Candy. A use of limit cycle oscillations to obtain robust analog-to-digital converters. IEEE Trans Commun, 22, 298(1974).

[4] J C Candy, B Wooley, O Benjamin. A voiceband codec with digital filtering. IEEE Trans Commun, 29, 815(1981).

[5] J C Candy, O J Benjamin. The structure of quantization noise from sigma-delta modulation. IEEE Trans Commun, 29, 1316(1981).

[6] J C Candy. A use of double integration in sigma-delta modulations. IEEE Trans Commun, 33, 249(1985).

[7] J C Candy, A Huynh. Double Interpolation for digital-to-analog conversion. IEEE Trans Commun, 34, 77(1986).

[8] T Hayashi, e Y Inabe, K Uchimura et al. A multistage delta-sigma modulator without double integration loop. ISSCC Digest of Technical Papers, 182(1986).

[9] J Q Chen, J Y Ren, J Xun et al. An 80 dB dynamic range modulator for a GSM system. Chin J Semicond, 28, 294(2007).

[10] Y Cao, T L Ren, Z L Hong et al. A 16 bit 96 kHz chopper-stabilized sigma-delta ADC. Chin J Semicond, 28, 1204(2007).

[11] J Yuan, Z F Zhang, J Wu et al. Continuous time sigma delta ADC design and non-idealities analysis. J Semicond, 32, 125007(2011).

[12] R Li, J Li, T Yi et al. A 18-mW, 20-MHz bandwidth, 12-bit continuous-time modulator using a power-efficient multi-stage amplifier. J Semicond, 33, 015007(2012).

[13] T C Caldwell, D A Johns. An 8-th order MASH delta-sigma with an OSR of 3. ESSCIRC, 476(2009).

[14] J S Chiang, H L Chen, P C Chou. A 2.5-V 14-bit MASH sigma-delta modulator for ADSL. IEEE Asia-Pacific Conference on Advanced System Integrated Circuits, 24(2004).

[15]

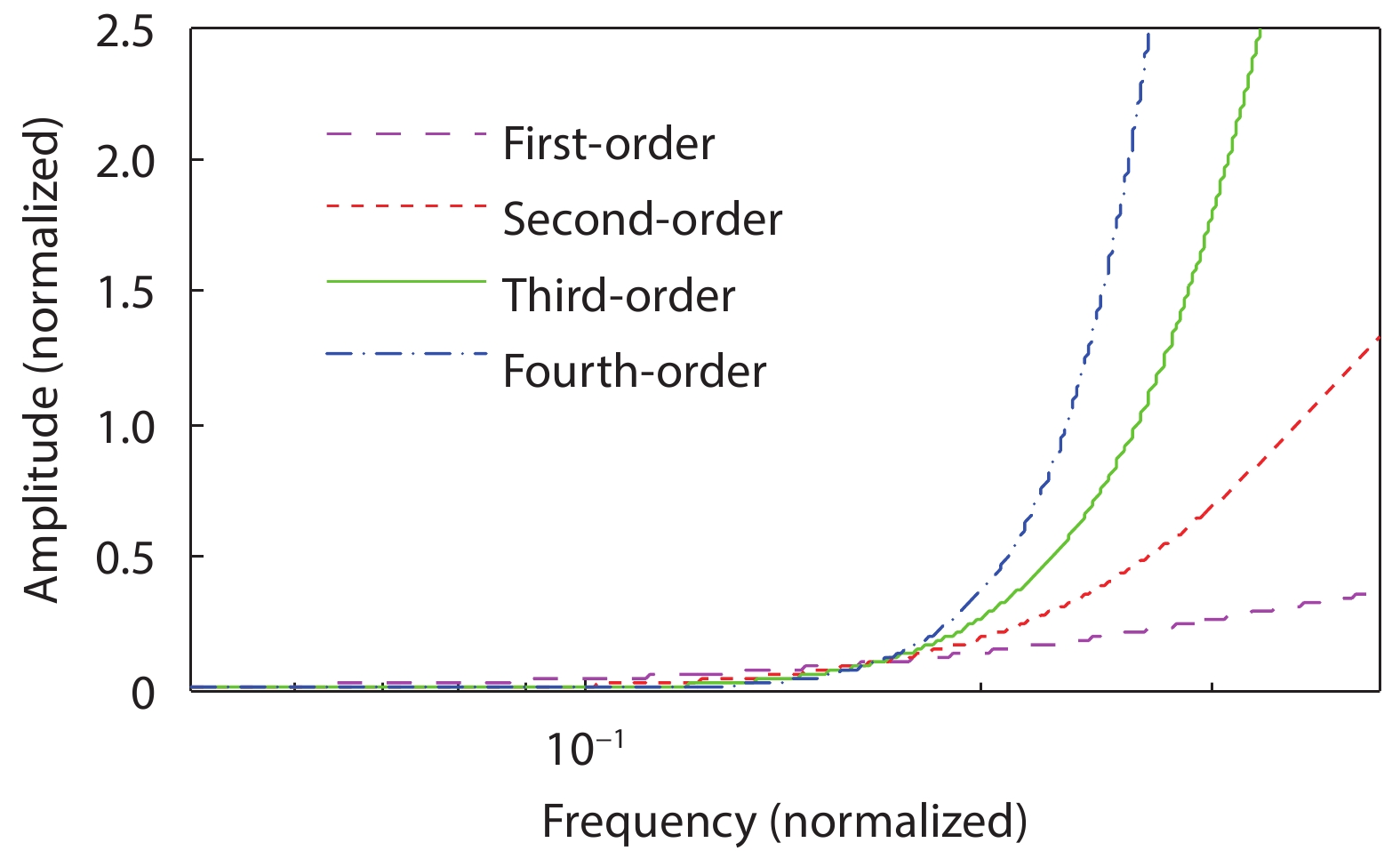

[16] K C Chao, S Nadeem, W L Lee et al. A higher order topology for interpolative modulators for oversampling A/D converters. IEEE Trans Circuits Syst, 37, 309(1990).

[17]

[18] F Wang, R Harjani. Power analysis and optimal design of opamps for oversampled converters. IEEE Trans Circuits Syst II, 46, 359(1999).

[19] F Medeiro, B Pérez-Verdú, la Rosa J M de et al. Fourth-order cascade SC sigma delta modulator: a comparative study. IEEE Trans Circuits Syst I, 45, 1041(1998).

[20]

[21]

[22] P Balmelli, Q Huang. A 25 MS/s 14 b 200 mW Σ∆ modulator in 0.18

[23] S Brigati, i F Francesconi, P Malcovati et al. A Fourth-order singla-bit switched capacitor sigma delta modulator for distributed sensor applications. IEEE Trans Instrum Meas, 53, 266(2004).

[24] A Gerosa, A Neviani. A 1.8

[25] L Yao, M Steyaert, W Sansen. A 1-V, 1 MS/s, 88-dB sigma delta modulator in 0.13-

[26]