Guiping Cao, Ning Dong. An 18-bit sigma –delta switched-capacitor modulator using 4-order single-loop CIFB architecture[J]. Journal of Semiconductors, 2020, 41(6): 062404

Search by keywords or author

- Journal of Semiconductors

- Vol. 41, Issue 6, 062404 (2020)

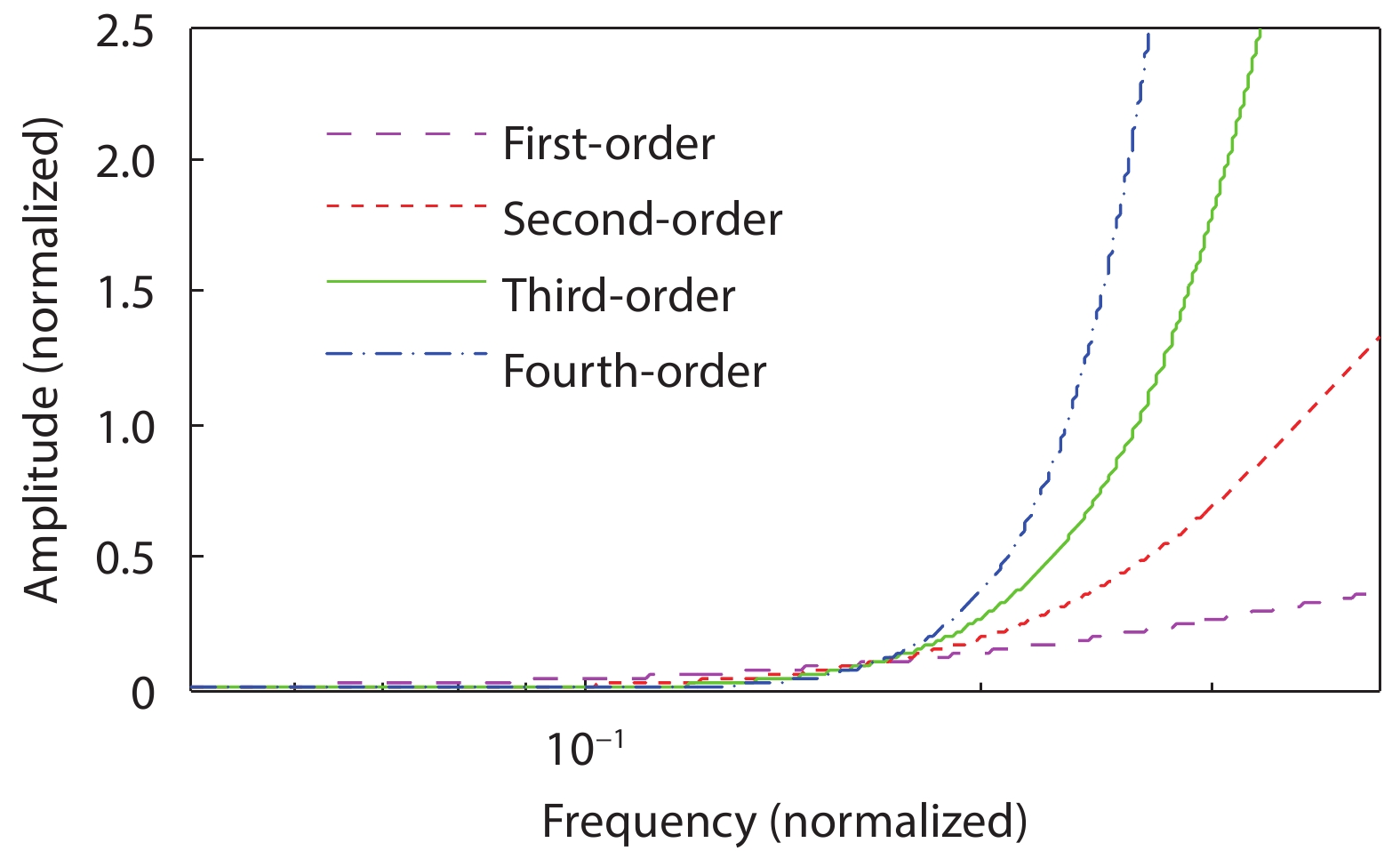

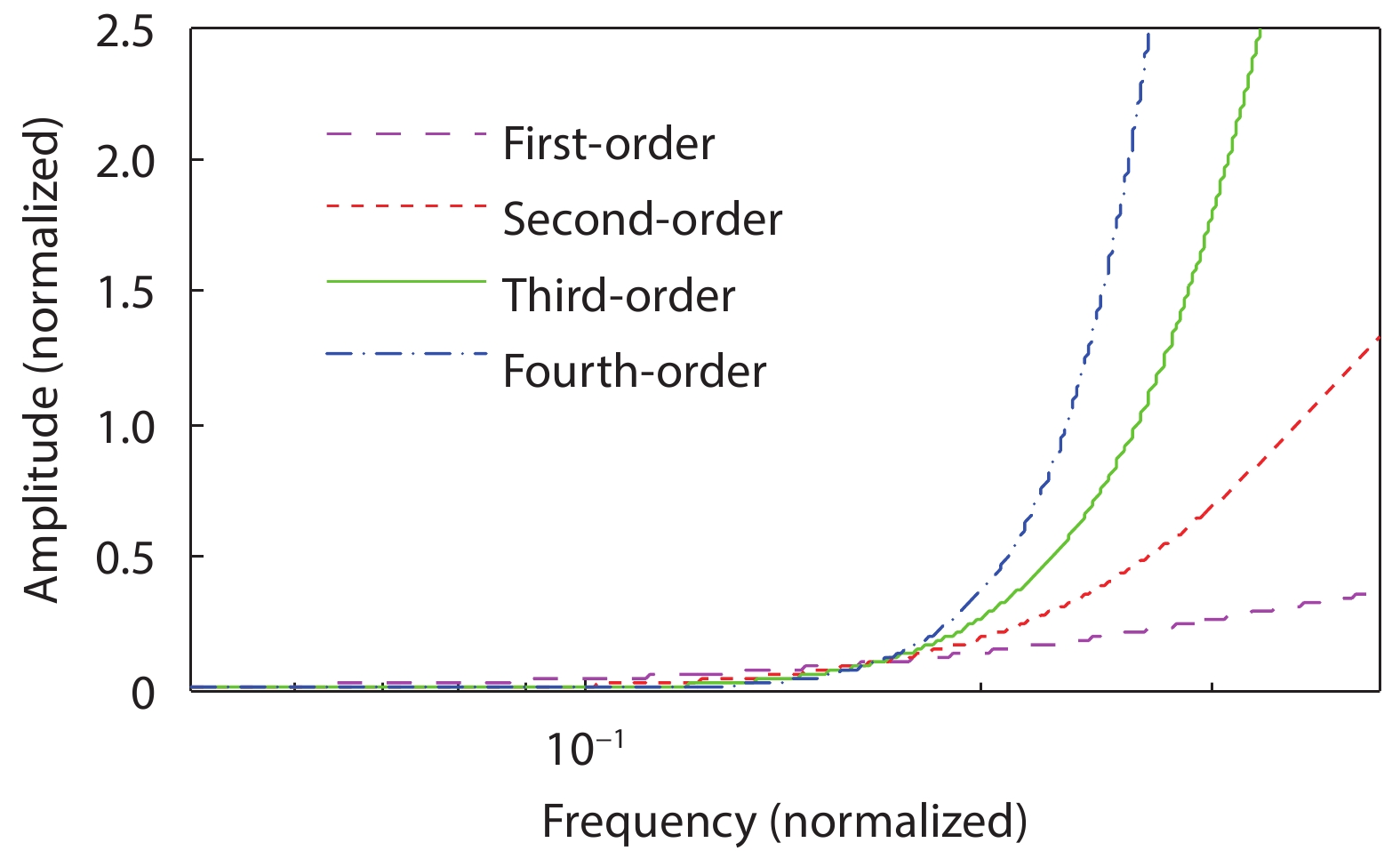

Fig. 1. (Color online) Noise modulation under different modulation orders.

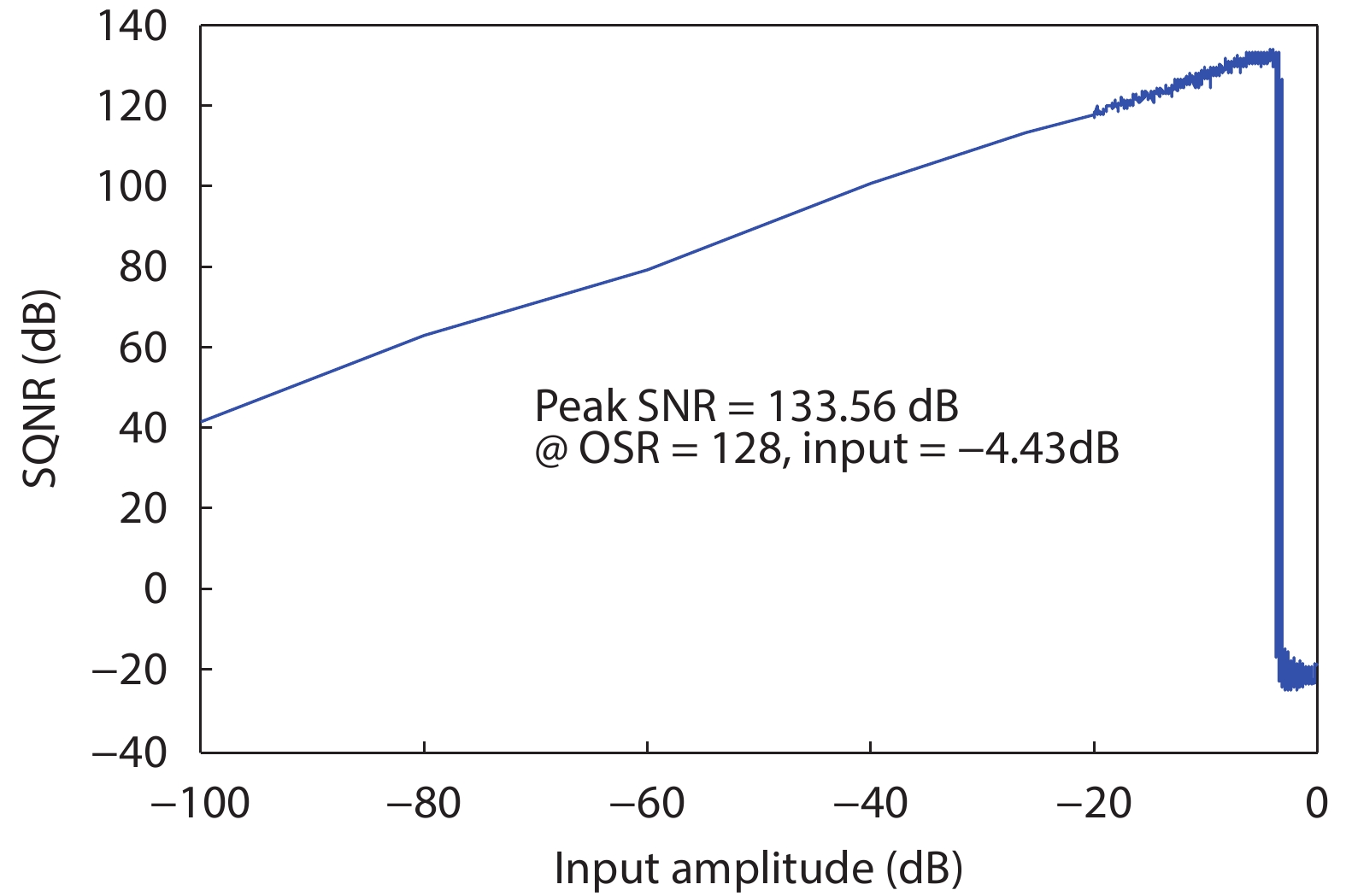

Fig. 2. (Color online) Relationship of the SQNR with input signal amplitude.

Fig. 3. 4-order single-loop CIFB structure.

Fig. 4. NTF/SFT transfer functions after mapping to CIFB structure.

Fig. 5. (Color online) Simulated SQNR under –6 dB input after mapping to CIFB structure.

Fig. 6. SC implementation of the CIFB structure modulator.

Fig. 7. Bandgap reference circuit.

Fig. 8. Simulated results (bandgap voltage fluctuation with power supply and temperature).

Fig. 9. OTA circuit.

Fig. 10. (Color online) Frequency Response of the designed OTA.

Fig. 11. Clocks used in the modulator.

Fig. 12. Clock generator circuit.

Fig. 13. Simulation results of clock generator.

Fig. 14. Comparator and Latch incorporating a hysteresis.

Fig. 15. (Color online) Σ–Δ modulator layout.

Fig. 16. Σ–Δ modulator (SDM) layout architecture and chip after manufacturing.

Fig. 17. (Color online) Test bench for the designed Σ–Δ modulator.

Fig. 18. (Color online) Modulated bit stream output of the designed Σ–Δ modulator.

Fig. 19. (Color online) Raw bit stream performance comparison of the designed chip with the industrial chip (CS5372).

Fig. 20. (Color online) Performance comparison after digital filtering of the designed chip with the industrial chip (CS5372).

|

Table 1. CIFB parameters calculated from NTF.

|

Table 2. Simulation results of OTA.

|

Table 3. Performance comparison between the designed chip and the industrial chip (CS5372).

|

Table 4. Performance comparison of the Σ–Δ modulators.

Set citation alerts for the article

Please enter your email address