Tongtong Yang, Yan Wang, Ruifeng Yue. Demonstration of 4H-SiC CMOS digital IC gates based on the mainstream 6-inch wafer processing technique[J]. Journal of Semiconductors, 2022, 43(8): 082801

Search by keywords or author

- Journal of Semiconductors

- Vol. 43, Issue 8, 082801 (2022)

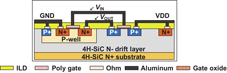

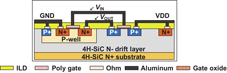

Fig. 1. (Color online) The CMOS circuit configuration that is used in this work

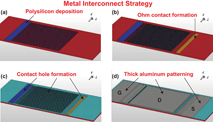

Fig. 2. (Color online) The proposed metal interconnect strategy for fabricating the SiC NMOS and PMOS devices.

Fig. 3. (Color online) The doping profiles of N+, P-well and P+ regions obtained by process simulations through Synopsys Sentaurus.

Fig. 4. (Color online) The fabricated SiC NMOS, PMOS and CMOS gates. (a) PMOS. (b) NMOS. (c) Inverter gate. (d) NAND gate.

Fig. 5. (Color online) The measured transfer characteristics of the PMOS and NMOS.

Fig. 6. (Color online) (a) The typical measured voltage transfer curves and (b) the extracted inverter gain of the fabricated Inverter gate.

Fig. 7. (Color online) The measured switching input-output characteristics of the fabricated SiC Inverter gate.

Fig. 8. (Color online) The measured switching input-output characteristics of the fabricated SiC NAND gate.

|

Table 1. The temperature, dose and energy used in the fabrications for P-well, P+ region and N+ regions.

Set citation alerts for the article

Please enter your email address