[1] G Z Liu. Characterization and modeling of a highly reliable ONO antifuse for high-performance FPGA and PROM. Int J Mater Sci Appl, 5, 169(2016).

[2] T N He, F C Zhang, S Bhunia et al. Silicon carbide (SiC) nanoelectromechanical antifuse for ultralow-power one-time-programmable (OTP) FPGA interconnects. IEEE J Electron Devices Soc, 3, 323(2015).

[3] N Rezzak, D Dsilva, J J Wang et al. SET and SEFI characterization of the 65 nm SmartFusion2 flash-based FPGA under heavy ion irradiation. 2015 IEEE Radiation Effects Data Workshop, 1(2015).

[4] J Zhang, D M Zhou. An 8.5-ps two-stage vernier delay-line loop shrinking time-to-digital converter in 130-nm flash FPGA. IEEE Trans Instrum Meas, 67, 406(2018).

[5] X L Li, Q K Yu, Y Sun et al. The experimental study on SEU hardened effect of flash FPGA for space application. 2018 International Conference on Radiation Effects of Electronic Devices, 1(2018).

[6] S Rezgui, J J Wang, E C Tung et al. New methodologies for SET characterization and mitigation in flash-based FPGAs. IEEE Trans Nucl Sci, 54, 2512(2007).

[7] M Ebrahimi, P M B Rao, R Seyyedi et al. Low-cost multiple bit upset correction in SRAM-based FPGA configuration frames. IEEE Trans Very Large Scale Integr (VLSI) Syst, 24, 932(2016).

[8] C Bernardeschi, L Cassano, A Domenici. SRAM-based FPGA systems for safety-critical applications: A survey on design standards and proposed methodologies. J Comput Sci Technol, 30, 373(2015).

[9] J J Wang, N Rezzak, D Dsilva et al. A novel 65 nm radiation tolerant flash configuration cell used in RTG4 field programmable gate array. IEEE Trans Nucl Sci, 62, 3072(2015).

[10] N Rezzak, J J Wang, D Dsilva et al. TID and SEE characterization of microsemi's 4th generation radiation tolerant RTG4 flash-based FPGA. 2015 IEEE Radiation Effects Data Workshop, 1(2015).

[11]

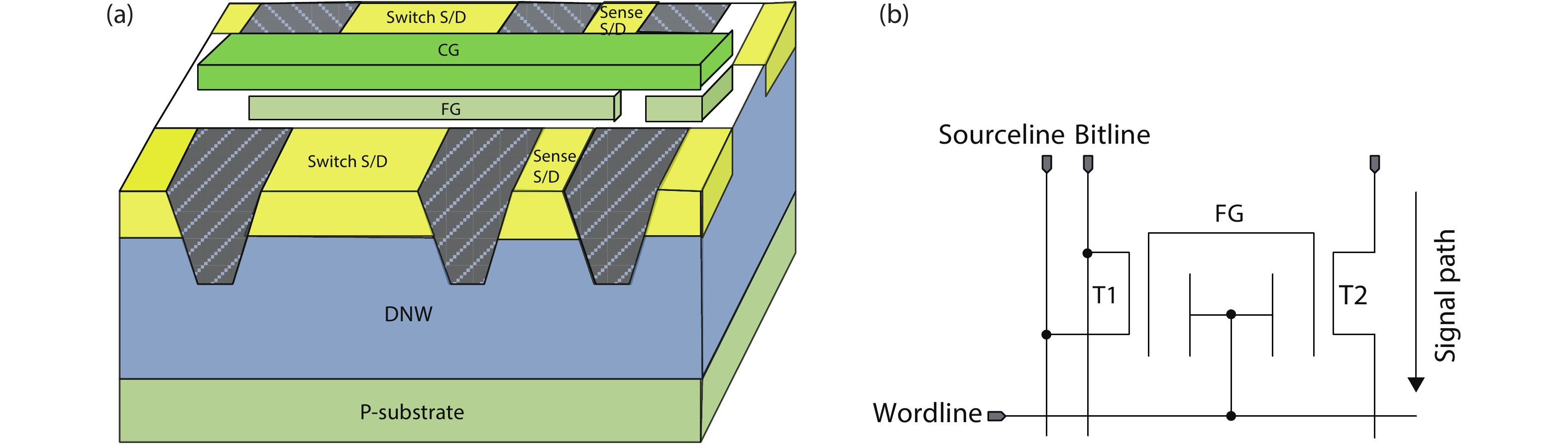

[12] G Z Liu, B Li, J H Wei et al. A radiation-hardened Sense-Switch pFLASH cell for FPGA. Microelectron Reliab, 103, 113514(2019).

[13] G Z Liu, B Li, Z Q Xiao et al. The TID characteristics of a radiation hardened sense-switch pFLASH cell. IEEE Trans Device Mater Reliab, 20, 358(2020).

[14] S Yamada, Y Hiura, T Yamane et al. Degradation mechanism of flash EEPROM programming after program/erase cycles. Proc IEEE Int Electron Devices Meet, 23(1993).

[15] B A Schmid, J Y Jia, J Wolfman et al. Cycling induced degradation of a 65 nm FPGA flash memory switch. IEEE International Integrated Reliability Workshop Final Report, 92(2010).

[16] S S Chung, S N Kuo, C M Yih et al. Performance and reliability evaluations of p-channel flash memories with different programming schemes. Int Electron Devices Meet IEDM Tech Dig, 295(1997).

[17] R E Shiner, J M Caywood, B L Euzent. Data retention in EPROMS. 18th International Reliability Physics Symposium, 238(1980).

[18] S Mori, Y Kaneko, N Arai et al. Reliability study of thin inter-poly dielectrics for non-volatile memory application. 28th Annual Proceedings on Reliability Physics Symposium, 132(1990).