Spins in silicon (Si) quantum dots (QDs), as a new type of solid state qubits, is expected to be a competitive contender in the long run of scalable quantum computation[

- Journal of Semiconductors

- Vol. 41, Issue 7, 070402 (2020)

Abstract

Despite its significant impact on classical computation, silicon is still a new material for quantum computation. As early as the beginning of the 21st century, electron spins in gate defined GaAs/AlGaAs QDs were investigated[

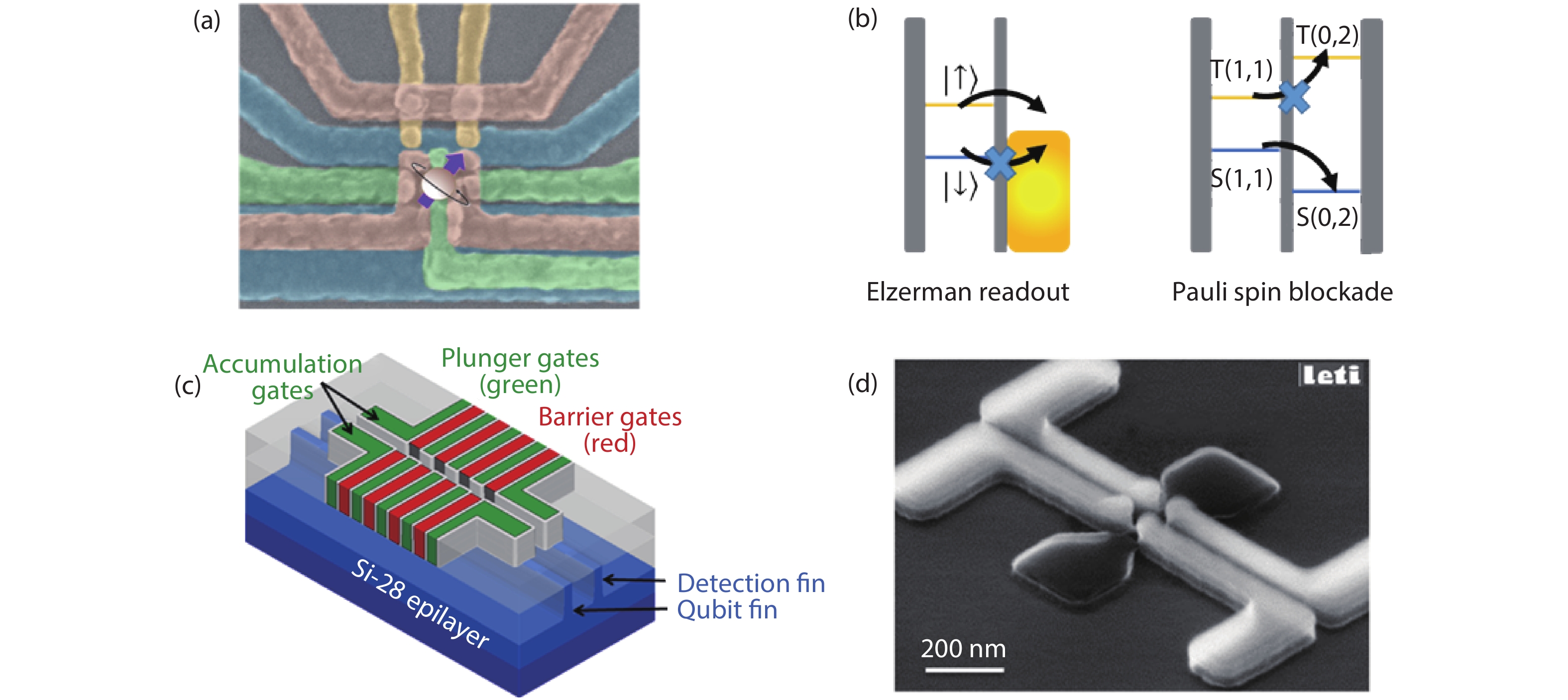

The large effective mass requires tighter electron confinement and decreases the transparency of tunnel barriers, and to tackle this problem, researchers suffered a long time and eventually invented the so-called overlapping gate architecture. As shown in Fig. 1(a), on the surface of a Si/SiGe heterostructure or a Si metal–oxide–semiconductor (MOS), metal electrodes are overlapped with one another to define a QD with a diameter ~ 10–20 nm and achieve full control of the electron occupation in the QD. In this way, the QD could be emptied down to single electron. With an external magnetic field, the degeneracy of spin states could be lifted with a Zeeman energy between spin-up and spin-down. Then a qubit can be defined by these two quantum states. By controlling the tunnel rate between the QD and the reservoir or among two QDs, the electron spin direction can be read out using Elzerman readout method or Pauli spin blockade method (see Fig. 1(b)). When a microwave burst with the qubit frequency is applied to one of the electrodes (with natural or synthetic spin-orbit coupling) or to a stripline antenna, the qubit could be driven coherently to oscillate between spin-up and spin-down. Based on Elzerman readout, several research groups have demonstrated single- and two-qubit quantum gate operations with fidelities over 99.9%[

Apart from the overlapping gate architecture, there are also some foundry based gate structures that are under development. In 2018, Intel Corporation reported a novel dual nested gate integration process for creating Si QDs based on their fin field-effect transistor (FinFET) technology (see Fig. 1(c)). And in 2019, they demonstrated Coulomb blockade in the QD and tunable tunnel coupling between QDs[

Although the control fidelity of spin qubits in Si QDs could be very high, the interaction between spin and valley degree of freedom in Si QDs still distracts the researchers’ attention. In 2013, Andrew S. Dzurak’s group at University of New South Wales first reported spin relaxation “hot spot” in silicon[

In a European quantum technologies roadmap published in 2018[

1) Control of a linear array of spins with high fidelity single- and two-qubit gates;

2) Readout of a linear array of spins with high fidelity and fast speed for feedback control;

3) Control of a scalable two-dimensional array of spins with high fidelity single- and two-qubit gates;

4) Readout of a scalable two-dimensional array of spins with high fidelity and fast speed for feedback control;

5) Demonstration of error correction code based on an array of spin qubits.

References

[1] X Zhang, H O Li, G Cao et al. Semiconductor quantum computation. Natl Sci Rev, 6, 32(2019).

[2] R Hanson, L P Kouwenhoven, J R Petta et al. Spins in few-electron quantum dots. Rev Mod Phys, 79, 1217(2007).

[3] F A Zwanenburg, A S Dzurak, A Morello et al. Silicon quantum electronics. Rev Mod Phys, 85, 961(2013).

[4] J Yoneda, K Takeda, T Otsuka et al. A quantum-dot spin qubit with coherence limited by charge noise and fidelity higher than 99.9%. Nat Nanotechnol, 13, 102(2018).

[5] C H Yang, K W Chan, R Harper et al. Silicon qubit fidelities approaching incoherent noise limits via pulse engineering. Nat Electron, 2, 151(2019).

[6] W Huang, C H Yang, K W Chan et al. Fidelity benchmarks for two-qubit gates in silicon. Nature, 569, 532(2019).

[7] C H Yang, R C C Leon, J C C Hwang et al. Operation of a silicon quantum processor unit cell above one kelvin. Nature, 580, 350(2020).

[8] L Petit, H G J Eenink, M Russ et al. Universal quantum logic in hot silicon qubits. Nature, 580, 355(2020).

[9]

[10]

[11] C H Yang, A Rossi, R Ruskov et al. Spin-valley lifetimes in a silicon quantum dot with tunable valley splitting. Nat Commun, 4, 2069(2013).

[12] E Kawakami, P Scarlino, D R Ward et al. Electrical control of a long-lived spin qubit in a Si/SiGe quantum dot. Nat Nanotechnol, 9, 666(2014).

[13] X Zhang, R Z Hu, H O Li et al. Giant anisotropy of spin relaxation and spin-valley mixing in a silicon quantum dot. Phys Rev Lett, 124, 257701(2020).

[14] A Acín, I Bloch, H Buhrman et al. The quantum technologies roadmap: A European community view. New J Phys, 20, 080201(2018).

Set citation alerts for the article

Please enter your email address