Wenjing Xu, Jie Chen, Zhangqu Kuang, Li Zhou, Ming Chen, Chengbin Zhang. A low-power high-quality CMOS image sensor using 1.5 V 4T pinned photodiode and dual-CDS column-parallel single-slope ADC[J]. Journal of Semiconductors, 2022, 43(8): 082401

Search by keywords or author

- Journal of Semiconductors

- Vol. 43, Issue 8, 082401 (2022)

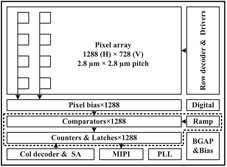

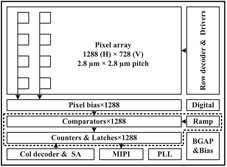

Fig. 1. Block diagram of the overall architecture.

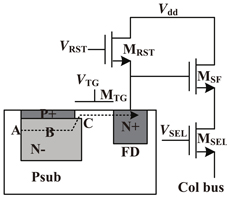

Fig. 2. 4T-PPD architecture.

Fig. 3. (Color online) PPD shape and potential profile: (a) conventional rectangle shaped, (b) proposed five-finger shaped.

Fig. 4. Column circuit of the SS-ADC.

Fig. 5. Timing diagram for dual correlated double sampling.

Fig. 6. Dual-mode counting method: (a) circuit, (b) timing diagram.

Fig. 7. Chip photograph and layout.

Fig. 8. (a) Timing diagram for lag test. (b) Measured lag curves with different shaped PPD.

Fig. 9. Measured photo response curves of five-finger shaped PPD with different transfer gate voltage.

Fig. 10. Measured photon transfer curve.

Fig. 11. Captured image from the fabricated sensor.

Fig. 12. (a) Measured Digital codes of the 644th column without dual-mode counting. (b) Measured Digital codes of the 644th column with dual-mode counting.

|

Table 0. Chip power consumption.

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Table 0. Comparison with other published CIS.

Set citation alerts for the article

Please enter your email address