[1] K Li, P Chen, T Lai et al. Sub-60mV-swing negative-capacitance FinFET without hysteresis. IEEE International Electron Devices Meeting (IEDM), 22(2015).

[2] C Lin, A I Khan, S Salahuddin et al. Effects of the variation of ferroelectric properties on negative capacitance FET characteristics. IEEE Trans Electron Devices, 63, 21972199(2016).

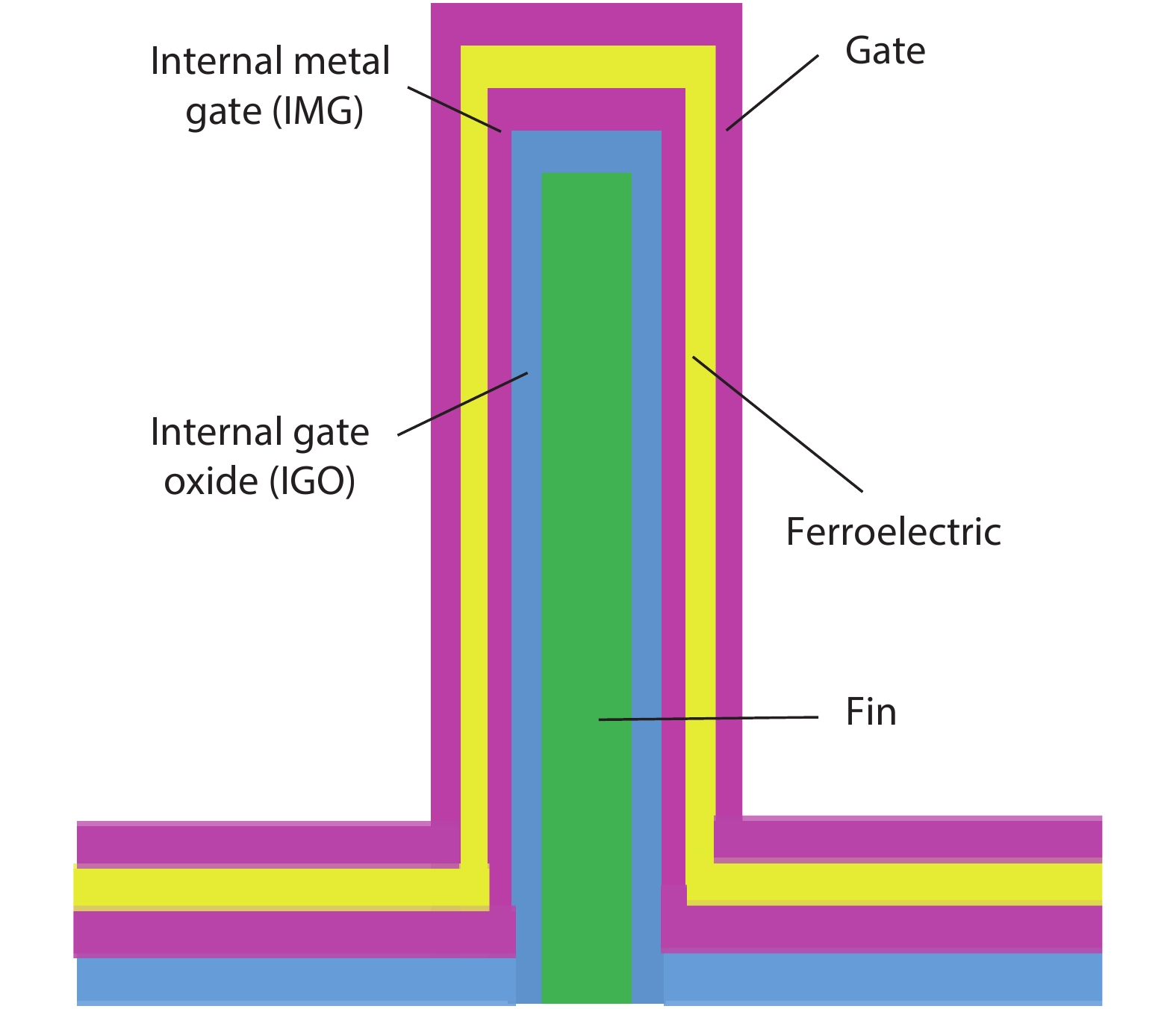

[3] S Khandelwal, A I Khan, J P Duarte et al. Circuit performance analysis of negative capacitance FinFETs. IEEE Symposium on VLSI Technology, 1(2016).

[4] E Ko, H Lee, Y Goh et al. Sub-60-mV/decade negative capacitance FinFET with sub-10-nm hafnium-based ferroelectric capacitor. IEEE J Electron Devices Soc, 5, 306309(2017).

[5] H Ota, K Fukuda, T Ikegami et al. Perspective of negative capacitance FinFETs investigated by transient TCAD simulation. IEEE International Electron Devices Meeting (IEDM), 15(2017).

[6] S Khandelwal, J P Duarte, A I Khan et al. Impact of parasitic capacitance and ferroelectric parameters on negative capacitance FinFET characteristics. IEEE Electron Device Lett, 38, 142144(2017).

[7] H Banga, D Agarwal. Single bit-line 10T SRAM cell for low power and high SNM. International Conference on Recent Innovations in Signal processing and Embedded Systems (RISE), 433(2017).

[8] G Zhang, Y Li, S F Yu. Techniques to improve read noise margin and write margin for bit-cell of 14 nm FINFET node. China Semiconductor Technology International Conference, 1(2015).

[9] K T Chen, S S Gu, M H Lee. Ferroelectric HfZrO

[10] A Aziz, S Ghos, S Datta et al. Physics-based circuit compatible SPICE model for ferroelectric transistors. IEEE Electron Device Lett, 37, 805808(2016).

[11] V Kumar, R K Shrivatava, M M Padaliya. A temperature compensated read assist for low

[12] Y Li, K Yao, G S Samudra. Delay and power evaluation of negative capacitance ferroelectric MOSFET based on SPICE model. IEEE Trans Electron Devices, 64, 24032408(2017).

[13] T Dutta, G Pahwa, A R Trivedi et al. performance evaluation of 7-nm node negative capacitance FinFET-based SRAM. IEEE Electron Device Lett, 38, 1161(2017).

[14] G Pahwa, T Dutta, A Agarwal et al. Analysis and compact modeling of negative capacitance transistor with high on-current and negative output differential resistance —Part I: model description. IEEE Trans Electron Devices, 63, 4981(2016).

[15] G Pahwa, T Dutta, A Agarwal et al. Analysis and compact modeling of negative capacitance transistor with high on-current and negative output differential resistance—Part II: model validation. IEEE Trans Electron Devices, 63, 4986(2016).

[16] Q Dong, Y N Ma, H Chen et al. A novel method for accurate measurement and decoupling of SRAM standby leakage. IEEE 11th International Conference on Solid-State and Integrated Circuit Technology, 1(2012).

[17] G Prasad, R Kusuma. Statistical (M-C) and static noise margin analysis of the SRAM cells. Students Conference on Engineering and Systems (SCES), 1(2013).