[1] S Salahuddin, S Datta. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett, 8, 405(2008).

[2] A Rusu, G A Salvatore, D Jiménez et al. Metal-ferroelectric-meta-oxide-semiconductor field effect transistor with sub-60mV/decade subthreshold swing and internal voltage amplification. 2010 Int Electron Devices Meet, 16.3.1(2010).

[3] J R Zhou, G Q Han, N Xu et al. Experimental validation of depolarization field produced voltage gains in negative capacitance field-effect transistors. IEEE Trans Electron Devices, 66, 4419(2019).

[4] Q Q Huang, H M Wang, Y Zhao et al. New understanding of negative capacitance devices for low-power logic applications. 2019 China Semiconductor Technology International Conference (CSTIC), 1(2019).

[5] Y J Zhang, H Y Wang, L Zhang et al. Field-effect transistor memories based on ferroelectric polymers. J Semicond, 38, 111001(2017).

[6] H F Xu. Two dimensional analytical model for a negative capacitance double gate tunnel field effect transistor with ferroelectric gate dielectric. J Semicond, 39, 104004(2018).

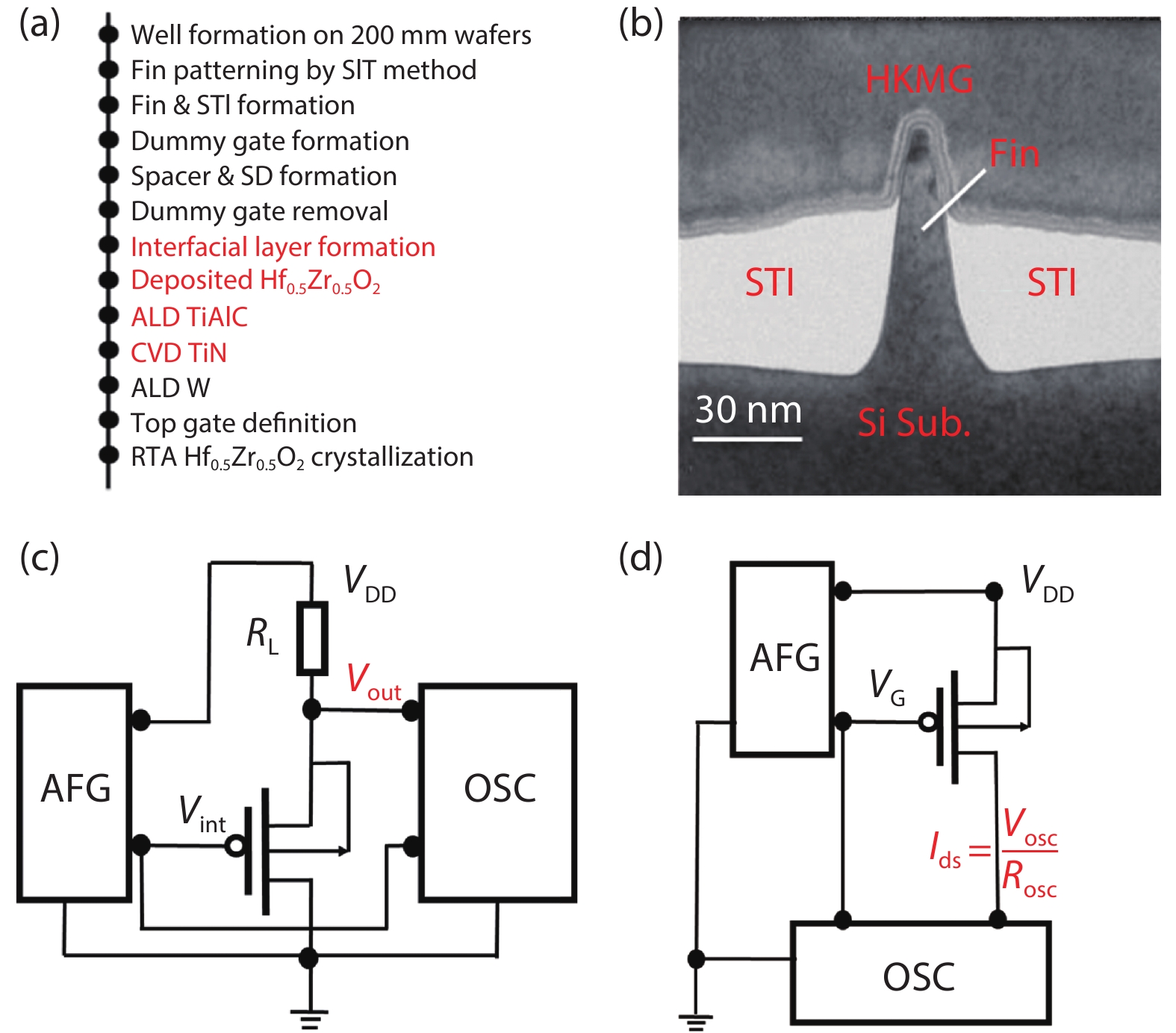

[7] Z H Zhang, G B Xu, Q Z Zhang et al. FinFET with improved subthreshold swing and drain current using 3-nm ferroelectric Hf0.5Zr0.5O2. IEEE Electron Device Lett, 40, 367(2019).

[8] J R Zhou, G Q Han, Q L Li et al. Ferroelectric HfZrO

[9] Y W Cai, Q Z Zhang, Z H Zhang et al. Endurance characteristics of negative capacitance FinFETs with negligible hysteresis. IEEE Electron Device Lett, 42, 260(2021).

[10] Y X Li, R R Liang, J B Wang et al. Negative capacitance oxide thin-film transistor with sub-60 mV/decade subthreshold swing. IEEE Electron Device Lett, 40, 826(2019).

[11] J L Wang, D Wang, Q Li et al. Excellent ferroelectric properties of Hf0.5Zr0.5O2 thin films induced by Al2O3 dielectric layer. IEEE Electron Device Lett, 40, 1937(2019).

[12] J J Liao, B J Zeng, Q Sun et al. Grain size engineering of ferroelectric Zr-doped HfO2 for the highly scaled devices applications. IEEE Electron Device Lett, 40, 1868(2019).

[13] M J Tsai, P J Chen, P Y Peng et al. Atomic-level Analysis by synchrotron radiation and characterization of 2 nm, 3 nm, and 5 nm-thick Hf0.5Zr0.5O2 negative capacitance FinFET. 2019 Silicon Nanoelectronics Workshop (SNW), 1(2019).

[14] E J Nowak, I Aller, T Ludwig et al. Turning silicon on its edge [double gate CMOS/FinFET technology]. IEEE Circuits Devices Mag, 20, 20(2004).

[15] D Suh, J G Fossum. A physical charge-based model for non-fully depleted SOI MOSFET's and its use in assessing floating-body effects in SOI CMOS circuits. IEEE Trans Electron Devices, 42, 728(1995).

[16]

[17] K Chatterjee, A J Rosner, S Salahuddin. Intrinsic speed limit of negative capacitance transistors. IEEE Electron Device Lett, 38, 1328(2017).

[18] D Kwon, Y H Liao, Y K Lin et al. Response speed of negative capacitance FinFETs. 2018 IEEE Symposium on VLSI Technology, 49(2018).

[19] Z Krivokapic, U Rana, R Galatage et al. 14 nm Ferroelectric FinFET technology with steep subthreshold slope for ultra low power applications. 2017 IEEE Int Electron Devices Meet IEDM, 15.1.1(2017).

[20] K S Li, Y J Wei, Y J Chen et al. Negative-capacitance FinFET inverter, ring oscillator, SRAM cell, and

[21] M Kobayashi, N Ueyama, K Jang et al. Experimental study on polarization-limited operation speed of negative capacitance FET with ferroelectric HfO2. 2016 IEEE Int Electron Devices Meet IEDM, 12.3.1(2016).

[22] Z Yuan, S Rizwan, M Wong et al. Switching-speed limitations of ferroelectric negative-capacitance FETs. IEEE Trans Electron Devices, 63, 4046(2016).

[23] J R Zhou, J B Wu, G Q Han et al. Frequency dependence of performance in Ge negative capacitance PFETs achieving sub-30 mV/decade swing and 110 mV hysteresis at MHz. 2017 IEEE Int Electron Devices Meet IEDM, 15.5.1(2017).

[24]

[25]

[26]

[27] X Yu, B Chen, R Cheng et al. Fast-trap characterization in Ge CMOS using sub-1 ns ultra-fast measurement system. 2016 IEEE International Electron Devices Meeting (IEDM), 31.3.1(2016).

[28] J C Wong, S Salahuddin. Negative capacitance transistors. Proc IEEE, 107, 49(2019).