Shizhe Wei, Haifeng Wu, Qian Lin, Mingzhe Zhang. A 0.1–1.5 GHz multi-octave quadruple-stacked CMOS power amplifier[J]. Journal of Semiconductors, 2020, 41(6): 062401

Search by keywords or author

- Journal of Semiconductors

- Vol. 41, Issue 6, 062401 (2020)

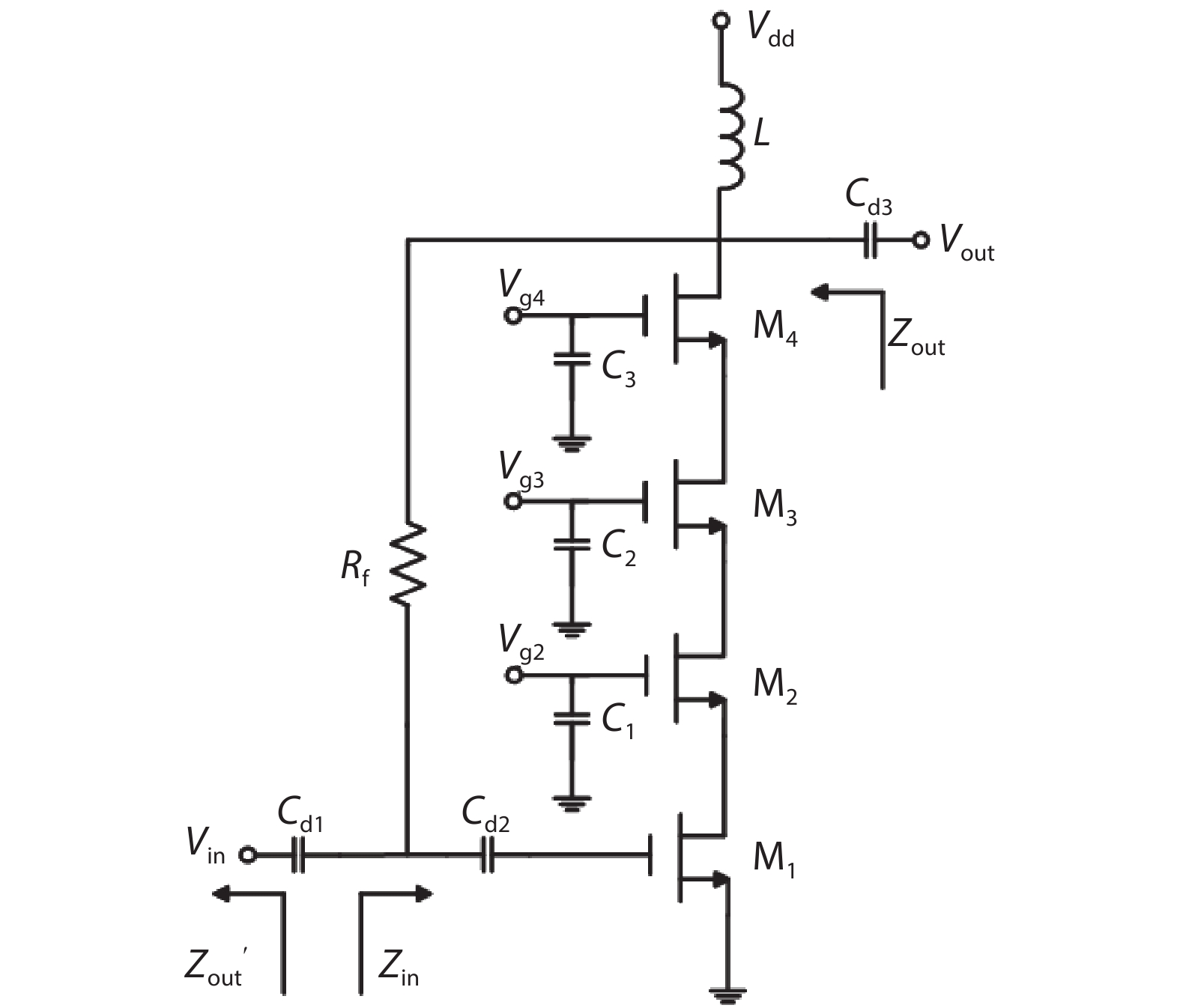

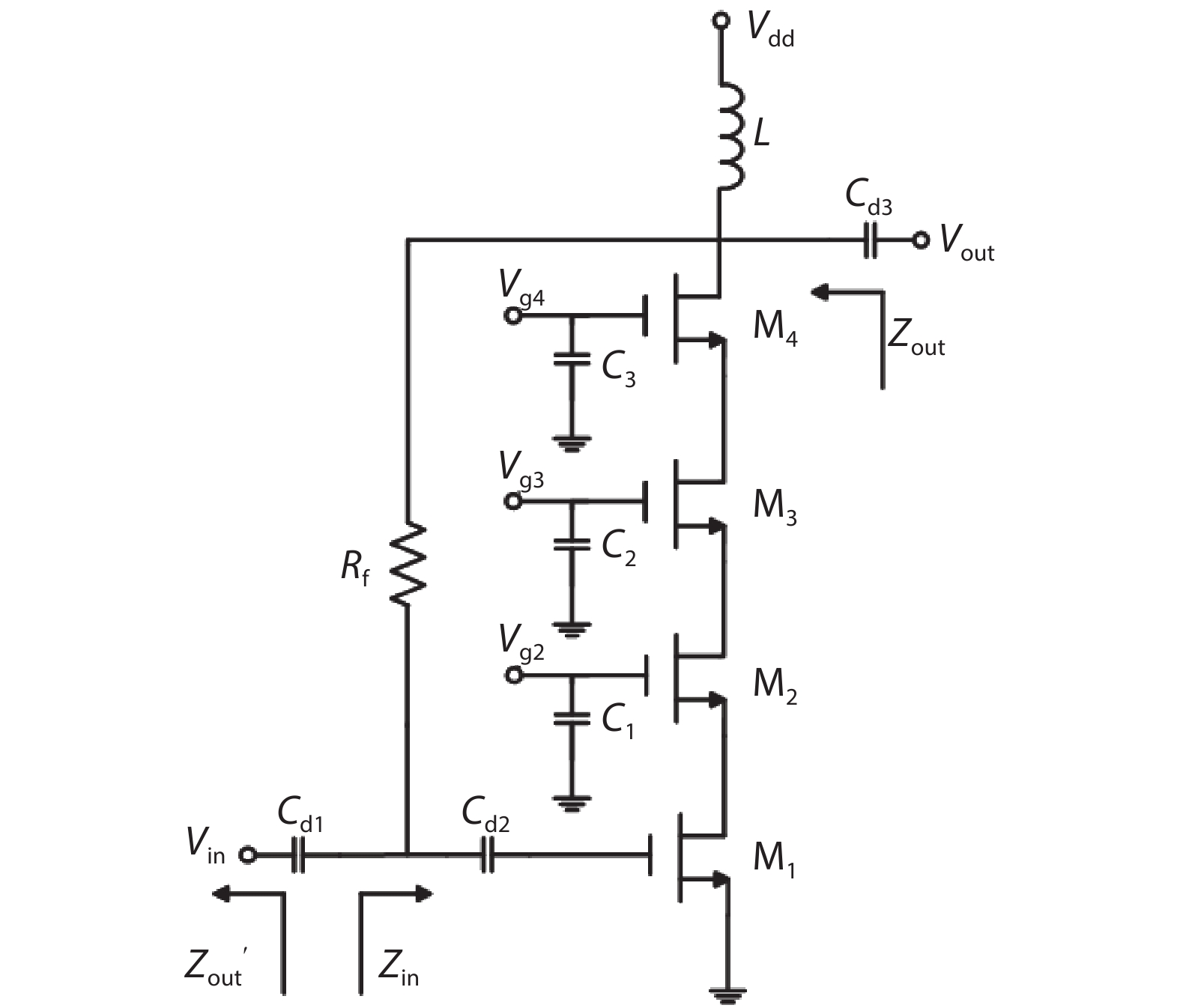

Fig. 1. The equivalent AC circuit.

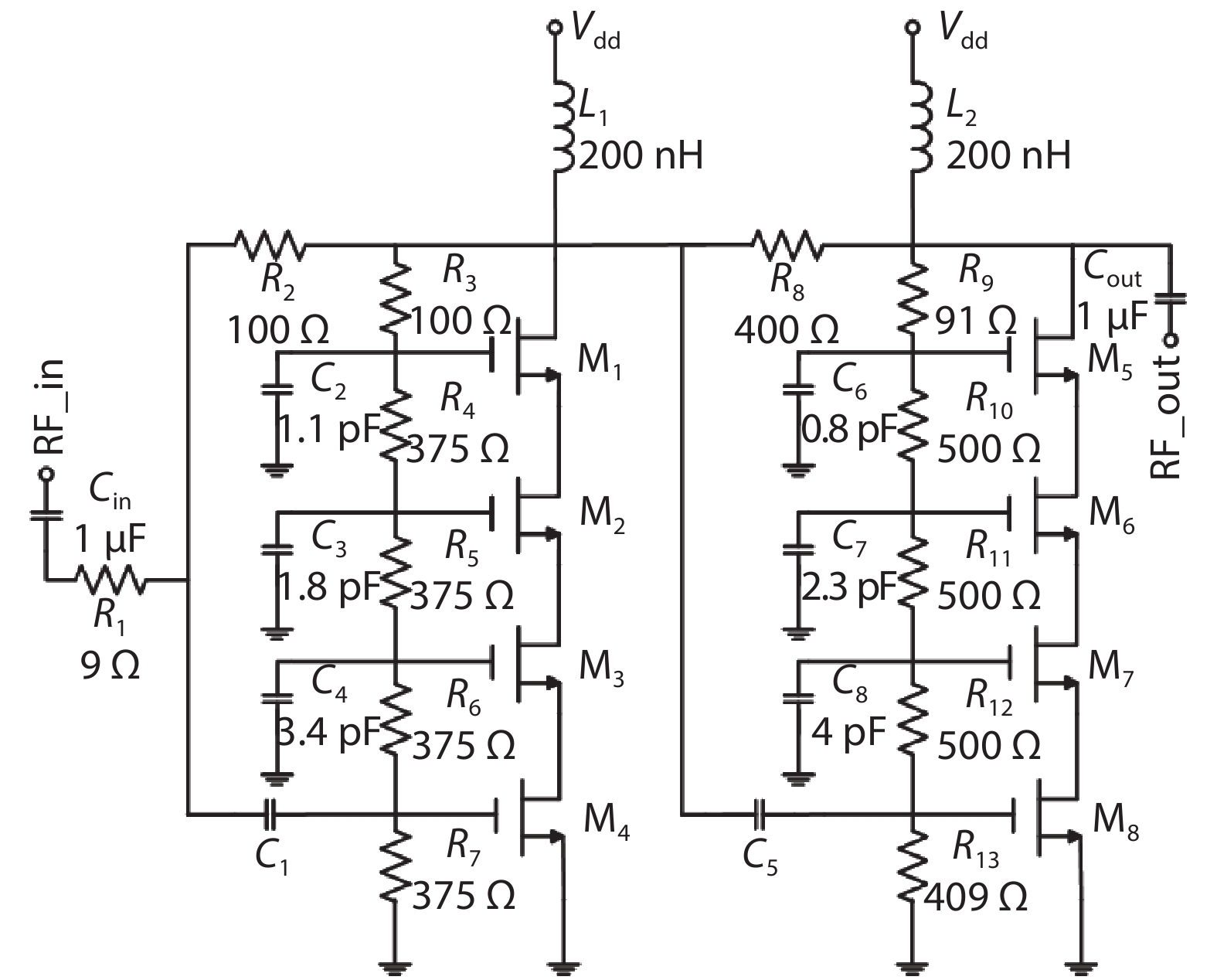

Fig. 2. Schematic of proposed PA.

Fig. 3. (Color online) Effects of R 2S -parameter. (a) S 11. (b) S 21. (c) S 22.

Fig. 4. (Color online) Effects of R 2 on output power and PAE (post-layout simulation). (a) Output power. (b) PAE

Fig. 5. (Color online) Microphotograph of the stacked PA.

Fig. 6. (Color online) Photograph of the test system.

Fig. 7. (Color online) K -factor and S -parameters.

Fig. 8. (Color online) Output power and PAE.

|

Table 1. Performance of Broadband CMOS PAs.

|

Table 2. Power consumption of each stage.

Set citation alerts for the article

Please enter your email address