- Journal of Semiconductors

- Vol. 41, Issue 6, 062401 (2020)

Abstract

1. Introduction

Modern wireless communication systems working in 0.1–1.5 GHz have recently been developed, such as industrial scientific and medical (ISM), enterprise network, space and so on, which results in the desirability of a single chip CMOS transceiver to urgently reduce the overall cost. As a key component in the RF transceiver, there are still many challenges for the CMOS power amplifier (PA) design, which are mainly caused by the low breakdown voltage and lossy on-chip passive elements[

In the ultra-broadband PA design, the common problem is that the optimum impedance varies as the frequency changes[

To solve these problems, stacked power amplifiers have become a popular choice in recent years. The transistors involved in this structure have the same current and superimposed voltage, and increasing the output voltage swing. The structure also enlarges the output impedance, which makes the broadband output matching easier. However, the input impedance remains nearly constant and requires additional matching[

In this letter, a two-stage ultra-wideband stacked-FET PA in GLOBALFOUNDRIES 0.18-μm CMOS technology has been designed with a small chip dimension. Over 0.1 to 1.5 GHz, the saturated output power (Psat) is about 22 dBm. Up to 20% PAE is acquired and the input VSWR is below 2 : 1.

2. Circuit design

2.1. The biasing condition of FETs

The biasing condition of FETs is one of the top priorities in circuit design. As the transistor and the working condition are determined, especially for the case of saturation condition, the drain current simply depends on the Vgs, when Vds > Vsat is satisfied.

The optimum load impedance Zopt of the transistor is limited by the biasing condition. For the whole N-stacked FETs structure, the total optimal load impedance of the structure is N × Zopt. This means that we can control the optimum load impedance by adjusting the drain bias voltage. For the quadruple-stacked structure in this letter, to connect 50 Ω load directly without matching network, the total optimal load impedance of the second stage should be set at 12.5 Ω (4 × 12.5 = 50 Ω).

2.2. The impact of feedback resistor on input and output impedance

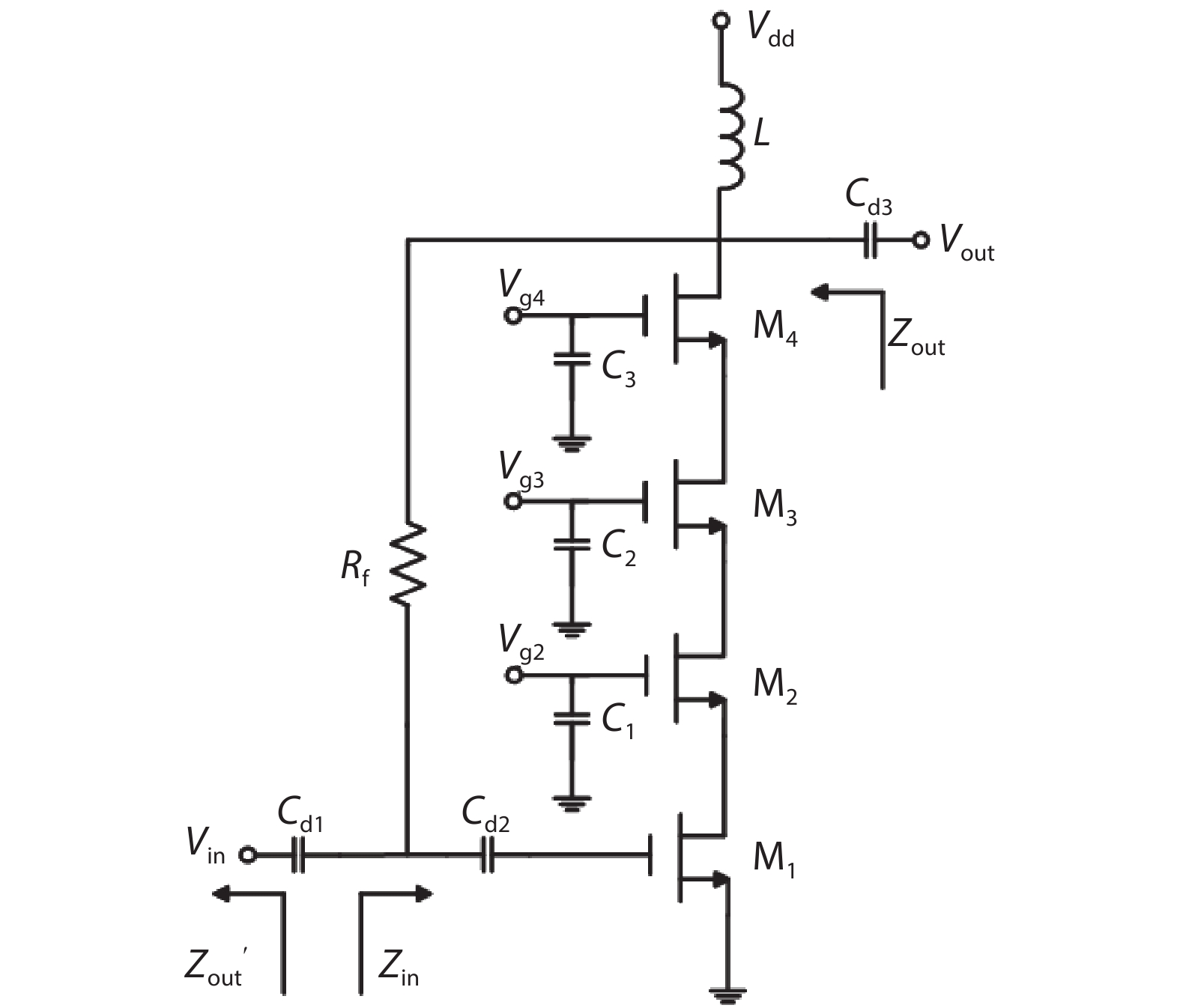

Fig. 1 shows an equivalent AC circuit model of a quadruple-stacked power amplifier. The structure mainly consists of four transistors (M1, M2, M3, M4) and capacitance C1, C2, C3. Cd1, Cd2, Cd3 are DC blocking capacitors, and Rf is a feedback resistor connected between the gate of M1 and the drain of M4.

![]()

Figure 1.The equivalent AC circuit.

As shown in Fig. 1, the transconductance gmstack of the stacked PA can be derived as[

Based on Refs. [14, 15], the closed-loop voltage gain Av of the resistive negative feedback circuit can be derived as:

where ZL is the 50 Ω output load impedance of the PA. The input impedance Zin combined with the negative feedback structure can be derived based on Eq. (2).

where Cgs1 is the gate-to-source capacitance, and the output impedance Zout of the PA is:

Therefore, based on Eqs. (3) and (4), the feedback resistor affects the input and output impedance, by optimizing the feedback resistor Rf, the input and output impedance can be set at a value approached to 50 Ω in the specific frequency band.

2.3. The quadruple-stacked structure

The circuit topology in this design is shown in Fig. 2, and the power stage is made up of transistor M5, M6, M7 and M8, which is connected in series. To enhance the output power, a larger voltage swing is acquired, and thus a two-stage quadruple-stacked FETs structure is employed. The drain current is the same through each transistor, and the total drain bias voltage is superimposed. The gate bias voltage for each layer is obtained by dividing the supply voltage through resistors R9, R10, R11, R12 and R13. It is worth noting that a larger magnitude of impedance needs to be selected for the divider resistance to reduce the quiescent current and power consumption. To adjust the drain output impedance and signal of each layer, the grid voltage of the transistor in each layer is connected to a ground capacitor, forming an AC voltage divider structure with the gate-source capacitor. A feedback resistor R8 is added to improve circuit stability. C5 is used as DC-block between the two stages. The driver stage and power stage are set to be same structure. The input matching network consists of resistors R1, R2 and capacitance C1, which aims to improve the stability and ensure the gain flatness of the circuit. Eight transistors are required in the circuit, M1–M8 are thick gate transistor. The width/length of M1–M2 is 1200 μm/0.35 μm, and the width/length of M3–M8 is 1600 μm/0.35 μm.

![]()

Figure 2.Schematic of proposed PA.

Moreover, the impedance for each transistor is affected by the phase-adjusting capacitances (C2–C4, C6–C8) and gate-to-source capacitance (Cgs) of each FET simultaneously. The key factor to build a 50 Ω stacked FETs is to realize the same transistor size, the same gate to source bias controlled by the voltage-dividing resistors, the same phase of RF voltage controlled by the phase-adjusting capacitances. In consideration of the potentially instability with lower drain voltage, the resistors in the circuit should be optimized to ensure K-factor greater than 1. The broadband input matching is obviously obtained by the resistor R1, R2 and R8. R1 can improve the matching results but decrease the gain of the circuit. The bandwidth response, input and output return loss, power gain and PAE of the circuit is mainly affected by R2 and R8.

Figs. 3 and 4 show the method of adjusting the value of R2 to balance various indexes. As shown in the figures, when the values of R2 reach 200 Ω, the simulated results of S11, S21 and S22 are better than those in 100 and 300 Ω in 0.1–1.5 GHz. 22.3 dBm output power with 20.8% PAE at 0 dBm input power are acquired in post-layout simulation. Obviously, 200 Ω is the more reasonable value in the topology.

![]()

Figure 3.(Color online) Effects of

![]()

Figure 4.(Color online) Effects of

3. Experimental results

To verify the post-layout simulation results, the PA was fabricated as shown in Fig. 5. The total dimension of the chip is 0.58 × 0.76 mm2 with bond pad. The testing system of the fabricated PA is shown in Fig. 6. Using bias-tees at the drain of two stages to provide the supply voltage. And the chip is tested on a probe station. Through a R&S ZVA40 network analyzer, the data ofS11, S21, S22 is acquired. Measurement of the output power is accomplished by the R&S FSV40 frequency analyzer.

![]()

Figure 5.(Color online) Microphotograph of the stacked PA.

![]()

Figure 6.(Color online) Photograph of the test system.

As shown in Fig. 7, the S scattering parameter and stability factor of the fabricated PA are measured. The minimum value of the measured K-factor is larger than 1, which means global stability of the circuit in the entire bandwidth. In the range of 0.1–1.5 GHz, the measured S11 (< –10.8 dB),S21 (22.3 ± 1.5 dB) and S22 (< –9.6 dB) indicate a feature of wide bandwidth, and shows a good gain flatness.Fig. 8 displays 22 dBm of saturated Pout and 20% peak PAE, respectively.

![]()

Figure 7.(Color online)

![]()

Figure 8.(Color online) Output power and PAE.

A comparison of performance indices reported in the literature with state-of-the-art is given in Table 1.

Compared with Ref. [4] and Ref. [8], the proposed PA shows a lower PAE based on the power consumption of each stage, as shown in the Table 2. The reason is that the first stage of the PA consumes more power than expected, which decreases the efficiency of the circuit.

Nevertheless, his work achieves a good performance in gain and bandwidth with a smaller chip size.

4. Conclusion

In this letter, a novel circuit for a 0.1–1.5 GHz multi-octave PA in a small chip dimension was proposed. The combination of stacked structure and feedback resistors greatly enhance the bandwidth of the circuit. Meanwhile, the dimension of the chip is also decreased by resistive matching networks. Our measurement results show that greater than 22 dBm output power from 0.1 to 1.5 GHz, and 20% peak PAE was realized, a gain flatness of 22.3 ± 1.5 dB was measured. This indicates that the proposed structure is suitable for low-breakdown voltage CMOS process in the ultra-broadband PA.

Acknowledgments

This work was supported by the National Natural Science Foundation of China (No. 61841110) and AoShan Talents Outstanding Scientist Program by Pilot National Laboratory for Marine Science and Technology (Qingdao) (No. 2017ASTCP-OS03).

References

[1] J Jin, J Shi, B L Ai et al. A highly linear power amplifier for WLAN. J Semicond, 37, 025006(2016).

[2] J Gong, W Li, J T Hu et al. An 8–18 GHz power amplifier with novel gain fluctuation compensation technique in 65 nm CMOS. J Semicond, 39, 125008(2018).

[3] J S Park, Y J Wang, S Pellerano et al. A CMOS wideband current-mode digital polar power amplifier with built-in AM–PM distortion self-compensation. IEEE J Solid-State Circuits, 53, 340(2018).

[4] H Wang, s C Sideris, i A Hajimiri et al. A CMOS broadband power amplifier with a transformer-based high-order output matching network. IEEE J Solid-State Circuits, 45, 2709(2018).

[5] J Xia, g X Fang, a S Boumaiza. 60-GHz power amplifier in 45-nm SOI-CMOS using stacked transformer-based parallel power combiner. IEEE Microwave Wireless Compons Lett, 28, 711(2018).

[6] H T Ahn, t D J Allstot. A 0.5–8.5-GHz fully differential CMOS distributed amplifier. IEEE J Solid-State Circuits, 37, 985(2002).

[7]

[8] P C Huang, Z M Tsai, K Y Lin et al. A high-efficiency, broadband CMOS power amplifier for cognitive radio applications. Trans Microwave Theory Tech, 58, 3556(2010).

[9]

[10] H F Wu, X J Liao, Q Lin et al. A compact ultrabroadband stacked traveling-wave GaN on Si power amplifier. IEEE Trans Microwave Theory Tech, 66, 3306(2018).

[11] F Thome, A Leuther, M Schlechtweg et al. Broadband high-power W-band amplifier MMICs based on stacked-HEMT unit cells. Trans Microwave Theory Tech, 66, 1312(2018).

[12] C Wu, Y Lin, o Y Hsiao et al. Design of a 60-GHz high-output power stacked- FET power amplifier using transformer-based voltage-type power combining in 65-nm CMOS. Trans Microwave Theory Tech, 66, 4595(2018).

[13] S Pornpromlikit, J Jeong, C D Presti et al. A Watt-level stacked-FET linear power amplifier in silicon-on-insulator CMOS. IEEE Trans Microwave Theory Tech, 58, 57(2010).

[14]

[15] H T Dabag, B Hanafi, F Golcuk et al. Analysis and design of stacked-FET millimeter-wave power amplifiers. IEEE Trans Microwave Theory Tech, 61, 1543(2013).

Set citation alerts for the article

Please enter your email address