Jianwei Wu, Zongguang Yu, Genshen Hong, Rubin Xie. Design of GGNMOS ESD protection device for radiation-hardened 0.18 μm CMOS process[J]. Journal of Semiconductors, 2020, 41(12): 122403

Search by keywords or author

- Journal of Semiconductors

- Vol. 41, Issue 12, 122403 (2020)

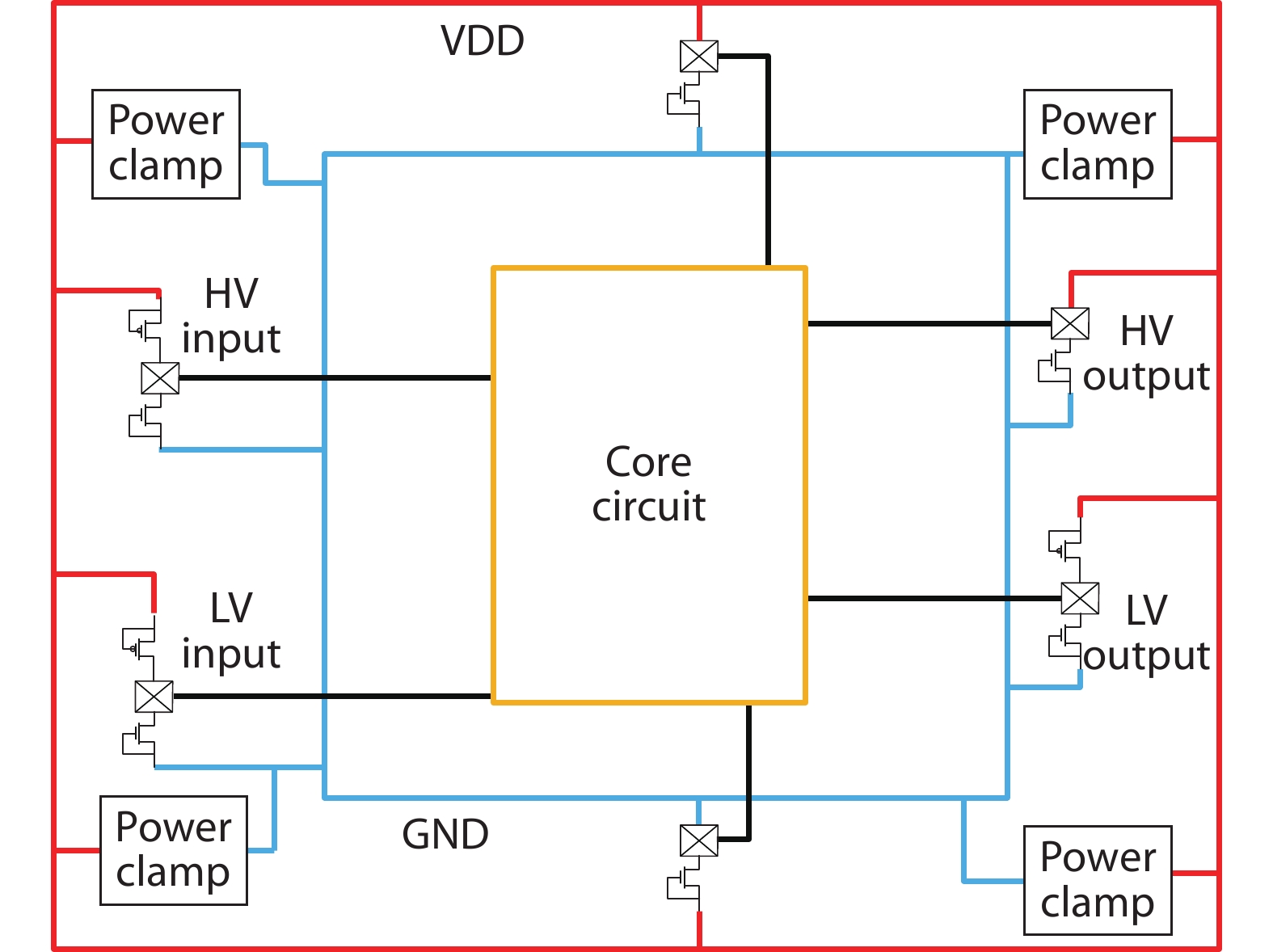

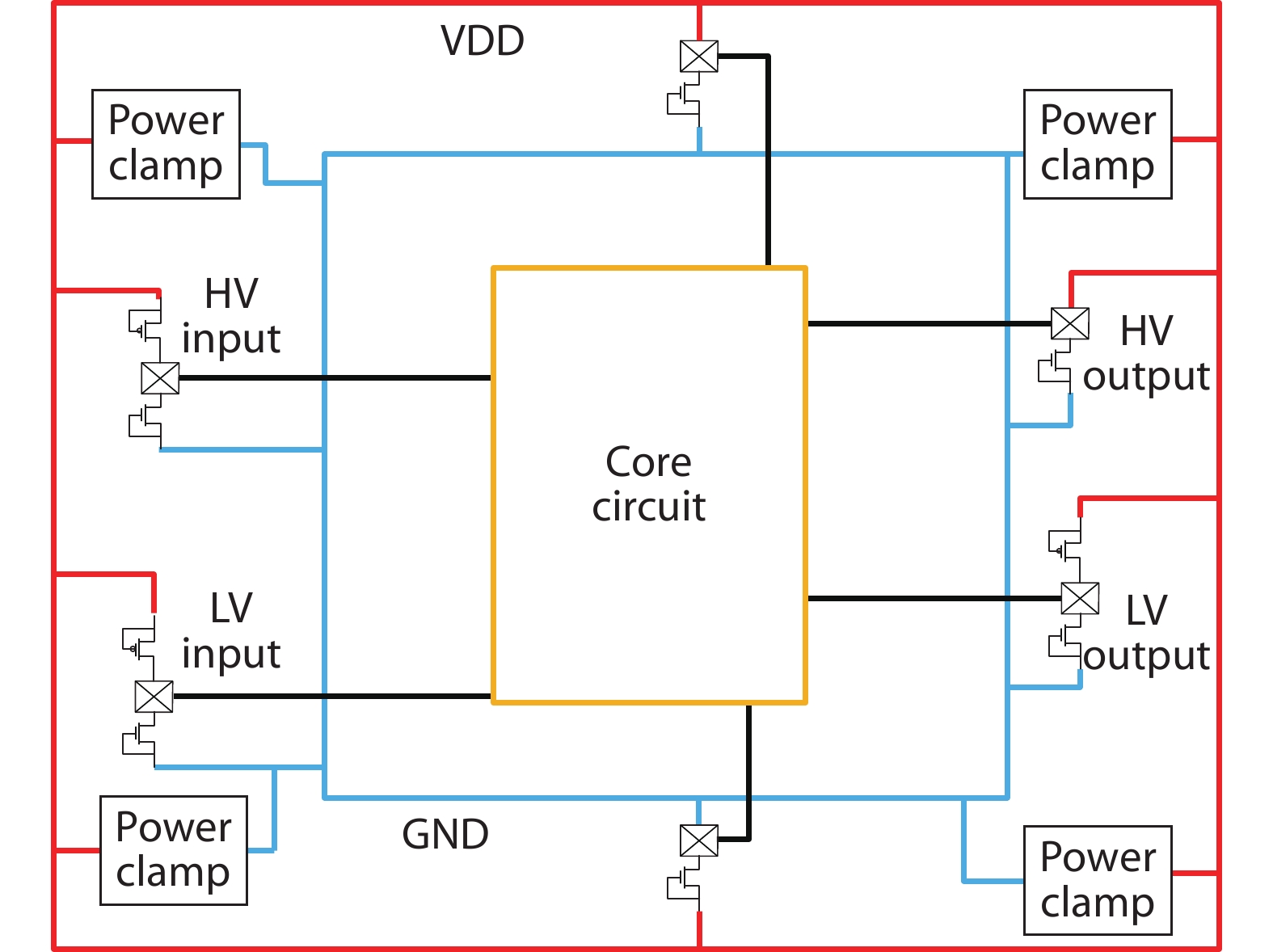

Fig. 1. (Color online) The structure of IC (integrated circuit) chip ESD protection system.

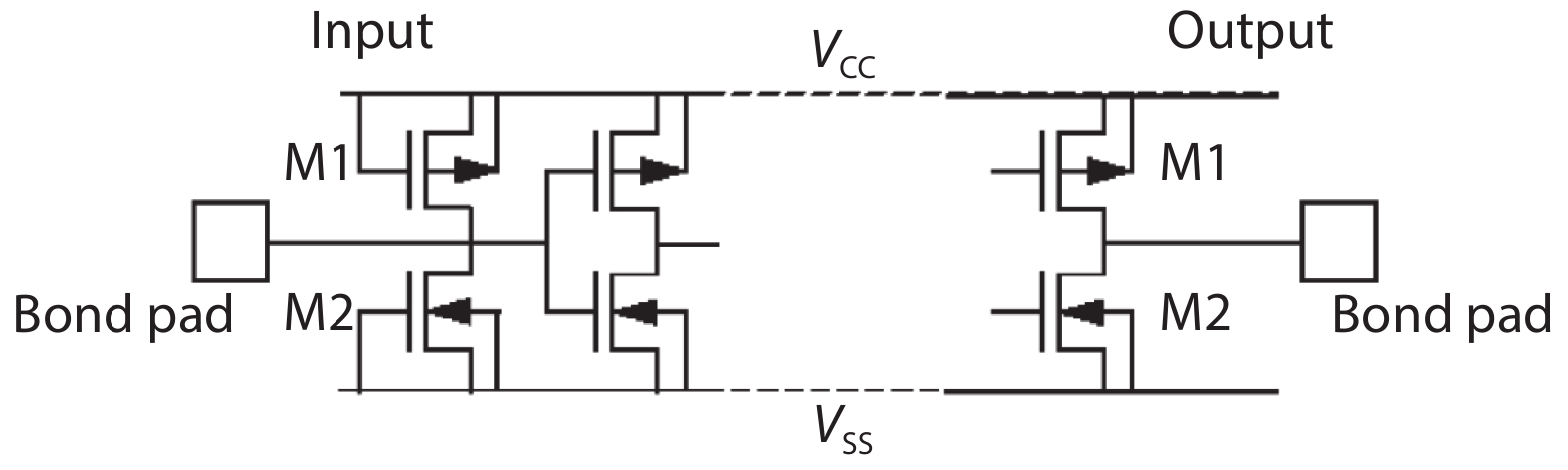

Fig. 2. CMOS input and output ESD protection circuit.

Fig. 3. ESD working principle of GGNMOS device.

Fig. 4. (Color online) Typical discharge curve and design window of GGNMOS device in ESD event.

Fig. 5. (Color online) (a) Structure diagram of GGNMOS. (b) 3D display of GGNMOS device.

Fig. 6. (Color online) TCAD process simulation results of GGNMOS devices.

Fig. 7. Comparison of the TCAD and test structure GGNMOS TLP curve.

Fig. 8. (Color online) The impact ionization, current density and lattice temperature diagrams.

Fig. 9. (Color online) The influence of gate length and DCGS on the lattice temperature of GGNMOS.

Fig. 10. (Color online) Effect of different ESD ion implantation dose on 3.3 V GGNMOS I t2.

Fig. 11. (Color online) Influence of single finger width on ESD current.

Fig. 12. (Color online) Influence of number of fingers on ESD current.

Fig. 13. (Color online) Effect of DCGS size on the ESD performance of GGNMOS.

Fig. 14. (Color online) GGNMOS TLP curves with a total 240 μ m width. (a) 3.3 V GGNMOS TLP It 2 = 2.9 A. (b) 1.8 V GGNMOS TLP I t2 = 3.84 A.

Fig. 15. (Color online) EMMI of DSP circuit pad ESD fails.

Fig. 16. (Color online) GGNMOS I t2 value versus process nodes.

|

Table 1. The radiation-hardened 0.18 μ m CMOS process characteristic parameters.

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Table 2. Comparison with literature.

Set citation alerts for the article

Please enter your email address