Zhengwu Shu, Lei Jiang, Xingxing Hu, Yue Xu. An integrated front-end vertical hall magnetic sensor fabricated in 0.18 μm low-voltage CMOS technology[J]. Journal of Semiconductors, 2022, 43(3): 032402

Search by keywords or author

- Journal of Semiconductors

- Vol. 43, Issue 3, 032402 (2022)

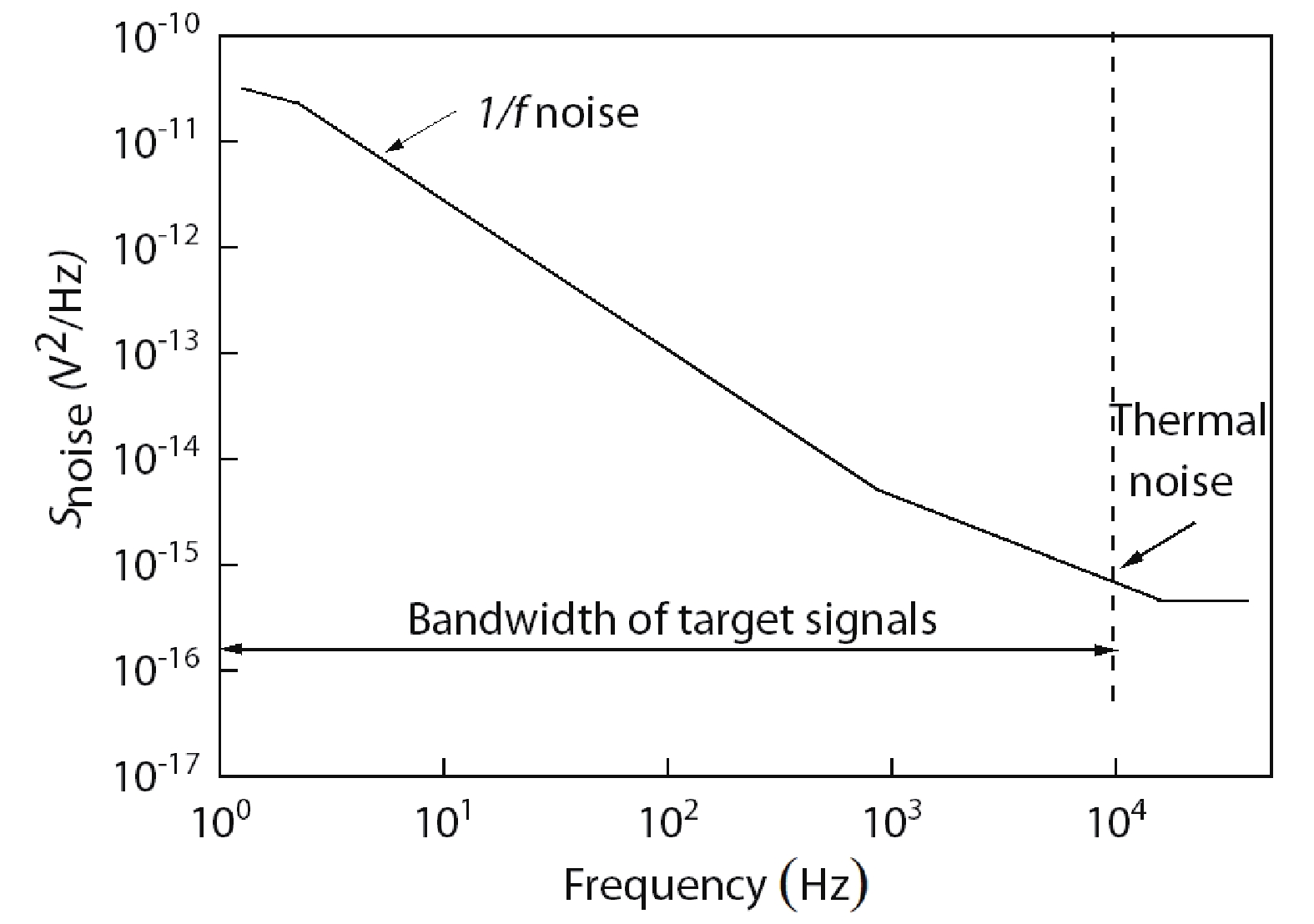

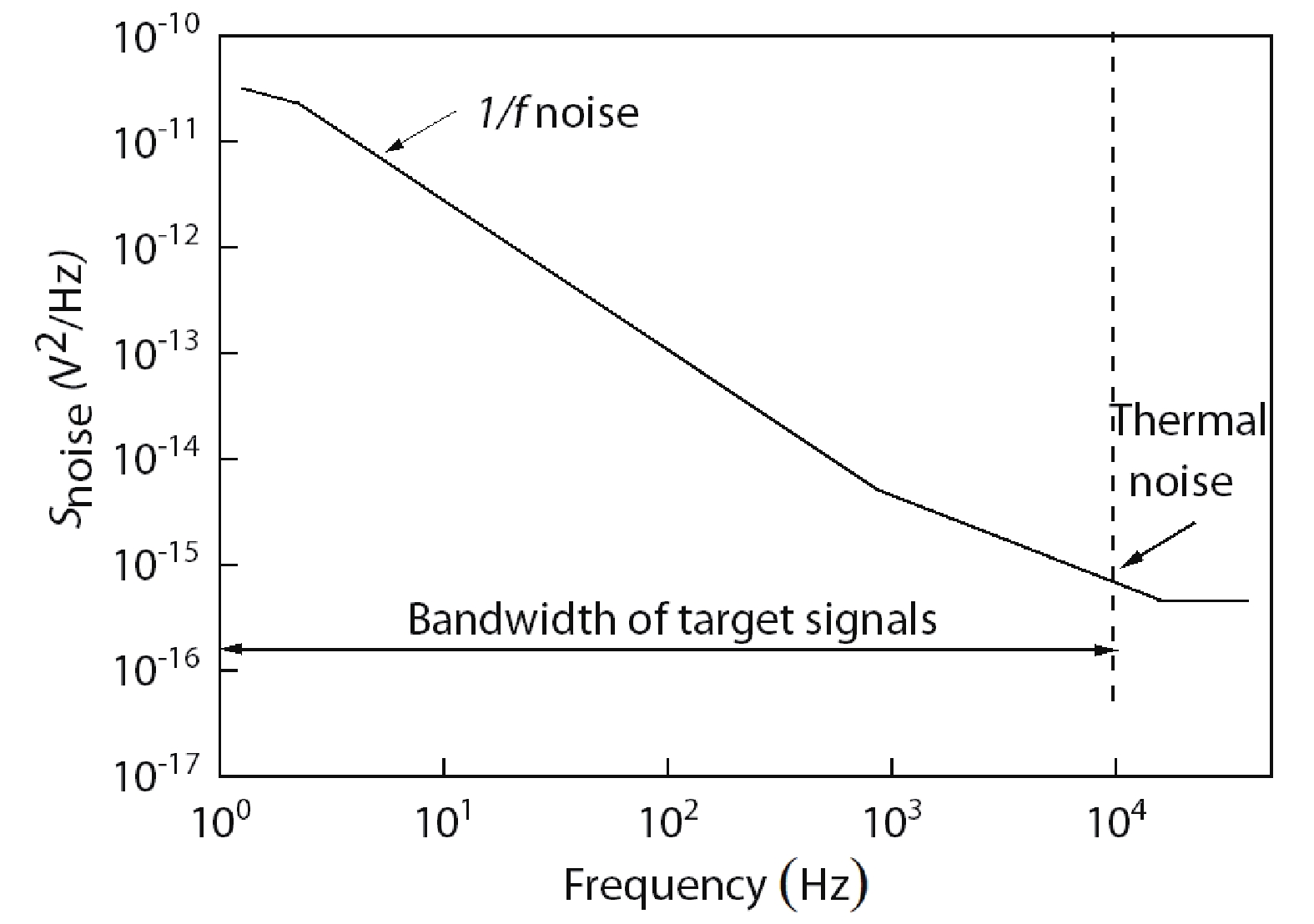

Fig. 1. Schematic diagram of the noise power spectral density of VHDs.

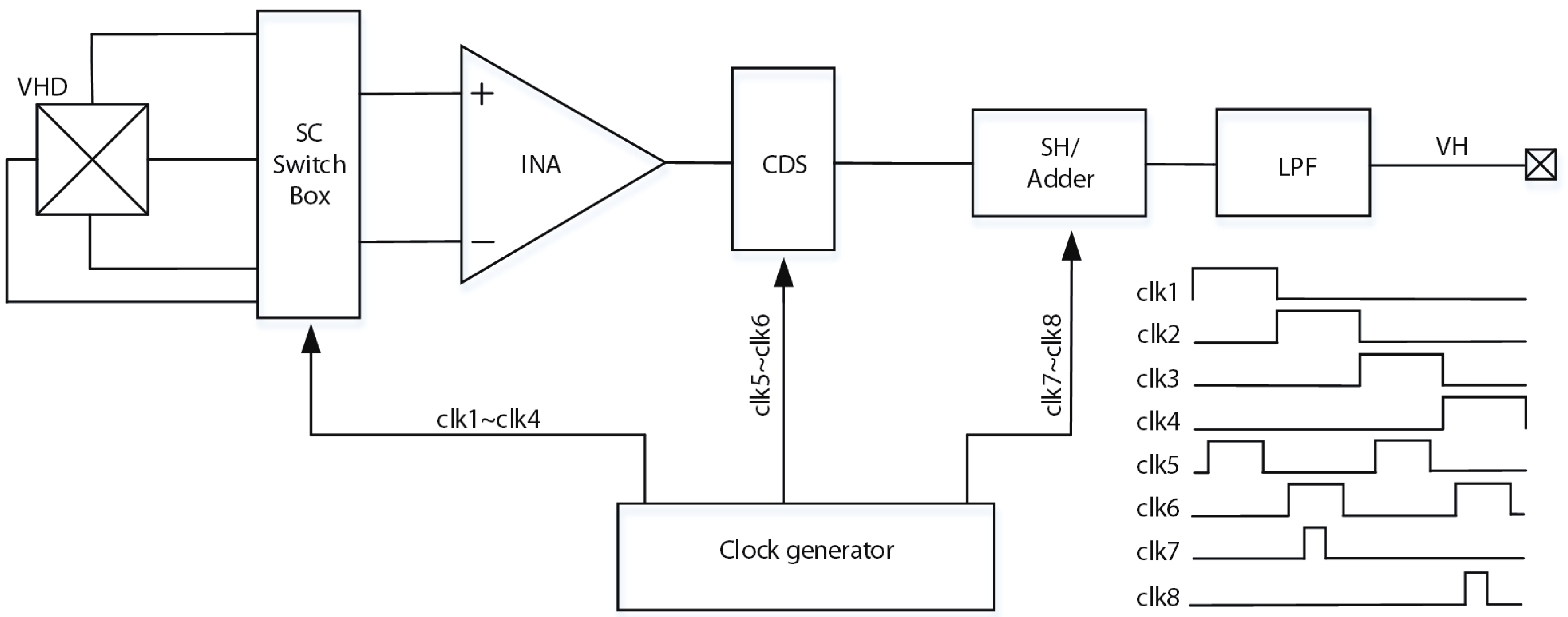

Fig. 2. The block diagram of the proposed vertical Hall sensor.

Fig. 3. Schematic of (a) the FSVHD consisting of four interconnected 3CVHEs and (b) the four operating modes in the four-phase spinning technique.

Fig. 4. (Color online) TCAD simulation results for the FSVHD sensitivity. Sensitivity as a function of (a) L n and (b) L d.

Fig. 5. Schematic diagram of (a) the switched vertical Hall device using four-phase spinning current operation and (b) the output Hall voltage and offset voltage corresponding to the four-phase sequence clocks.

Fig. 6. The schematic diagram of the bridge instrumentation amplifier.

Fig. 7. The schematic diagram of the CDS demodulation circuit.

Fig. 8. (Color online) Hall sensor microphotograph: whole chip including pads with an active area with the back-annotated layout of main circuital blocks.

Fig. 9. (Color online) Experimental setup.

Fig. 10. (Color online) Test Hall voltages as a function of in-plane magnetic field for two FSVHDs. The inset picture shows the voltage-related sensitivity of two FSVHDs.

Fig. 11. (Color online) Tested results of the optimized FSVHD. (a) Offset as a function of bias voltage and (b) 1/f noise at the various bias voltages.

Fig. 12. (Color online) Measured differential output voltages of the vertical Hall sensor as a function of a magnetic field.

|

Table 1. Performance Summary and Comparison Table of This Work With The Reported Ones.

Set citation alerts for the article

Please enter your email address