[1] S R Hofstein, F P Heiman. The silicon insulated-gate field-effect transistor. Proc IEEE, 51, 1190(1963).

[2] G Moore. Cramming more components onto integrated circuits. Electronics, 38, 114(1965).

[3] S E Thompson, M Armstrong, C Auth et al. A 90-nm logic technology featuring strained-silicon. IEEE Trans Electron Devices, 51, 1790(2004).

[4] K Mistry, C Allen, C Auth et al. A 45 nm logic technology with high-k metal gate transistors, strained silicon, 9 Cu interconnect layers, 193nm dry patterning, and 100% Pb-free packaging. IEEE International Electron Devices Meeting, 247(2007).

[5] C Auth, C Allen, A Blattner et al. A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. Symp VLSI Technol VLSIT, 131(2012).

[6] F Balestra, S Cristoloveanu, M Benachir et al. Double-gate silicon-on-insulator transistor with volume inversion: A new device with greatly enhanced performance. IEEE Electron Device Lett, 8, 410(1987).

[7]

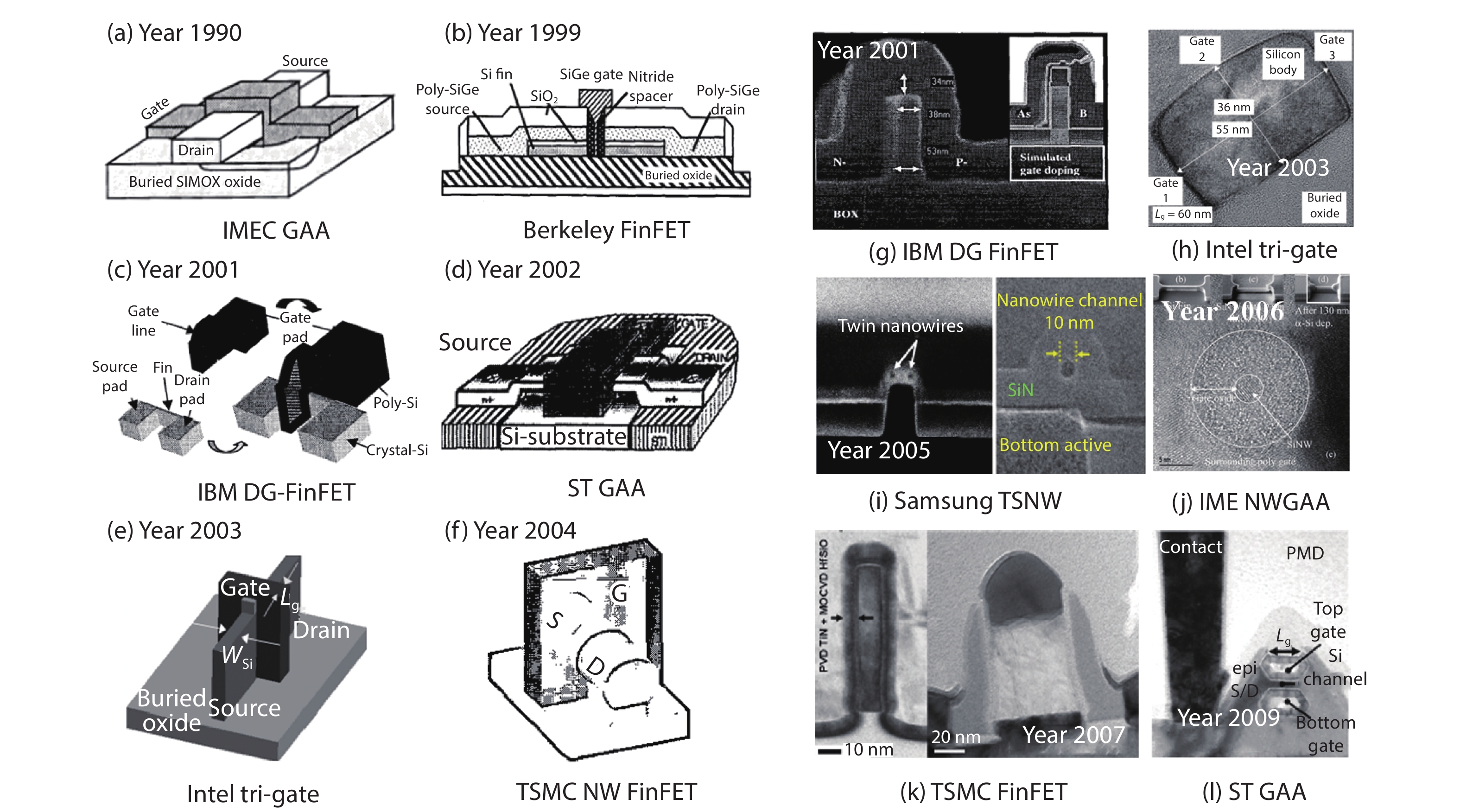

[8] X J Huang, W C Lee, C Kuo et al. Sub 50-nm FinFET: PMOS. IEEE International Electron Devices Meeting, 67(1999).

[9] D Hisamoto, W C Lee, J Kedzierski et al. FinFET – a self-aligned double-gate MOSFET scalable to 20 nm. IEEE Trans Electron Devices, 47, 2320(2000).

[10] B S Doyle, S Datta, M Doczy et al. High performance fully-depleted tri-gate CMOS transistors. IEEE Electron Device Lett, 24, 263(2003).

[11]

[12] F L Yang, H Y Chen, F C Chen et al. 25 nm CMOS Omega FETs. IEEE International Electron Devices Meeting, 255(2002).

[13] B Ho, X Sun, N Xu et al. First demonstration of quasi-planar segmented-channel MOSFET design for improved scalability. IEEE Trans Electron Devices, 59, 2273(2012).

[14] J P Colinge, M H Gao, A Romano-Rodriguez et al. Silicon-on-insulator ‘gate-all-around device’. International Technical Digest on Electron Devices, 595(1990).

[15] S Monfray, T Skotnicki, Y Morand et al. 50 nm-gate all around (GAA)-silicon on nothing (SON)-devices: A simple way to co-integration of GAA transistors within bulk MOSFET process. Symposium on VLSI Technology, 108(2002).

[16] F L Yang, D H Lee, H Y Chen et al. 5nm-gate nanowire FinFET. Symposium on VLSI Technology, 196(2004).

[17] S D Suk, S Y Lee, S M Kim et al. High performance 5nm radius twin silicon nanowire MOSFET (TSNWFET): Fabrication on bulk Si wafer, characteristics, and reliability. IEEE International Electron Devices Meeting, 181(2005).

[18] N Singh, A Agarwal, L K Bera et al. High-performance fully depleted silicon nanowire (diameter ≤ 5 nm) gate-all-around CMOS devices. IEEE Electron Device Lett, 27, 383(2006).

[19] S Barraud, B Previtali, C Vizioz et al. 7-levels-stacked nanosheet GAA transistors for high performance computing. IEEE Symposium on VLSI Technology, 1(2020).

[20]

[21] E Pop. Energy dissipation and transport in nanoscale devices. Nano Res, 3, 147(2010).

[22] L X Yin, L Shen, H Jiang et al. Impact of self-heating effects on nanoscale Ge p-channel FinFETs with Si substrate. Sci China Inf Sci, 61, 1(2017).

[23] D Son, K Hong, H Shim et al. New insight into negative bias temperature instability degradation during self-heating in nanoscale bulk FinFETs. IEEE Electron Device Lett, 40, 1354(2019).

[24] R Cheng, X Yu, B Chen et al. Investigation of self-heating effect on ballistic transport characterization for Si FinFETs featuring ultrafast pulsed IV technique. IEEE Trans Electron Devices, 64, 909(2017).

[25] R Cheng, X Yu, B Chen et al. First investigation of hot carrier injection effects on ballistic transport characteristics for SOI MOSFETs featuring ultrafast pulsed IV measurement. International Reliability Physics Symposium (IRPS), 3E-3(2017).

[26] H K Lim, J G Fossum. Threshold voltage of thin-film silicon-on-insulator (SOI) MOSFET's. IEEE Trans Electron Devices, 30, 1244(1983).

[27] G Vellianitis, M J H van Dal, L Witters et al. Gatestacks for scalable high-performance FinFETs. IEEE International Electron Devices Meeting, 681(2007).

[28] G Bidal, J L Huguenin, S Denorme et al. Gate-all-around technology: Taking advantage of ballistic transport. Proceedings of the European Solid State Device Research Conference, 315(2009).

[29]

[30]

[31] B Doris, Y H Kim, B P Linder et al. High performance FDSOI CMOS technology with metal gate and high-k. Symposium on VLSI Technology, 214(2005).

[32] K Mistry, C Allen, C Auth et al. A 45 nm logic technology with high-k metal gate transistors, strained silicon, 9 Cu interconnect layers, 193nm dry patterning, and 100% Pb-free packaging. IEEE International Electron Devices Meeting, 247(2007).

[33] C H Diaz, K Goto, H T Huang et al. 32nm gate-first high-k/metal-gate technology for high performance low power applications. IEEE International Electron Devices Meeting, 1(2008).

[34] R Coquand, S Monfray, S Barraud et al. Innovative through-Si 3D lithography for ultimate self-aligned planar double-gate and gate-all-around nanowire transistors. Symposium on VLSI Technology, T226(2013).

[35]

[36] S Barraud, R Coquand, M Casse et al. Performance of omega-shaped-gate silicon nanowire MOSFET with diameter down to 8 nm. IEEE Electron Device Lett, 33, 1526(2012).

[37] C Auth, C Allen, A Blattner et al. A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. Symposium on VLSI Technology (VLSIT), 131(2012).

[38] N Loubet, T Hook, P Montanini et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. Symposium on VLSI Technology, T230(2017).

[39]

[40]

[41] M Xu, H X Yin, H L Zhu et al. Device parameter optimization for sub-20 nm node HK/MG-last bulk FinFETs. J Semicond, 36, 044007(2015).

[42] S Deleonibus. Ultra-thin films and multigate devices architectures for future CMOS scaling. Sci China Inf Sci, 54, 990(2011).

[43] M Jurczak, N Collaert, A Veloso et al. Review of FINFET technology. IEEE International SOI Conference, 1(2009).

[44] A Malinowski, J Chen, S K Mishra et al. What is killing Moore's Law, challenges in advanced FinFET technology integration. MIXDES - 26th International Conference Mixed Design of Integrated Circuits and Systems, 46(2019).

[45]

[46] V Moroz. Technology inflection points: Planar to FinFET to nanowire. Int Symp Phys Design(2016).

[47]

[48] Z Aksamija, I Knezevic. Thermal conductivity of Si1–

[49] E Bury, B Kaczer, J Mitard et al. Characterization of self-heating in high-mobility Ge FinFET pMOS devices. IEEE Symp VLSI Technol VLSI Technol, T60(2015).

[50] E Pop, S Sinha, K E Goodson. Heat generation and transport in nanometer-scale transistors. Proc IEEE, 94, 1587(2006).

[51] Y Terada, K Ohkubo, T Mohri et al. Thermal conductivity of cobalt-base alloys. Metall Mater Trans A, 34, 2026(2003).

[52] Y Zhao, Y M Qu. Impact of self-heating effect on transistor characterization and reliability issues in sub-10 nm technology nodes. IEEE J Electron Devices Soc, 7, 829(2019).

[53] W C Chen, R Cheng, D W Wang et al. Electrothermal effects on hot-carrier reliability in SOI MOSFETs—AC versus circuit-speed random stress. IEEE Trans Electron Devices, 63, 3669(2016).

[54] R S Wang, J Zhuge, C Z Liu et al. Experimental study on quasi-ballistic transport in silicon nanowire transistors and the impact of self-heating effects. IEEE International Electron Devices Meeting, 1(2008).

[55] H Jiang, X Y Liu, N Xu et al. Investigation of self-heating effect on hot carrier degradation in multiple-fin SOI FinFETs. IEEE Electron Device Lett, 36, 1258(2015).

[56] T Yamane, N Nagai, S I Katayama et al. Measurement of thermal conductivity of silicon dioxide thin films using a 3ω method. J Appl Phys, 91, 9772(2002).

[57] M Lundstrom. Elementary scattering theory of the Si MOSFET. IEEE Electron Device Lett, 18, 361(1997).

[58] M S Lundstrom. On the mobility versus drain current relation for a nanoscale MOSFET. IEEE Electron Device Lett, 22, 293(2001).

[59] M J Chen, H T Huang, K C Huang et al. Temperature dependent channel backscattering coefficients in nanoscale MOSFETs. IEEE International Electron Devices Meeting, 39(2002).

[60] T Y Liow, K M Tan, H C Chin et al. Carrier transport characteristics of sub-30 nm strained N-channel FinFETs featuring silicon-carbon source/drain regions and methods for further performance enhancement. IEEE International Electron Devices Meeting, 1(2006).

[61] A Dixit, A Kottantharayil, N Collaert et al. Analysis of the parasitic S/D resistance in multiple-gate FETs. IEEE Trans Electron Devices, 52, 1132(2005).

[62] R Tomita, H Kimura, M Yasuda et al. Improvement on sheet resistance uniformity of nickel silicide by optimization of silicidation conditions. Microelectron Reliab, 53, 665(2013).

[63] T Matsukawa, Y X Liu, K Endo et al. Variability origins of parasitic resistance in FinFETs with silicided source/drain. IEEE Electron Device Lett, 33, 474(2012).

[64] P H Su, Y M Li. Determination of source-and-drain series resistance in 16-nm-gate FinFET devices. IEEE Trans Electron Devices, 62, 1663(2015).

[65] N Choudhury, U Sharma, H M Zhou et al. Analysis of BTI, SHE induced BTI and HCD under full VG/VD space in GAA nano-sheet N and P FETs. IEEE International Reliability Physics Symposium (IRPS), 1(2020).

[66] C Prasad. A review of self-heating effects in advanced CMOS technologies. IEEE Trans Electron Devices, 66, 4546(2019).

[67] M M Wang, J Y Zhang, H M Zhou et al. Bias temperature instability reliability in stacked gate-all-around nanosheet transistor. IEEE International Reliability Physics Symposium (IRPS), 1(2019).

[68]

[69] R Zhang, K X Yang, T Z Liu et al. New electromigration model and its potential application on degradation simulation for FinFET SRAM. International Integrated Reliability Workshop (IIRW), 1(2018).

[70]

[71] W K Wu, X An, X B Jiang et al. Line-edge roughness induced single event transient variation in SOI FinFETs. J Semicond, 36, 114001(2015).

[72] J Z Chen, Y Nakasaki, Y Mitani. Deep insight into process-induced pre-existing traps and PBTI stress-induced trap generations in high-k gate dielectrics through systematic RTN characterizations and ab initio calculations. IEEE Symposium on VLSI Technology, 1(2016).

[73] X P Zhan, Y F Xi, Q W Wang et al. Dual-point technique for multi-trap RTN signal extraction. IEEE Access, 8, 88141(2020).

[74]

[75] P C Feijoo, T Kauerauf, M Toledano-Luque et al. Time-dependent dielectric breakdown on subnanometer EOT nMOS FinFETs. IEEE Trans Device Mater Reliab, 12, 166(2012).

[76] D Lei, K H Lee, S Y Bao et al. The first GeSn FinFET on a novel GeSnOI substrate achieving lowest S of 79 mV/decade and record high Gm, int of 807

[77]

[78]

[79]

[80]

[81]

[82] C L Chu, K Wu, G L Luo et al. Stacked Ge-nanosheet GAAFETs fabricated by Ge/Si multilayer epitaxy. IEEE Electron Device Lett, 39, 1133(2018).

[83] W W Fang, N Singh, L K Bera et al. Vertically stacked SiGe nanowire array channel CMOS transistors. IEEE Electron Device Lett, 28, 211(2007).

[84] X Gong, G Q Han, F Bai et al. Germanium–tin (GeSn) p-channel MOSFETs fabricated on (100) and (111) surface orientations with sub-400 °C Si2H6 passivation. IEEE Electron Device Lett, 34, 339(2013).

[85]

[86] B Liu, X Gong, G Q Han et al. High-performance germanium ω-gate MuGFET with Schottky-barrier nickel germanide source/drain and low-temperature disilane-passivated gate stack. IEEE Electron Device Lett, 33, 1336(2012).

[87]

[88] R Zhang, T Iwasaki, N Taoka et al. Al2O3/GeO

[89] J Mitard, C Shea, B DeJaeger et al. Impact of EOT scaling down to 0.85 nm on 70 nm Ge-pFETs technology with STI. VLSI Symp Tech Dig, 82(2009).

[90] J Franco, B Kaczer, J Mitard et al. NBTI reliability of SiGe and Ge channel pMOSFETs with SiO2/HfO2 dielectric stack. IEEE Trans Device Mater Reliab, 13, 497(2013).