- Journal of Semiconductors

- Vol. 42, Issue 2, 023102 (2021)

Abstract

1. Introduction

Since the first demonstration of Si metal–oxide–semiconductor field-effect transistors (MOSFETs) in 1960s[

To further boost the cost-performance efficiency following Moore’s law, transistors with novel-structures have been adopted to improve the power density per footprint, for sub-20 nm technology nodes. Multi-gate MOSFETs (MuGFETs), owing to the additional conducting channels at the sidewalls, exhibit superior electrostatic control as well as higher current density per area. Since 22 nm technology node, tri-gate Si MOSFETs have been adopted by Intel[

In fact, multi-gate transistors have been experimentally demonstrated and studied for a long time since 1980s. The history of double gate MOSFETs on silicon-on-insulator (SOI) substrate can be pursued to late 80s[

In this work, we will review the process development and reliability issues related to the state-of-the-art Si MuGFETs. From the historical perspective, the development of various MuGFET technologies will be clearly provided, followed by a discussion on the process challenges based on current technology. Next, the reliability issues, including SHE, carrier transport, BTI and HCI are discussed for various MuGFET technologies. Among the existing review works on MuGFETs, the carrier transport behavior of these ultrascaled 3D devices was rarely analyzed. In this paper, the ballistic transport characteristics of MuGFETs and the impact of SHE on it were thoroughly summarized for MuGFETs, thin body SOI FETs (w/ and w/o HCI), and thin body GeOI FET. The SHE induced transport and reliability issues, especially the difference with the planar transistors, will be discussed. An overlook of the future technology trend on new material MuGFETs will be touched up at the end.

2. Process development of Si multi-gate transistors

2.1. A historical view on the development of MuGFETs

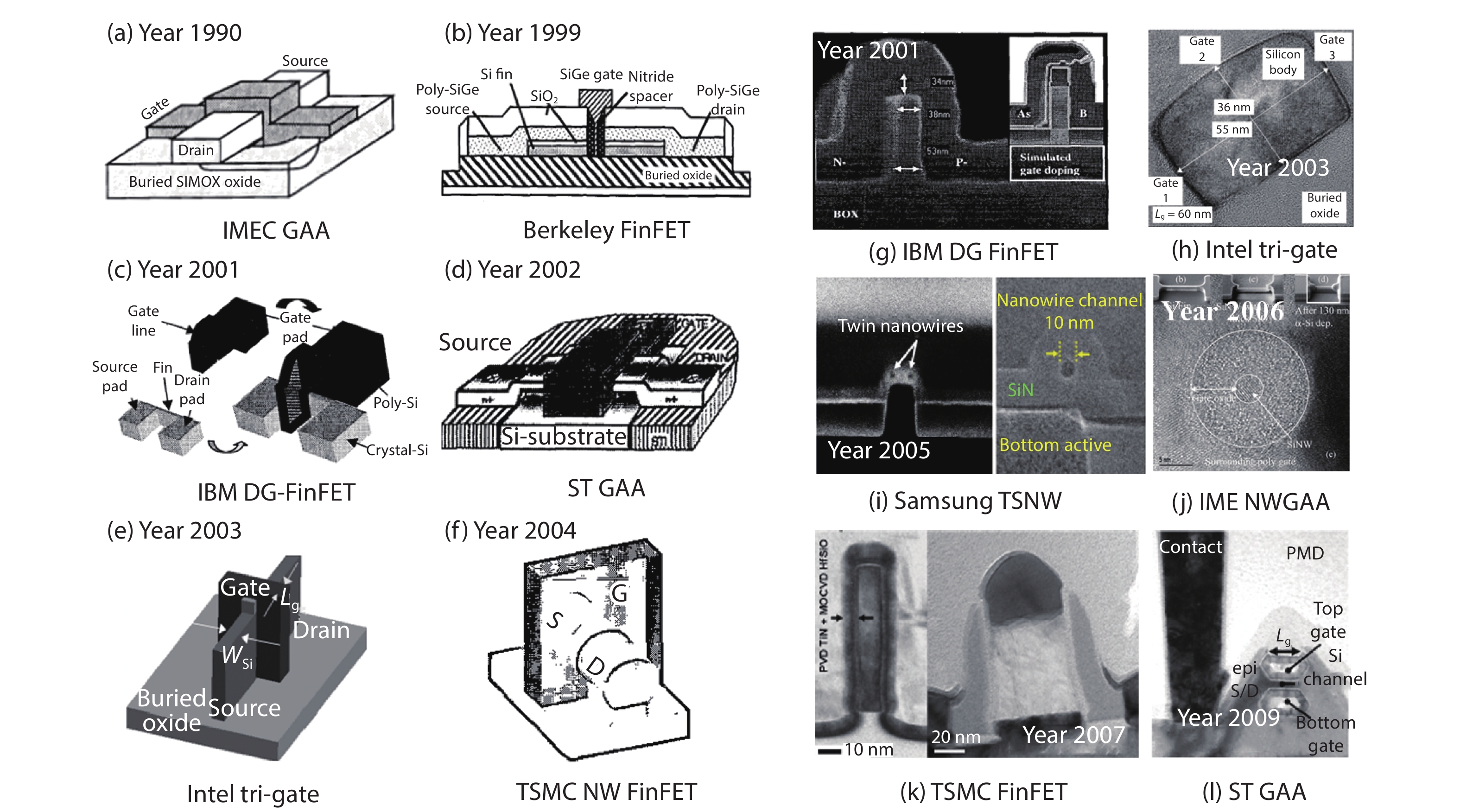

In late 1980s, double-gate Si MOSFETs was initially demonstrated on SOI substrate. The purpose of the back gate is to tune the threshold voltage VT of the front-gate transistor[

![]()

Figure 1.(a–f) Schematics of MuGFETs with different gate geometries: (a) IMEC’s gate-all-around (GAA) MOSFET[

![]()

Figure 2.(Color online) Evolution of MuGFETs from the planar device to the stacking structures. (a) Planar MOSFET. (b) Double-gate (DG) fully depleted SOI MOSFET. (c) FinFET. (d) Ω-gate MOSFET. (e) GAA NW MOSFET. (f) GAA multilayer nanosheet MOSFET.

![]()

Figure 3.(Color online) DIBL performance as a function of gate length among FDSOI, FinFET and planar technologies[

![]()

Figure 4.(Color online) Comparison of DIBL from ETSOI, DG, tri-gate, and GAA technologies as effective channel length reduces. Data are obtained from IBM and Intel Corp[

The initial demonstration of MuGFET technology was realized on SOI platform due to the simplicity in process design and elimination of junction leakage to the substrate. In 2011, Intel announced its advanced 22 nm FinFET technology on bulk Si wafer[

2.2. Process challenges in state-of-the-art MuGFETs

To achieve better gate control over SCEs, the narrow fin and ultrathin nanosheet structures are exploited in the most advanced MuGFETs. Fig. 5 provides the ION–DIBL data for several advanced Si MuGFETs reported in recent years with different process technologies[

![]()

Figure 5.(Color online)

With the continuous scaling down of Si CMOS, the Si process technology encounters more challenges for the realization of higher density, higher performance, and higher reliability Si MuGFET CMOS. Take the 7-layer NS MOSFET in Ref. [19] as an example. The 3D stacking design could help to achieve extraordinary ION per footprint but greatly increase the process difficulty in gate stack formation and heating-related degradation issues in the channel. In general, the process challenge for massive production of high-quality Si MuGFETs lies in the following aspects: lithography capability, product integration, variability control, threshold voltage tuning, and strain engineering[

3. Reliability issues of multi-gate transistors

3.1. Self-heating effect and carrier transport analysis

For short channel transistors, self-heating issues have become increasingly ineligible. As the drive current is inversely proportional to the gate length, the power density increases as the gate length shrinks. Furthermore, as compared with the traditional 2D/planar device architecture, 3D/FinFET structure exhibits more severe SHE[

![]()

Figure 6.(Color online) Thermal resistivity

![]()

Figure 7.(Color online) Thermal conductivity for various materials used in gate stack, source/drain, channel, isolation and interconnects in a MuGFET. The conductivity reduces as the technology node shrinks. Higher mobility channel materials like Ge and SiGe also exhibit lower thermal conductivity[

The increased SHE occurring near the channel/drain boundary would introduce various issues in device performance and reliability[

![]()

Figure 8.

For sub-100 nm FinFETs operated in quasi-ballistic regime, the ballistic transport characteristics would be greatly affected by SHE, especially when using the DC measurement setups. While in “real” IC circuit operated with a frequency of a few tens of GHz, the device temperature is much lower and therefore the SHE is less severe than that under DC measurement[

![]()

Figure 9.(Color online) (a) The schematic illustration of a pulsed

It should be noted here that, compared to the bulk FinFET, the SOI FinFET has even worse thermal dissipation capability with the insertion of buried oxide layer whose thermal conductivity is only around 1% of Si at the same thickness[

According to Lundstrom’s theory[

where η and α are defined to be the slopes of VT shift ΔVT and ΔIDsat/IDsat with respective to temperature T, respectively. From the extracted λo/lo, Bsat can be calculated using

where rsat is the carrier backscattering ratio, i.e. the fraction of injected carriers being scattering back from the channel. Furthermore, as compared with the bulk planar transistors, the series resistance for short-channel FinFETs is much larger due to the shrunk S/D regions[

where ΔRSD is the change of RSD as the channel temperature T changes. By correcting the effect of temperature-dependent RSD on the backscattering model, λo/lo could be extracted by the following modified equation:

while the correlation among λo/lo, rsat and Bsat remains unchanged.

For multi-gate transistors, the parasitic resistance exhibits large variability. Therefore, to accurately exempt the effect of RSD on the backscattering parameters, RSD was extracted for individual device at every characterization temperature. Fig. 10 shows the RTotal–VG plot for a FinFET with LG = 40 nm at three different characterization T. By fitting the data points in Fig. 10(a), RSD at each T could be taken at very high gate bias. As T increases, RSD gradually increases. For the FinFET in Fig. 10, RSD shows a linear relationship with T and its temperature dependent coefficient β is 0.591 Ω/K. Based on the corrected backscattering model, λo/lo was extracted at various gate lengths for both the “DC” and “pulse” cases. The RSD-corrected λo/lo as a function of LG is shown in Fig. 10. The values of λo/lo without considering the temperature-dependent RSD in the backscattering model is also included in Fig. 10 for comparison. As discussed before, since using pulsed I–V method could exempt the SHE on the characterization of ballistic transport, the mean free path in “pulse” case is larger than that in the “DC” case, as in the latter case the channel is heated up due to the severe SHE, leading to more scattering or shorter mean free path. As shown in Fig. 10, λo/lo ratio is higher for devices with shorter LG. As λo in the “pulse” case is larger, λo/lo ratio extracted from the pulsed I–V measurement is generally higher than the one extracted from the DC measurement. The difference of λo/lo between the two measurement conditions is slightly higher for FinFETs with smaller LG. As LG decreases, λo/lo in both “DC” and “pulse” cases increase while that extracted from pulsed I–V measurements increases more. This result indicates that self-heating may have more effects for devices with shorter LG. For sub-100 nm devices, using DC measurement to estimate the backscattering parameters may not cause large discrepancies but for FinFETs with sub-50 nm or even smaller gate length, pulsed I–V method would be more accurate for the extraction of backscattering parameters.

![]()

Figure 10.(a) Total resistance

Fig. 11 compares the ballisticity of FinFETs, FDSOI planar Si and Ge FETs. The trendline in the figure is obtained based on a numerical fitting model[

![]()

Figure 11.A summary of 1/

3.2. Bias temperature instability and hot carrier injection

Biased temperature instability (BTI) and hot carrier degradation (HCD) are the two main factors determining the lifetime of a transistor. With the scaling down of conventional transistors, negative bias temperature instability (NBTI) has become a major aging issue for p-channel MOSFETs while positive bias temperature instability (PBTI) gets unobvious for n-channel transistors[

For quite a period of time along the roadmap of Moore’s law, HCD is no longer an issue on the aging of CMOS[

![]()

Figure 12.(Color online) The change of interface trap density Δ

Fig. 13 summarizes the estimated aging contribution for HCD and BTI for both p- and n-channel FinFET from Intel, based on its 14 and 10 nm node FinFETs[

![]()

Figure 13.(Color online) Aging contribution from NBTI, PBTI, NHCD, and PHCD are compared for 14 and 10 nm technology nodes. Since the improvement in NBTI from 14 to 10 nm node could compensate the aggravation of HCD for both p- and n-FinFETs, the end-of-line (EOL) drive for the 10 nm node actually improves by 1.65 times[

With the aggressive scaling down of MuGFETs, BTI and HCI are not the only reliability issues in the MuGFET technologies. Reliability topics like electromigration[

4. Future trends

Although Si CMOS technology is still the sole choice for mass production of IC chips by the industry, in-depth research has been done to explore and pursue novel material transistors with higher-mobility beyond Si MOSFETs. III–V compound, Ge and GeSn channel MOSFETs were demonstrated to overcome the mobility limit of the traditional Si transistors[

To overcome the interface problems, in the past ten years, various passivation techniques were examined on the novel channel transistors[

![]()

Figure 14.(Color online) Comparison of SS and

5. Conclusion

3D structured MuGFETs with several different gate stack technologies were reviewed in this work. With more degree of gate wrapping over the transistor channel, excellent control of SCEs and volume inversion of channel can be achieved, demonstrating Si MuGFETs with superior electrostatic characteristics. For 14 nm technology node and beyond, the difficulties in process integration and co-optimization are discussed, as so to further improve the device performance and reliability. The carrier transport characteristics, BTI and HCI aging for Si MuGFETs with severe SHE were also investigated. At the end of the review, the possible future MuGFETs with novel high-mobility channels were discussed and compared. To make it possible to replace the current high performance Si MuGFETs, process optimization is still necessary to improve the gate stack quality and source/drain junctions.

Acknowledgements

The authors would like to express their deep gratitude to Prof. Hanming Wu from the School of Micro-nano Electronics, Zhejiang University for his valuable and inspiring discussion with the authors. This work was supported by Zhejiang Provincial Natural Science Foundation of China under Grant LR18F040001, LY19F040001, and the Opening Project of Key Laboratory of Microelectronic Devices & Integrated Technology, Institute of Microelectronics, Chinese Academy of Sciences.

References

[1] S R Hofstein, F P Heiman. The silicon insulated-gate field-effect transistor. Proc IEEE, 51, 1190(1963).

[2] G Moore. Cramming more components onto integrated circuits. Electronics, 38, 114(1965).

[3] S E Thompson, M Armstrong, C Auth et al. A 90-nm logic technology featuring strained-silicon. IEEE Trans Electron Devices, 51, 1790(2004).

[4] K Mistry, C Allen, C Auth et al. A 45 nm logic technology with high-k metal gate transistors, strained silicon, 9 Cu interconnect layers, 193nm dry patterning, and 100% Pb-free packaging. IEEE International Electron Devices Meeting, 247(2007).

[5] C Auth, C Allen, A Blattner et al. A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. Symp VLSI Technol VLSIT, 131(2012).

[6] F Balestra, S Cristoloveanu, M Benachir et al. Double-gate silicon-on-insulator transistor with volume inversion: A new device with greatly enhanced performance. IEEE Electron Device Lett, 8, 410(1987).

[7]

[8] X J Huang, W C Lee, C Kuo et al. Sub 50-nm FinFET: PMOS. IEEE International Electron Devices Meeting, 67(1999).

[9] D Hisamoto, W C Lee, J Kedzierski et al. FinFET – a self-aligned double-gate MOSFET scalable to 20 nm. IEEE Trans Electron Devices, 47, 2320(2000).

[10] B S Doyle, S Datta, M Doczy et al. High performance fully-depleted tri-gate CMOS transistors. IEEE Electron Device Lett, 24, 263(2003).

[11]

[12] F L Yang, H Y Chen, F C Chen et al. 25 nm CMOS Omega FETs. IEEE International Electron Devices Meeting, 255(2002).

[13] B Ho, X Sun, N Xu et al. First demonstration of quasi-planar segmented-channel MOSFET design for improved scalability. IEEE Trans Electron Devices, 59, 2273(2012).

[14] J P Colinge, M H Gao, A Romano-Rodriguez et al. Silicon-on-insulator ‘gate-all-around device’. International Technical Digest on Electron Devices, 595(1990).

[15] S Monfray, T Skotnicki, Y Morand et al. 50 nm-gate all around (GAA)-silicon on nothing (SON)-devices: A simple way to co-integration of GAA transistors within bulk MOSFET process. Symposium on VLSI Technology, 108(2002).

[16] F L Yang, D H Lee, H Y Chen et al. 5nm-gate nanowire FinFET. Symposium on VLSI Technology, 196(2004).

[17] S D Suk, S Y Lee, S M Kim et al. High performance 5nm radius twin silicon nanowire MOSFET (TSNWFET): Fabrication on bulk Si wafer, characteristics, and reliability. IEEE International Electron Devices Meeting, 181(2005).

[18] N Singh, A Agarwal, L K Bera et al. High-performance fully depleted silicon nanowire (diameter ≤ 5 nm) gate-all-around CMOS devices. IEEE Electron Device Lett, 27, 383(2006).

[19] S Barraud, B Previtali, C Vizioz et al. 7-levels-stacked nanosheet GAA transistors for high performance computing. IEEE Symposium on VLSI Technology, 1(2020).

[20]

[21] E Pop. Energy dissipation and transport in nanoscale devices. Nano Res, 3, 147(2010).

[22] L X Yin, L Shen, H Jiang et al. Impact of self-heating effects on nanoscale Ge p-channel FinFETs with Si substrate. Sci China Inf Sci, 61, 1(2017).

[23] D Son, K Hong, H Shim et al. New insight into negative bias temperature instability degradation during self-heating in nanoscale bulk FinFETs. IEEE Electron Device Lett, 40, 1354(2019).

[24] R Cheng, X Yu, B Chen et al. Investigation of self-heating effect on ballistic transport characterization for Si FinFETs featuring ultrafast pulsed IV technique. IEEE Trans Electron Devices, 64, 909(2017).

[25] R Cheng, X Yu, B Chen et al. First investigation of hot carrier injection effects on ballistic transport characteristics for SOI MOSFETs featuring ultrafast pulsed IV measurement. International Reliability Physics Symposium (IRPS), 3E-3(2017).

[26] H K Lim, J G Fossum. Threshold voltage of thin-film silicon-on-insulator (SOI) MOSFET's. IEEE Trans Electron Devices, 30, 1244(1983).

[27] G Vellianitis, M J H van Dal, L Witters et al. Gatestacks for scalable high-performance FinFETs. IEEE International Electron Devices Meeting, 681(2007).

[28] G Bidal, J L Huguenin, S Denorme et al. Gate-all-around technology: Taking advantage of ballistic transport. Proceedings of the European Solid State Device Research Conference, 315(2009).

[29]

[30]

[31] B Doris, Y H Kim, B P Linder et al. High performance FDSOI CMOS technology with metal gate and high-k. Symposium on VLSI Technology, 214(2005).

[32] K Mistry, C Allen, C Auth et al. A 45 nm logic technology with high-k metal gate transistors, strained silicon, 9 Cu interconnect layers, 193nm dry patterning, and 100% Pb-free packaging. IEEE International Electron Devices Meeting, 247(2007).

[33] C H Diaz, K Goto, H T Huang et al. 32nm gate-first high-k/metal-gate technology for high performance low power applications. IEEE International Electron Devices Meeting, 1(2008).

[34] R Coquand, S Monfray, S Barraud et al. Innovative through-Si 3D lithography for ultimate self-aligned planar double-gate and gate-all-around nanowire transistors. Symposium on VLSI Technology, T226(2013).

[35]

[36] S Barraud, R Coquand, M Casse et al. Performance of omega-shaped-gate silicon nanowire MOSFET with diameter down to 8 nm. IEEE Electron Device Lett, 33, 1526(2012).

[37] C Auth, C Allen, A Blattner et al. A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. Symposium on VLSI Technology (VLSIT), 131(2012).

[38] N Loubet, T Hook, P Montanini et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. Symposium on VLSI Technology, T230(2017).

[39]

[40]

[41] M Xu, H X Yin, H L Zhu et al. Device parameter optimization for sub-20 nm node HK/MG-last bulk FinFETs. J Semicond, 36, 044007(2015).

[42] S Deleonibus. Ultra-thin films and multigate devices architectures for future CMOS scaling. Sci China Inf Sci, 54, 990(2011).

[43] M Jurczak, N Collaert, A Veloso et al. Review of FINFET technology. IEEE International SOI Conference, 1(2009).

[44] A Malinowski, J Chen, S K Mishra et al. What is killing Moore's Law, challenges in advanced FinFET technology integration. MIXDES - 26th International Conference Mixed Design of Integrated Circuits and Systems, 46(2019).

[45]

[46] V Moroz. Technology inflection points: Planar to FinFET to nanowire. Int Symp Phys Design(2016).

[47]

[48] Z Aksamija, I Knezevic. Thermal conductivity of Si1–

[49] E Bury, B Kaczer, J Mitard et al. Characterization of self-heating in high-mobility Ge FinFET pMOS devices. IEEE Symp VLSI Technol VLSI Technol, T60(2015).

[50] E Pop, S Sinha, K E Goodson. Heat generation and transport in nanometer-scale transistors. Proc IEEE, 94, 1587(2006).

[51] Y Terada, K Ohkubo, T Mohri et al. Thermal conductivity of cobalt-base alloys. Metall Mater Trans A, 34, 2026(2003).

[52] Y Zhao, Y M Qu. Impact of self-heating effect on transistor characterization and reliability issues in sub-10 nm technology nodes. IEEE J Electron Devices Soc, 7, 829(2019).

[53] W C Chen, R Cheng, D W Wang et al. Electrothermal effects on hot-carrier reliability in SOI MOSFETs—AC versus circuit-speed random stress. IEEE Trans Electron Devices, 63, 3669(2016).

[54] R S Wang, J Zhuge, C Z Liu et al. Experimental study on quasi-ballistic transport in silicon nanowire transistors and the impact of self-heating effects. IEEE International Electron Devices Meeting, 1(2008).

[55] H Jiang, X Y Liu, N Xu et al. Investigation of self-heating effect on hot carrier degradation in multiple-fin SOI FinFETs. IEEE Electron Device Lett, 36, 1258(2015).

[56] T Yamane, N Nagai, S I Katayama et al. Measurement of thermal conductivity of silicon dioxide thin films using a 3ω method. J Appl Phys, 91, 9772(2002).

[57] M Lundstrom. Elementary scattering theory of the Si MOSFET. IEEE Electron Device Lett, 18, 361(1997).

[58] M S Lundstrom. On the mobility versus drain current relation for a nanoscale MOSFET. IEEE Electron Device Lett, 22, 293(2001).

[59] M J Chen, H T Huang, K C Huang et al. Temperature dependent channel backscattering coefficients in nanoscale MOSFETs. IEEE International Electron Devices Meeting, 39(2002).

[60] T Y Liow, K M Tan, H C Chin et al. Carrier transport characteristics of sub-30 nm strained N-channel FinFETs featuring silicon-carbon source/drain regions and methods for further performance enhancement. IEEE International Electron Devices Meeting, 1(2006).

[61] A Dixit, A Kottantharayil, N Collaert et al. Analysis of the parasitic S/D resistance in multiple-gate FETs. IEEE Trans Electron Devices, 52, 1132(2005).

[62] R Tomita, H Kimura, M Yasuda et al. Improvement on sheet resistance uniformity of nickel silicide by optimization of silicidation conditions. Microelectron Reliab, 53, 665(2013).

[63] T Matsukawa, Y X Liu, K Endo et al. Variability origins of parasitic resistance in FinFETs with silicided source/drain. IEEE Electron Device Lett, 33, 474(2012).

[64] P H Su, Y M Li. Determination of source-and-drain series resistance in 16-nm-gate FinFET devices. IEEE Trans Electron Devices, 62, 1663(2015).

[65] N Choudhury, U Sharma, H M Zhou et al. Analysis of BTI, SHE induced BTI and HCD under full VG/VD space in GAA nano-sheet N and P FETs. IEEE International Reliability Physics Symposium (IRPS), 1(2020).

[66] C Prasad. A review of self-heating effects in advanced CMOS technologies. IEEE Trans Electron Devices, 66, 4546(2019).

[67] M M Wang, J Y Zhang, H M Zhou et al. Bias temperature instability reliability in stacked gate-all-around nanosheet transistor. IEEE International Reliability Physics Symposium (IRPS), 1(2019).

[68]

[69] R Zhang, K X Yang, T Z Liu et al. New electromigration model and its potential application on degradation simulation for FinFET SRAM. International Integrated Reliability Workshop (IIRW), 1(2018).

[70]

[71] W K Wu, X An, X B Jiang et al. Line-edge roughness induced single event transient variation in SOI FinFETs. J Semicond, 36, 114001(2015).

[72] J Z Chen, Y Nakasaki, Y Mitani. Deep insight into process-induced pre-existing traps and PBTI stress-induced trap generations in high-k gate dielectrics through systematic RTN characterizations and ab initio calculations. IEEE Symposium on VLSI Technology, 1(2016).

[73] X P Zhan, Y F Xi, Q W Wang et al. Dual-point technique for multi-trap RTN signal extraction. IEEE Access, 8, 88141(2020).

[74]

[75] P C Feijoo, T Kauerauf, M Toledano-Luque et al. Time-dependent dielectric breakdown on subnanometer EOT nMOS FinFETs. IEEE Trans Device Mater Reliab, 12, 166(2012).

[76] D Lei, K H Lee, S Y Bao et al. The first GeSn FinFET on a novel GeSnOI substrate achieving lowest S of 79 mV/decade and record high Gm, int of 807

[77]

[78]

[79]

[80]

[81]

[82] C L Chu, K Wu, G L Luo et al. Stacked Ge-nanosheet GAAFETs fabricated by Ge/Si multilayer epitaxy. IEEE Electron Device Lett, 39, 1133(2018).

[83] W W Fang, N Singh, L K Bera et al. Vertically stacked SiGe nanowire array channel CMOS transistors. IEEE Electron Device Lett, 28, 211(2007).

[84] X Gong, G Q Han, F Bai et al. Germanium–tin (GeSn) p-channel MOSFETs fabricated on (100) and (111) surface orientations with sub-400 °C Si2H6 passivation. IEEE Electron Device Lett, 34, 339(2013).

[85]

[86] B Liu, X Gong, G Q Han et al. High-performance germanium ω-gate MuGFET with Schottky-barrier nickel germanide source/drain and low-temperature disilane-passivated gate stack. IEEE Electron Device Lett, 33, 1336(2012).

[87]

[88] R Zhang, T Iwasaki, N Taoka et al. Al2O3/GeO

[89] J Mitard, C Shea, B DeJaeger et al. Impact of EOT scaling down to 0.85 nm on 70 nm Ge-pFETs technology with STI. VLSI Symp Tech Dig, 82(2009).

[90] J Franco, B Kaczer, J Mitard et al. NBTI reliability of SiGe and Ge channel pMOSFETs with SiO2/HfO2 dielectric stack. IEEE Trans Device Mater Reliab, 13, 497(2013).

Set citation alerts for the article

Please enter your email address