- Chinese Optics Letters

- Vol. 20, Issue 1, 011302 (2022)

Abstract

1. Introduction

Silicon photonics has been attracting lots of attention in recent years[

It is a challenging task to design efficient couplers with large bandwidths, low insertion loss, and small footprint that connect on-chip multimode waveguides and FMFs due to their huge mode mismatch. Vertical and edge coupling schemes are the most common ways to realize multimode fiber-chip coupling. For vertical coupling, grating couplers (GCs)[

In this Letter, we report a silicon edge coupler based on adiabatic taper for four-mode fiber-to-chip coupling. The proposed coupler consists of a

2. Operation Principle and Device Design

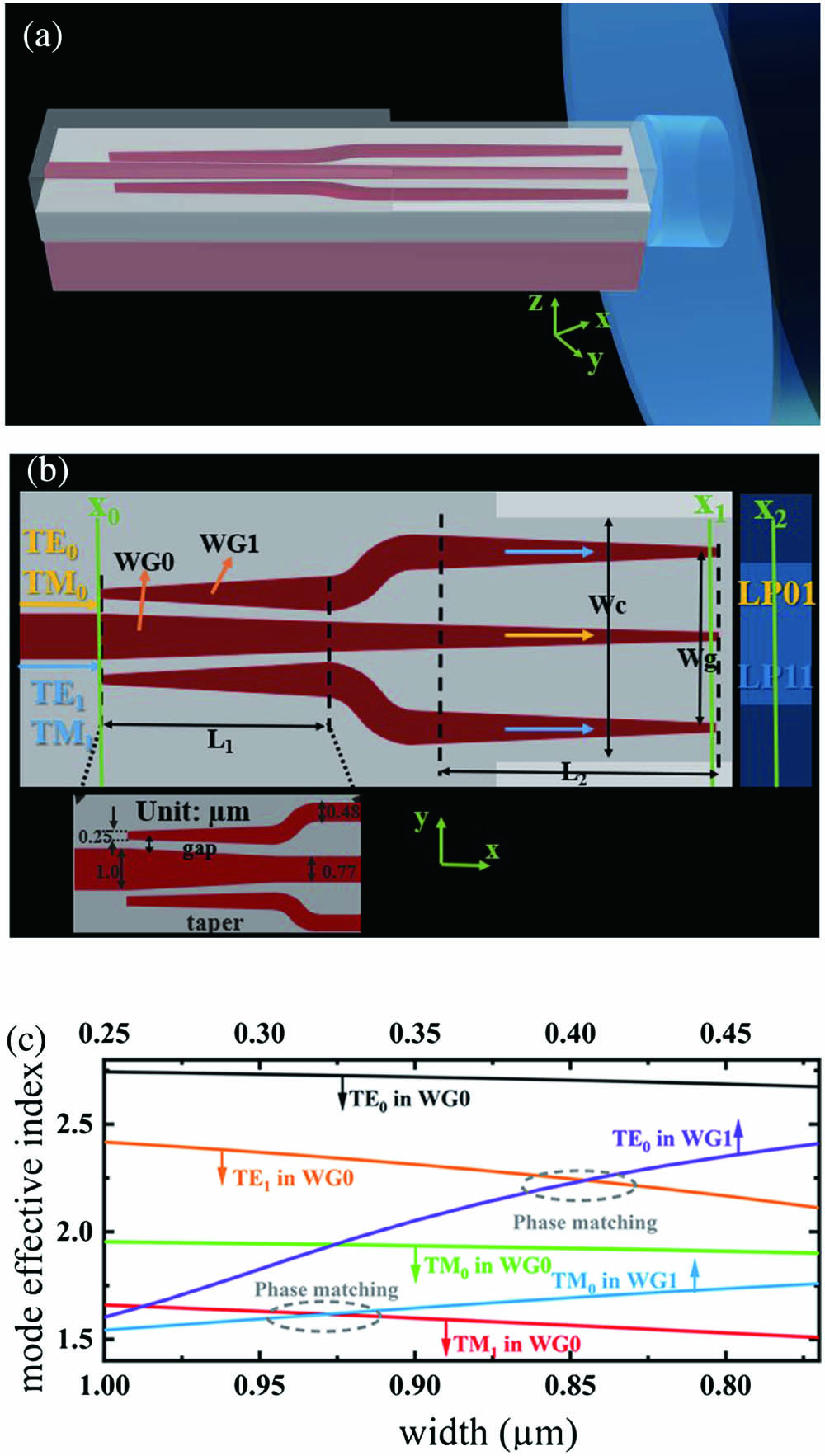

Figure 1(a) presents the schematic of the designed FMEC, which consists of a

![]()

Figure 1.Schematics of DMEC coupling with dual-mode fiber in (a) 3D view and (b) top view; the silicon waveguides are in red, and the silicon oxide layer is in gray. The modes conversion process is also demonstrated. (c) Effective refractive index of the modes in each waveguide (WG0/WG1) of the mode-evolution counter-taper with tapering width from 1 µm/0.25 µm to 0.77 µm/0.48 µm.

3. Simulation and Analysis

3.1. Optimization of FMEC

To analyze the performance of FMEC, the simulation is separated into two parts, the on-chip mode conversion from

![]()

Figure 2.(a) Mode conversion loss for the input TE0, TM0, TE1, and TM1 modes, respectively, (b) transmission loss for the TE0 and TM0 modes in inverse taper (L2), and (c) wavelength dependence of the transmission from ‘x0’–‘x1’.

However, the coupling between the triple-tip taper and FMF presents larger coupling loss, mainly caused by the mismatched mode fields between chip edge and FWF. In the simulation model, the diameters of core and cladding of the FMF are 14 µm and 125 µm, with the refractive indices of 1.4485 and 1.44402, respectively. The silicon substrate may cause more loss because of leaky modes, so we remove the substrate of the SOI wafer[

| Ref. | Number of Modes | Compatible with CMOS | Coupling Loss (dB) | Evaluation Method |

|---|---|---|---|---|

| [ | 2 | Yes | Numerical | |

| 2020 | ||||

| [ | 4 | No | Experimental | |

| 2017 | ||||

| [ | 1 | Yes | Numerical | |

| 2017 | Experimental | |||

| [ | 4 | No | No data | / |

| 2020 | ||||

| This work | 4 | Yes | Numerical | |

Table 1. Comparison of the Reported Multimode Edge Coupler and Coupler Proposed in This Work

![]()

Figure 3.Cross-sectional schematics of the edge coupling area: (a) x–y direction; (b) y–z direction.

![]()

Figure 4.(a) Simulated overlap integral of mode field between the FMF and SiO2 cladding, (b) simulated coupling loss for different Wg, (c) spatial mode coupling (from ‘x1’–‘x2’), and (d) the lateral alignment tolerance of coupling efficiency (CE) for spatial mode coupling.

The total coupling efficiency (CE) of the FMEC is 4.1 dB, 5.1 dB, 2.1 dB, and 2.9 dB for

![]()

Figure 5.(a) Total CE and (b) crosstalk of the FMEC in the span of 200 nm.

Figures 6(a)–6(p) show the simulated mode propagation for the input

![]()

Figure 6.Simulated electrical field mode profiles of (a) TE0, (b) TM0, (c) TE1, and (d) TM1 modes at position ‘x0’ in Fig.

3.2. Analysis of fabrication tolerance

In order to ensure reliability, Figs. 7(a) and 7(b) show the fabrication tolerance for on-chip conversion using EME by scanning the thickness and tapers waveguide width (which also causes gap distance variations), where the widths of both ends of the tapers vary simultaneously. Compared with that of high-order modes, the loss of input fundamental modes is negligible, so we only consider the conversion loss variations of the input TE1 and TM1 modes under the different fabrication error. The calculated conversion losses are always below 0.42 dB, as long as the waveguide width and thickness are controlled within the fabrication error variations of

![]()

Figure 7.Fabrication tolerance to deviation (a) of the waveguide width and thickness for TE1 input mode, (b) of the waveguide width and thickness for TM1 input mode, (c) of the tip width.

4. Conclusions

We design a compact, low loss, broadband, and fabrication-tolerant silicon photonic FMEC based on mode-evolution counter-tapers and a triple-tip inverse taper, serving as a bridge between the FMF and multimode chip, so that the input

References

[1] C. Sun, M. T. Wade, Y. Lee, J. S. Orcutt, L. Alloatti, M. S. Georgas, A. S. Waterman, J. M. Shainline, R. R. Avizienis, S. Lin, B. R. Moss, R. Kumar, F. Pavanello, A. H. Atabaki, H. M. Cook, A. J. Ou, J. C. Leu, Y. H. Chen, K. Asanovic, R. J. Ram, M. A. Popovic, V. M. Stojanovic. Single-chip microprocessor that communicates directly using light. Nature, 528, 534(2015).

[2] H. Ma, H. Yang, B. Tang, M. Wei, J. Li, J. Wu, P. Zhang, C. Sun, L. Li, H. Lin. Passive devices at 2 µm wavelength on 200 mm CMOS-compatible silicon photonics platform. Chin. Opt. Lett., 19, 071301(2021).

[3] C. Alonso-Ramos, A. Ortega-Monux, I. Molina-Fernandez, P. Cheben, L. Zavargo-Peche, R. Halir. Efficient fiber-to-chip grating coupler for micrometric SOI rib waveguides. Opt. Express, 18, 15189(2010).

[4] C. Li, D. Liu, D. Dai. Multimode silicon photonics. Nanophotonics, 8, 227(2019).

[5] Y. Lai, Y. Yu, S. Fu, J. Xu, P. Shum, X. Zhang. Compact double-part grating coupler for higher-order mode coupling. Opt. Lett., 43, 3172(2018).

[6] Z. Yu, Z. Ju, X. Zhang, Z. Meng, F. Yin, K. Xu. High-speed multimode fiber imaging system based on conditional generative adversarial network. Chin. Opt. Lett., 19, 081101(2021).

[7] B.-T. Lee, S.-Y. Shin. Mode-order converter in a multimode waveguide. Opt. Lett., 28, 1660(2003).

[8] Y. Kawaguchi, K. Tsutsumi. Mode multiplexing and demultiplexing devices using multimode interference couplers. Electron. Lett., 38, 1701(2002).

[9] W. Lu, L. Chang, X. Ren, D. Li, Z. Pan, M. Cheng, D. Liu, M. Zhang. Ultra-compact mode (de) multiplexer based on subwavelength asymmetric Y-junction. Opt. Express, 26, 8162(2018).

[10] W. Shen, J. Du, J. Xiong, L. Ma, Z. He. Silicon-integrated dual-mode fiber-to-chip edge coupler for 2 × 100 Gbps/lambda MOM optical interconnection. Opt. Express, 28, 33254(2020).

[11] B. Wohlfeil, G. Rademacher, C. Stamatiadis, K. Voigt, L. Zimmermann, K. Petermann. A two-dimensional fiber grating coupler on SOI for mode division multiplexing. IEEE Photon. Technol. Lett., 28, 1241(2016).

[12] A. M. J. Koonen, H. Chen, D. Van, O. Raz. Silicon photonic integrated mode multiplexer and demultiplexer. IEEE Photon. Technol. Lett., 24, 1961(2012).

[13] P. C. Kuo, Y. Tong, C. Chow, J. Tsai, Y. Liu, C. Yeh, H. Tsang. 4.36 Tbit/s silicon chip-to-chip transmission via few-mode fiber (FMF) using 2D sub-wavelength grating couplers. 2021 Optical Fiber Communications Conference and Exhibition (OFC)(2021).

[14] Y. Tong, W. Zhou, X. Wu, H. K. Tsang. Efficient mode multiplexer for few-mode fibers using integrated silicon-on-insulator waveguide grating coupler. IEEE J. Quantum Electron., 56, 8400107(2020).

[15] Y. Wu, K. Chiang. Ultra-broadband mode multiplexers based on three-dimensional asymmetric waveguide branches. Opt. Lett., 42, 407(2017).

[16] O. A. J. Gordillo, U. D. Dave, M. Lipson. Bridging between Si and few-mode fiber higher order modes. Conference on Lasers and Electro-Optics, SM2O.6(2020).

[17] Y. Lai, Y. Yu, S. Fu, J. Xu, P. P. Shum, X. Zhang. Efficient spot size converter for higher-order mode fiber-chip coupling. Opt. Lett., 42, 3702(2017).

[18] Z. Li, Y. Lai, Y. Yu, X. Zhang. Reconfigurable fiber-chip mode converter with efficient multi-mode coupling function. IEEE Photon. Technol. Lett., 32, 371(2020).

[19] A. F. Milton, W. K. Burns. Tapered velocity couplers for integrated optics: design. Appl. Opt., 14, 1207(1975).

[20] N. Riesen, J. D. Love. Tapered velocity mode-selective couplers. J. Lightwave Technol., 31, 2163(2013).

[21] J. V. Galán, P. Sanchis, G. Sánchez, J. Martí. Polarization insensitive low-loss coupling technique between SOI waveguides and high mode field diameter single-mode fibers. Opt. Express, 15, 7058(2007).

[22] M. Wood, P. Sun, R. M. Reano. Compact cantilever couplers for low-loss fiber coupling to silicon photonic integrated circuits. Opt. Express, 20, 164(2012).

[23] J. Wang, Y. Xuan, M. Qi, H. Huang, Y. Li, M. Li, X. Chen, Z. Sheng, A. Wu, W. Li, X. Wang, S. Zou, F. Gan. Broadband and fabrication-tolerant on-chip scalable mode-division multiplexing based on mode-evolution counter-tapered couplers. Opt. Lett., 40, 1956(2015).

[24] V. H. Nguyen, I. K. Kim, T. J. Seok. Low-loss and broadband silicon photonic 3-dB power splitter with enhanced coupling of shallow-etched rib waveguides. Appl. Sci., 10, 4507(2020).

[25] J. Zhu, Q. Chao, H. Huang, Y. Zhao, Y. Li, L. Tao, X. She, H. Liao, R. Huang, Z. Zhu, X. Liu, Z. Sheng, F. Gan. Compact, broadband, and low-loss silicon photonic arbitrary ratio power splitter using adiabatic taper. Appl. Opt., 60, 413(2021).

[26] Z. Yao, Y. Wan, Y. Zhang, X. Ma, Z. Zheng. Broadband high-efficiency triple-tip spot size converter for edge coupling with improved polarization insensitivity. Opt. Commun., 475, 126301(2020).

[27] J. Wang, Y. Xuan, C. Lee, B. Niu, L. Liu, G. Liu, M. Qi. Low-loss and misalignment-tolerant fiber-to-chip edge coupler based on double-tip inverse tapers. 2016 Optical Fiber Communications Conference and Exhibition (OFC)(2016).

[28] X. Mu, S. L. Wu, L. R. Cheng, H. Y. Fu. Edge couplers in silicon photonic integrated circuits: a review. Appl. Sci., 10, 29(2020).

Set citation alerts for the article

Please enter your email address