Bo-Wu WANG, Wei-Hua YU, Yan-Fei HOU, Qin YU, Yan SUN, Wei CHENG, Ming ZHOU. A 33~170 GHz cascode amplifier based on InP DHBT technology[J]. Journal of Infrared and Millimeter Waves, 2023, 42(2): 197

Search by keywords or author

- Journal of Infrared and Millimeter Waves

- Vol. 42, Issue 2, 197 (2023)

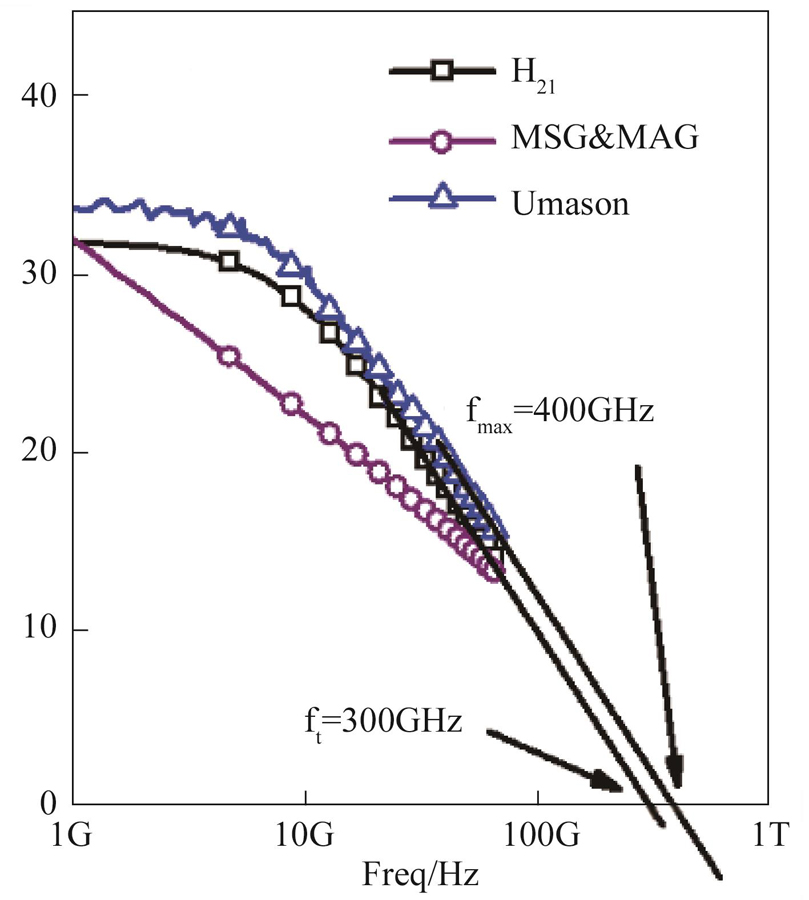

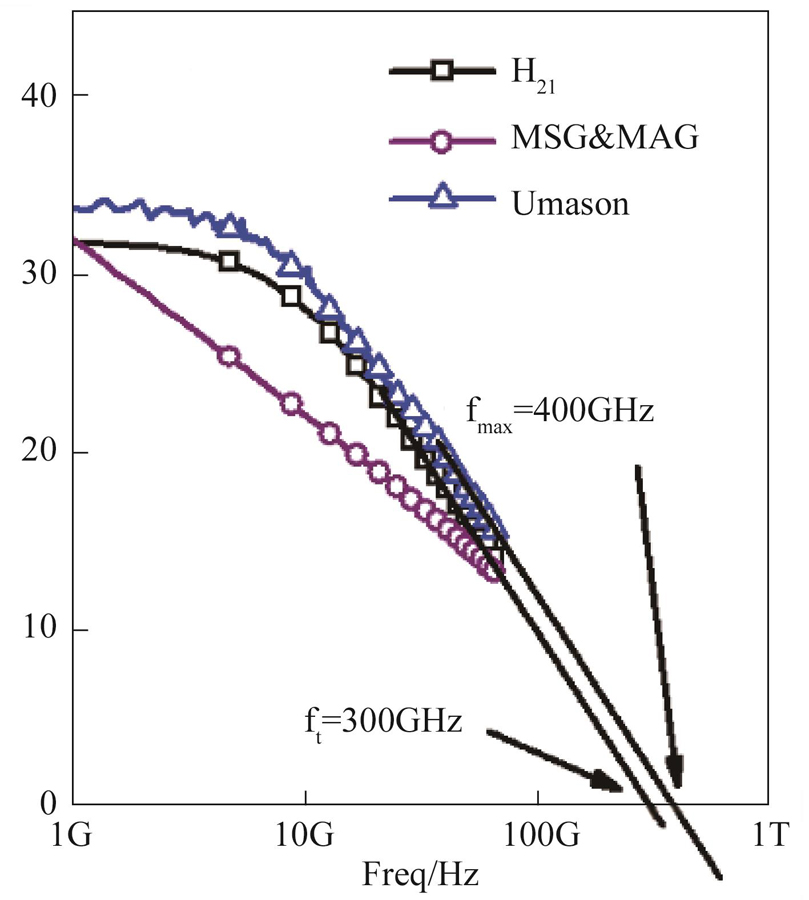

Fig. 1. The fT and fmaxof the transistor

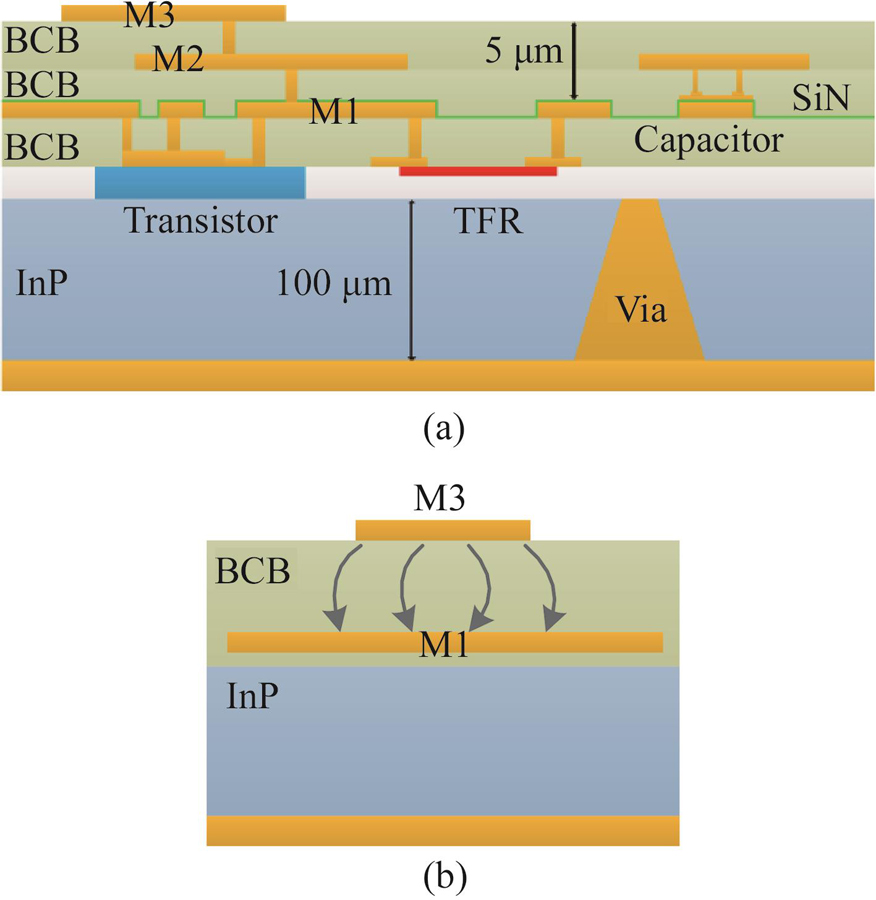

Fig. 2. Schematic cross-sectional view of (a) multilayer interconnect, and (b) thin-film microstrip lines

Fig. 3. Block diagram of the typical cascode amplifier

Fig. 4. Circuit topology for the wide band cascode amplifier

Fig. 5. Impedance matching Smith chart and the network schematic

Fig. 6. Chip photograph of the cascode amplifier MMIC. Size:1.0 mm × 0.8 mm

Fig. 7. Measured and simulated S-parameters of the broadband amplifier MMIC On-wafer bias:Vb1=1.5 V,Vb2/Vc=2.5 V

Fig. 8. Output power measured results

| ||||||||||||||||||||||||||||||||||||||||||||

Table 1. Layer structure of the InGaAs/InP DHBT

|

Table 2. State-of-the-art of ultra-broadband amplifier

Set citation alerts for the article

Please enter your email address