Nicolò Zagni, Manuel Fregolent, Andrea Del Fiol, Davide Favero, Francesco Bergamin, Giovanni Verzellesi, Carlo De Santi, Gaudenzio Meneghesso, Enrico Zanoni, Christian Huber, Matteo Meneghini, Paolo Pavan. Physical insights into trapping effects on vertical GaN-on-Si trench MOSFETs from TCAD[J]. Journal of Semiconductors, 2024, 45(3): 032501

Search by keywords or author

- Journal of Semiconductors

- Vol. 45, Issue 3, 032501 (2024)

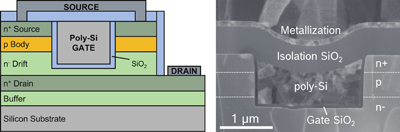

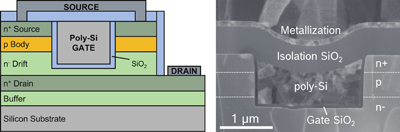

Fig. 1. (Color online) (a) Schematic 2-D view of the pseudo-vertical GaN-on-Si TMOS under study in this work. (b) TEM image of a FIB lamella taken from the gate trench.

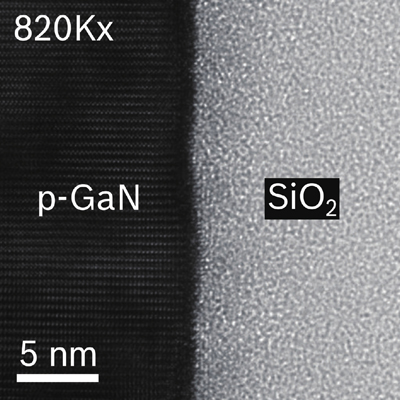

Fig. 2. HRTEM image at 820 Kx magnification of the gate interface in the channel region on the etched sidewall for device B.

Fig. 3. (Color online) Experimentally measured ID−VGS of device A (a) and B (b). Continuous lines with squares (dashed lines with circles) are the forward and backward sweeps, respectively.

Fig. 4. (Color online) VT time evolution during (a) stress and (b) recovery experiments on device B. Different stress voltages (VGS,STR) were applied (see legend), whereas the recovery voltage (VGS,REC) was always 0 V.

Fig. 5. (Color online) VT time evolution during (a) stress (VGS,STR = 30 V) and (b) recovery (VGS,REC = 0 V) experiments on device A and different temperatures (see legend). No clear dependence of VT shift on temperature was found.

Fig. 6. (Color online) (a) Interface and (b) border trap densities vs trap energy (ET) referred to the conduction band edge of GaN (EC) employed in the simulations of device A (for device B, all parameters were the same except for the concentrations, see Table 1 ). ECNL in (a) indicates the assumed charge neutrality level that discriminates between acceptor-like and donor-like interface traps[22]. Border traps are only acceptor states.

Fig. 7. (Color online) Simulated ID−VGS of device A (a) and B (b). Continuous (dashed) lines are the forward and backward sweeps, respectively.

Fig. 8. (Color online) (a) Simulated band diagram (device B) plotted along the lateral dimension perpendicular to the vertical current flow for different VGS (see legend). (b) Corresponding trapped charge in border traps (nBT) in the gate oxide (SiO2) and free electron density (n) in the channel (GaN).

Fig. 9. (Color online) (a) Simulated band diagram (device B) plotted along the lateral dimension perpendicular to the vertical current flow for different VGS (see legend). (b) Corresponding trapped charge in border traps (nBT) in the gate oxide (SiO2) and free electron density (n) in the channel (GaN).

Fig. 10. (Color online) Hysteresis in the ID−VGS (see text for definition) of device A and B. Both experimental data and simulation results are shown. Dashed lines are linear fitting of data points. The ≈75% hysteresis reduction at VGS,max = 40 V of device B compared to A is reproduced by simulations by reducing oxide trap concentration by the same amount.

Fig. 11. (Color online) Sensitivity of H to border trap density (DBT) with the simulation setup calibrated on device B. The experimental data points at VGS,max = 40 V are shown for reference.

Fig. 12. (Color online) Sensitivity of SS (obtained on the upward sweep) to interface trap density (DIT) with the simulation setup calibrated on device B. The experimental data points at VGS,max = 40 V are shown for reference. The asymptotic theoretical limit (i.e., for a trap-free interface determined only by the depletion capacitance, CD, and oxide capacitance, Cox) is also indicated.

| |||||||||||||||||||||||||

Table 1. Trap-related simulation parameters (Device A/Device B).

Set citation alerts for the article

Please enter your email address