[1] H H Radamson. CMOS past, present and future. Woodhead Publishing Series in Electronic and Optical Materials(2018).

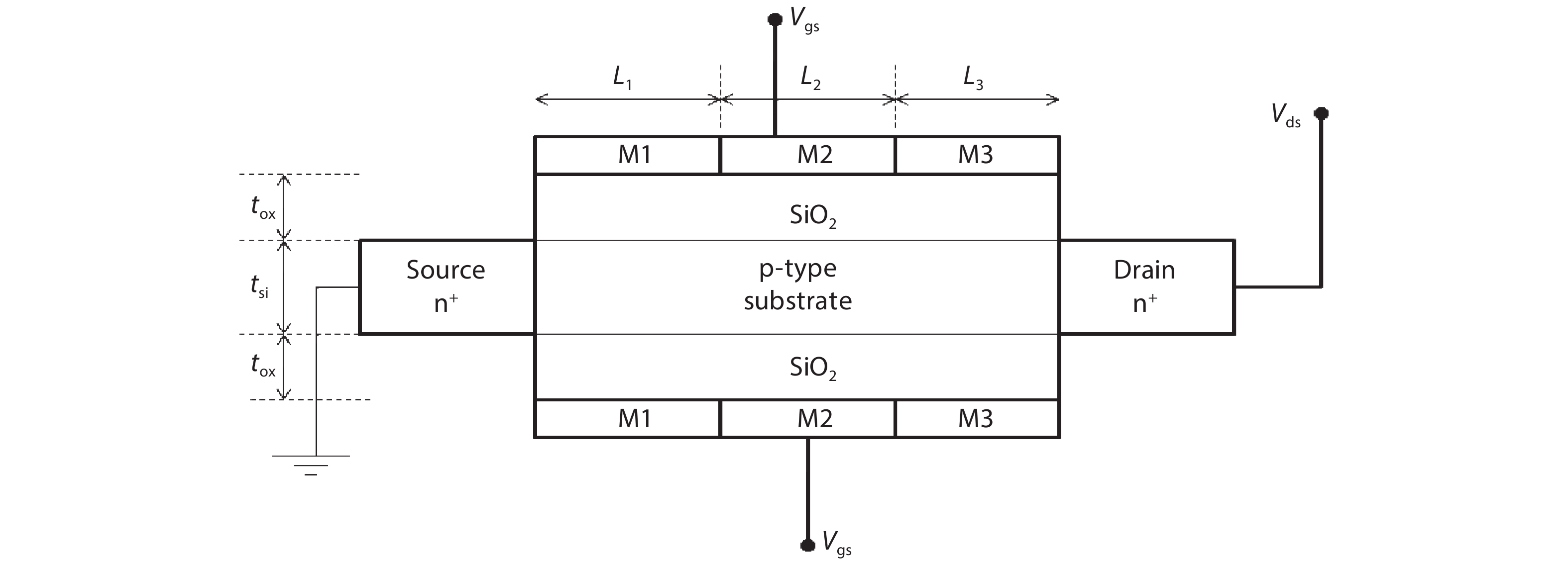

[2] B Buvaneswari, N B Balamurugan. 2D analytical modeling and simulation of dual material DG MOSFET for biosensing application. Int J Electron Commun, 99, 193(2019).

[3] V M Srivastava, K S Yadav, G Singh. Design and performance analysis of double-gate MOSFET over single-gate MOSFET for RF switch. Microelectron J, 43, 873(2012).

[4] J P Colinge. Multi-gate SOI MOSFETs. Microelectron Eng, 84, 2071(2007).

[5] E Gili, V D Kunz, C H D Groot et al. Single, double and surround gate vertical MOSFETs with reduced parasitic capacitance. Solid-State Electron, 48, 511(2004).

[6] J H K Verma, Y Pratap, S Haldar et al. Capacitance modeling of gate material engineered cylindrical/surrounded gate MOSFETs for sensor applications. Superlattices Microstruct, 88, 271(2015).

[7] I M Tienda-Luna, J B Roldan, F G Ruiz et al. An analytical mobility model for square gate-all-around MOSFETs. Solid-State Electron, 90, 18(2013).

[8] F Djeffal, H Ferhati, T Bentrcia. Improved analog and RF performances of gate-all-around junctionless MOSFET with drain and source extensions. Superlattices Microstruct, 90, 193(2016).

[9] A Sarkar, A K Das, S De et al. Effect of gate engineering in double-gate MOSFETs for analog/RF applications. Microelectron J, 43, 873(2012).

[10] F Nasri, M F B Aissa, M H Gazzah et al. 3D thermal conduction in ananoscale tri-Gate MOSFET based on single-phase-lag model. Appl Therm Eng, 91, 647(2015).

[11] J E Pakaree, V M Srivastava. Realization with fabrication of double-gate MOSFET based differential amplifier. Microelectron J, 91, 70(2019).

[12] S Abhinav. Reliability analysis of junction-less double gate (JLDG) MOSFET for analog/RF circuits for high linearity applications. Microelectron J, 64, 60(2017).

[13] V M Srivastava, K S Yadav, G Singh. Design and performance analysis of cylindrical surrounding double-gate MOSFET for RF switch. Microelectron J, 42, 1124(2011).

[14] W H Ku. Unilateral gain and stability criterion of active two-ports in terms of scattering parameters. Proc IEEE, 54, 1617(1966).

[15] K Sivasankaran, D Kannadassan, K Seetaram et al. Bias and geometry optimization of silicon nanowire transistor: radio frequency stability perspective. Micro Optic Technol Lett, 54, 2114(2012).

[16] A A Orouji, S Heydari, M Fathipour. Double step buried oxide (DSBO) SOI-MOSFET: A proposed structure for improving self-heating effects. Physica E, 41, 1665(2009).

[17] I Kwona, H I Kwonb, H I Cho. Development of high temperatureoperation silicon based MOSFET for harsh environment application. Results Phys, 11, 475(2018).

[18]

[19] R Narang, M Saxena, M Gupta. Modeling of gate underlap junctionless double gate MOSFET as bio-sensor. Mater Sci Semicond Process, 71, 240(2017).

[20] A Kumar, M M Tripathi, R Chaujar. Comprehensive analysis of sub-20 nm black phosphorus based junctionless-recessed channel MOSFET for analog/RF applications. Superlattices Microstruct, 116, 171(2018).

[21] F Djeffal, N Lakhdar, A Yousfi. An optimized design of 10-nm-scale dual-material surrounded gate MOSFETs for digital circuit applications. Physica E, 44, 339(2011).

[22] V Pathak, G Saini. A Graded channel dual-material gate junctionless MOSFET for analog applications. Proced Comput Sci, 125, 825(2018).

[23] R Narang, M Saxena, M Gupta. Investigation of dielectric modulated (DM) double gate (DG) junctionless MOSFETs for application as a biosensors. Superlattices Microstruct, 85, 557(2015).

[24] Y S Pang, J R Brews. Design of 0.1-

[25] A A Orouji, M J Kumar. Nanoscale SOI MOSFETs with electrically induced source/drain extension: Novel attributes and design considerations for suppressed short-channel effects. Superlattices Microstruct, 39, 395(2006).

[26] A Pal, A Sarkar. Analytical study of dual material surrounding gate MOSFET to suppress short-channel effects (SCEs). Eng Sci Technol, 17, 205(2014).

[27] E Chebaki, F Djeffal, H Ferhati et al. Improved analog/RF performance of double gate junctionless MOSFET using both gate material engineering and drain/source extensions. Superlattices Microstruct, 92, 80(2016).

[28] Y Wang, Y Tang, L L Sun et al. High performance of junctionless MOSFET with asymmetric gate. Superlattices Microstruct, 97, 2016(2016).

[29] B Awadhiya, P N Kondekar, A D Meshram. Understanding negative differential resistance and region of operation in undoped HfO2-based negative capacitance field effect transistor. Appl Phys A, 125, 427(2019).

[30] A Kumar, N Gupta, R Chaujar. TCAD RF performance investigation of transparent gate recessed channel MOSFET. Microelectron J, 49, 36(2016).

[31] V K Mishra, R K Chauhan. Efficient layout design of junctionless transistor based 6-T SRAM cell using SOI technology. ECS J Solid State Sci Technol, 9, 456(2018).

[32] N C Roy, A Gupta, S Rai. Analytical surface potential modeling and simulation of junction-less double gate (JLDG) MOSFET for ultra-low power analog/RF circuits. Microelectron J, 46, 916(2015).

[33] G K Saramekala, A Santra, S Dubey et al. An analytical threshold voltage model for a short-channel dual-metal-gate (DMG) recessed-source/drain (Re-S/D) SOI MOSFET. Superlattices Microstruct, 60, 580(2013).

[34] S L Tripathi, R Patel, V K Agrawal. Low leakage pocket junction-less DGTFET with bio sensing cavity region. Turk J Electr Eng Comput Sci, 27, 2466(2019).