Xing Li, Lei Zhou. A survey of high-speed high-resolution current steering DACs[J]. Journal of Semiconductors, 2020, 41(11): 111404

Search by keywords or author

- Journal of Semiconductors

- Vol. 41, Issue 11, 111404 (2020)

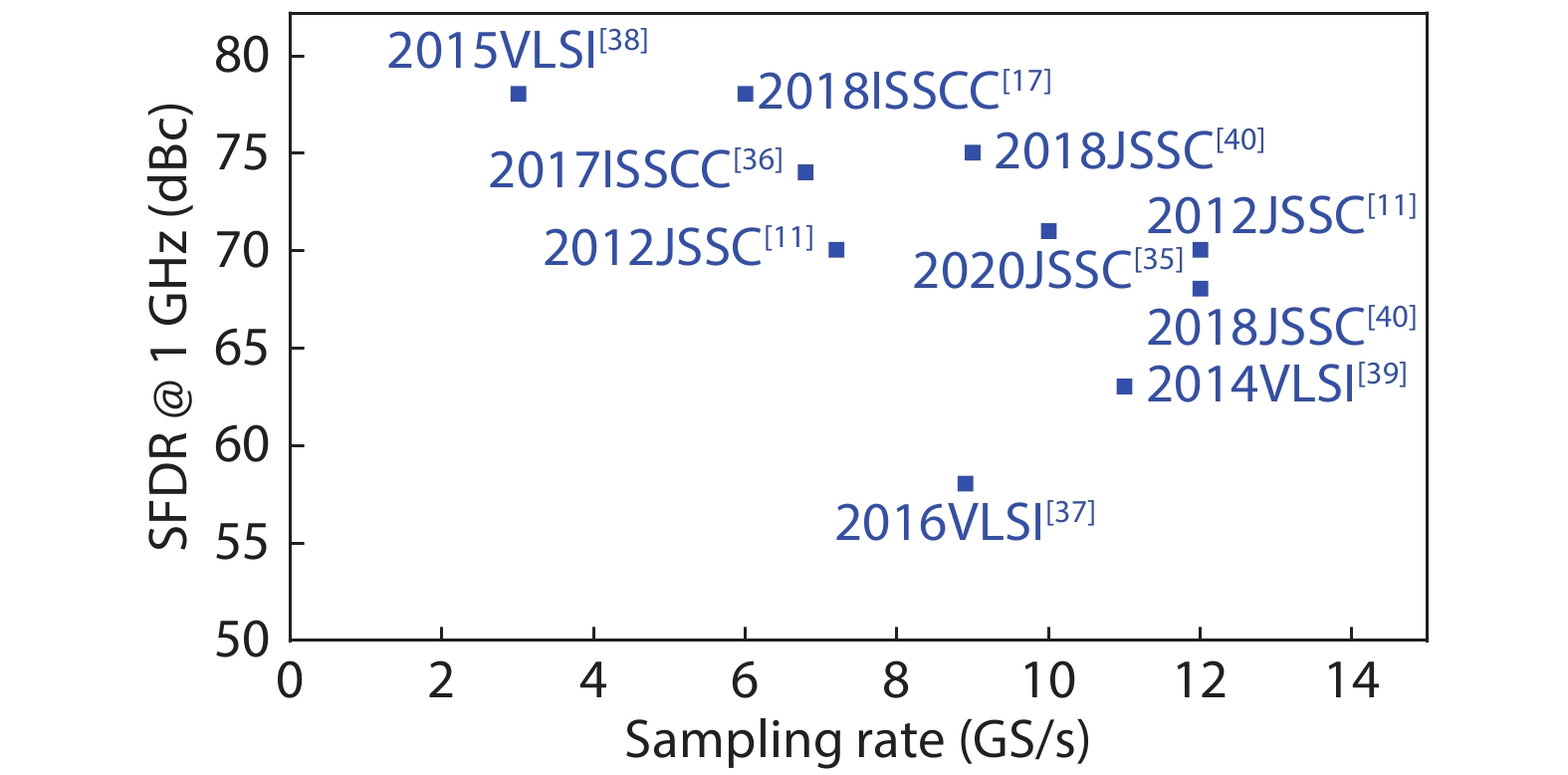

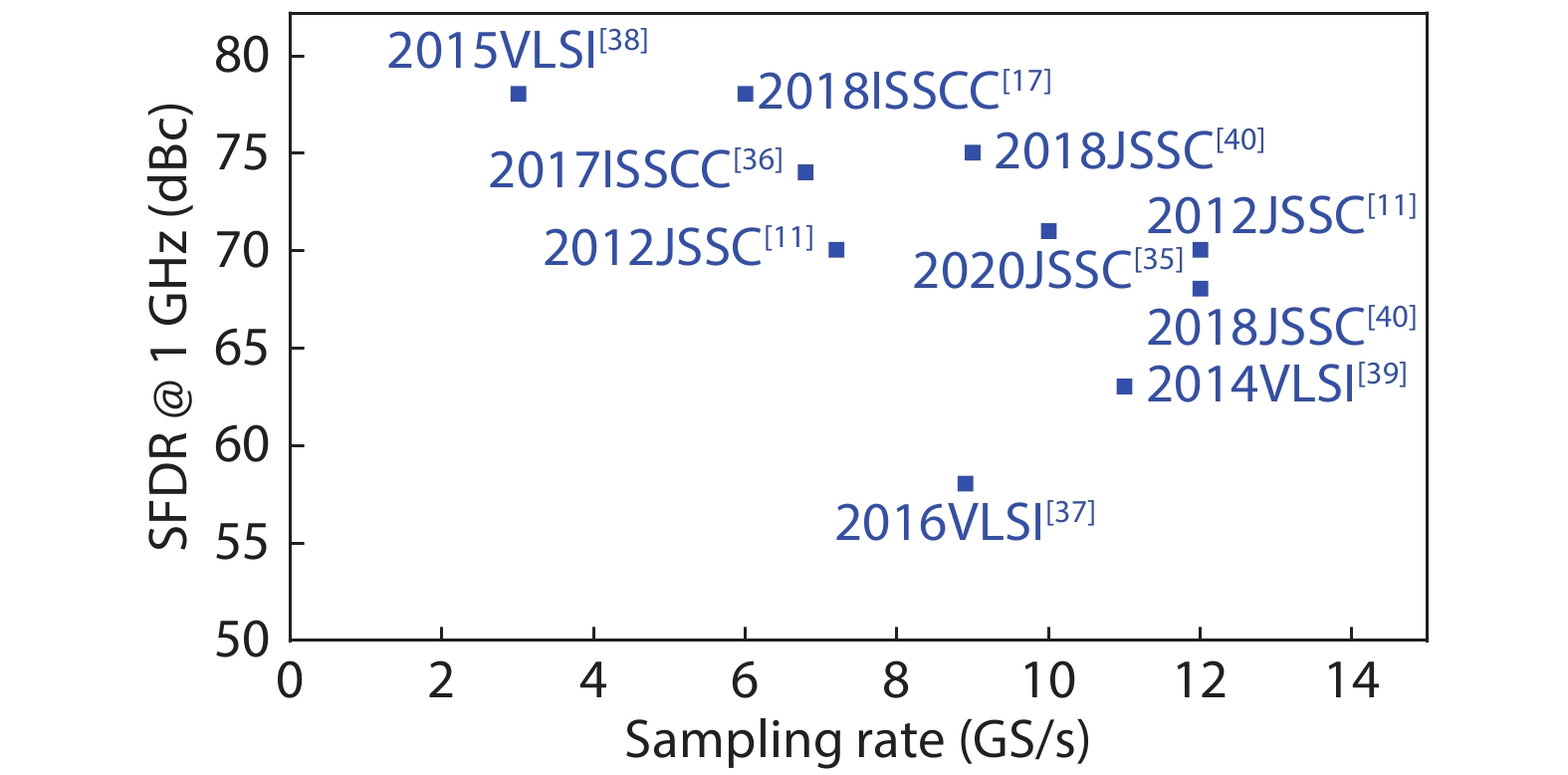

Fig. 1. (Color online) Performance comparison of state-of-the-art DACs: SFDR@1GHz vs. sampling rate.

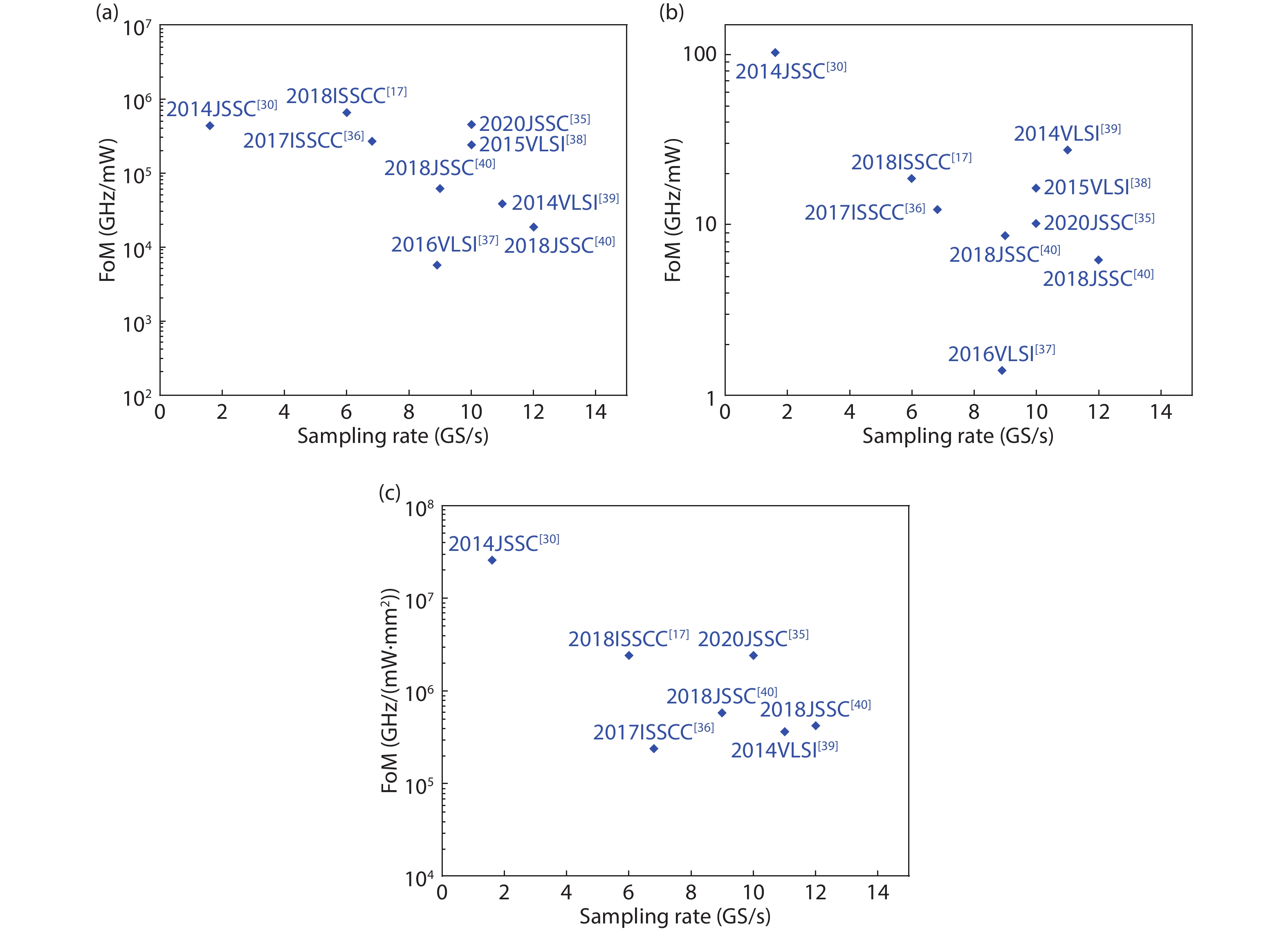

Fig. 2. (Color online) Performance comparison of state-of-the-art DACs: (a) FoM1, (b) FoM2, (c) FoM3 versus sampling rate.

Fig. 3. (Color online) Block diagram of a high-speed high-resolution current steering DAC with a typical switching current cell.

Fig. 4. A typical switching current cell proposed in Ref. [21 ].

Fig. 5. Quad-switching current cell with switch cascodes reported in Ref. [38 ].

Fig. 6. A simplified quad-switch cell proposed in Ref. [34 ].

Fig. 7. RZ current cell with resampling switches proposed in Ref. [11 ].

Fig. 8. (Color online) Magnitude of the frequency response for NRZ, RZ, and MRZ waveforms reported in Ref. [53 ].

Fig. 9. A typical fast latch proposed in Ref. [21 ]

Fig. 10. High-speed latch presented in Ref. [57 ].

Fig. 11. DAC output stack, with the switch driver proposed in Ref. [37 ].

Fig. 12. Block diagram of dummy trigger proposed in Ref. [56 ].

Fig. 13. Master-slave latch presented in Ref. [58 ].

Fig. 14. Double-edge current switch driver with enhanced reset circuit reported in Ref. [59 ].

Fig. 15. Two-parameter calibration loop configuration and CAL_DACs proposed in Ref. [28 ].

Fig. 16. Conceptual block diagram of a dual-rate hybrid DAC architecture proposed in Ref. [49 ].

Fig. 17. OIC technique with compensation resistor proposed in Ref. [35 ].

|

Table 1. Performance summary and comparison with state-of-the-art high-speed high-resolution DACs.

| ||||||||||||||||

Table 2. Detailed definitions of DAC FoMs.

|

Table 3. INL, DNL and temperature drift summary of proposed foreground calibration techniques.

Set citation alerts for the article

Please enter your email address