Author Affiliations

1School of Information Science and Technology, ShanghaiTech University, Shanghai 201210, China2Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, Shanghai 200050, China3University of Chinese Academy of Sciences, Beijing 100049, China4Intel Singapore, Singapore 339510, Singaporeshow less

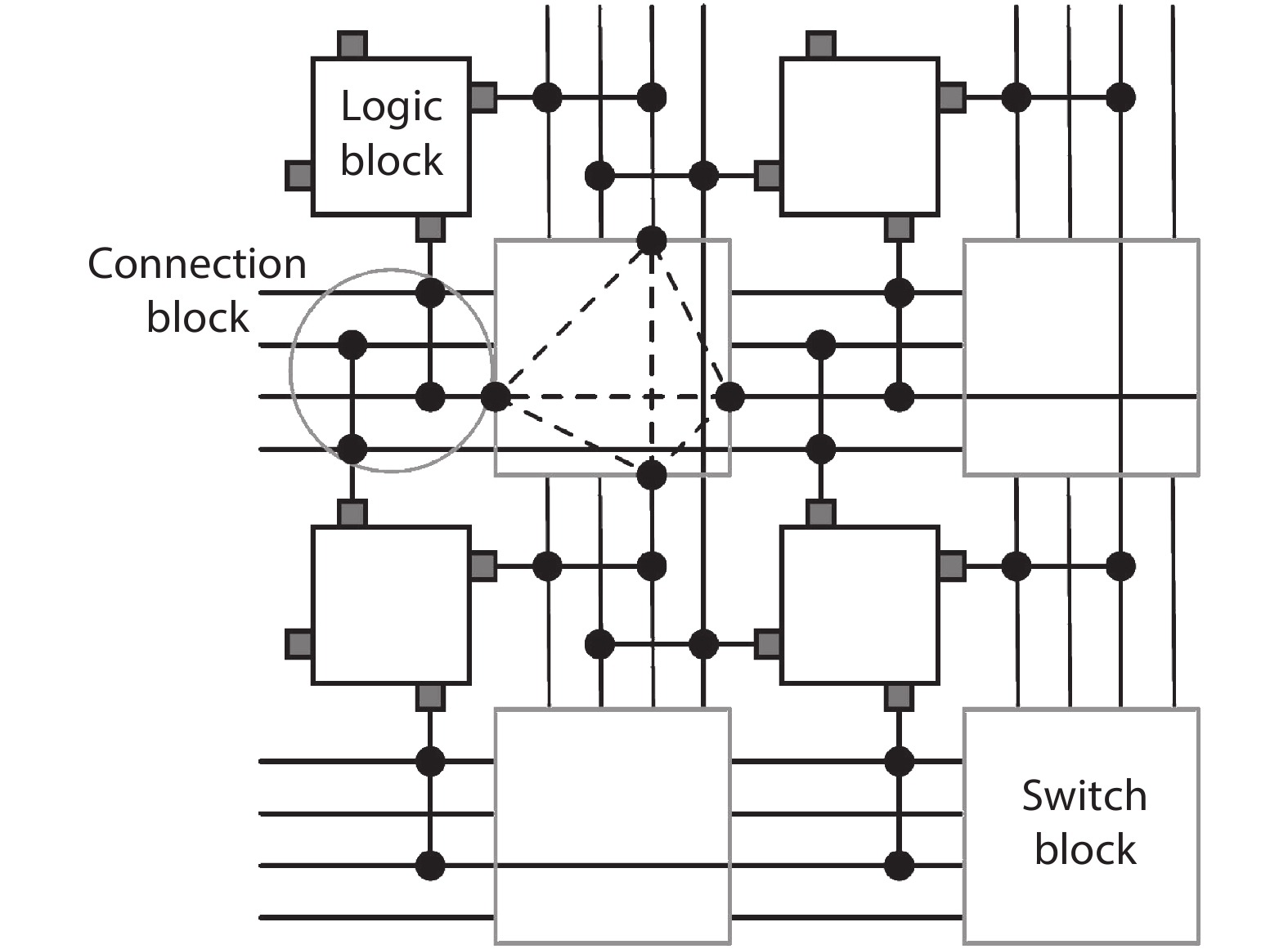

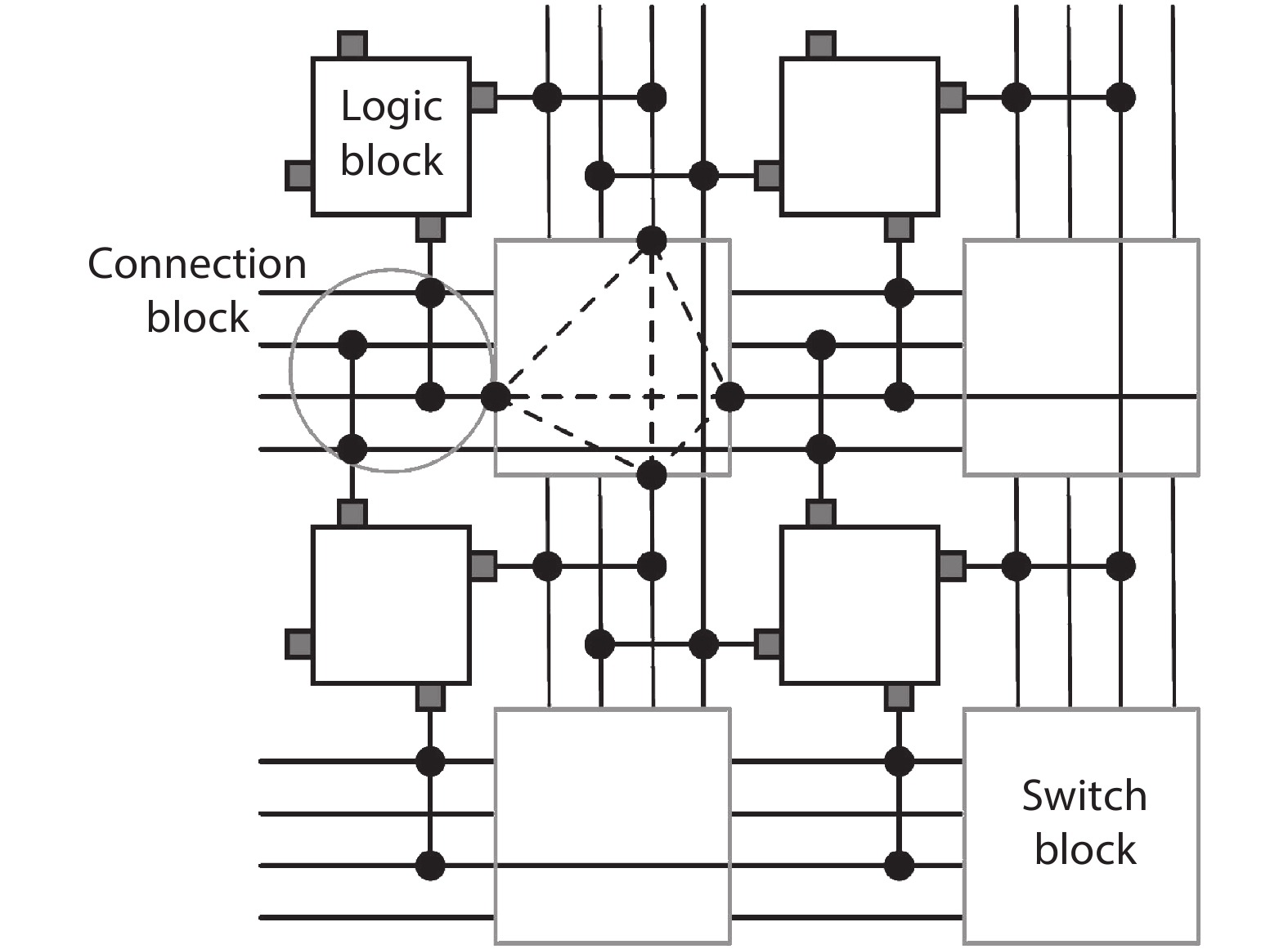

Fig. 1. Island-style architecture, which is the base of TM-ARCH with the time-multiplexed interconnects.

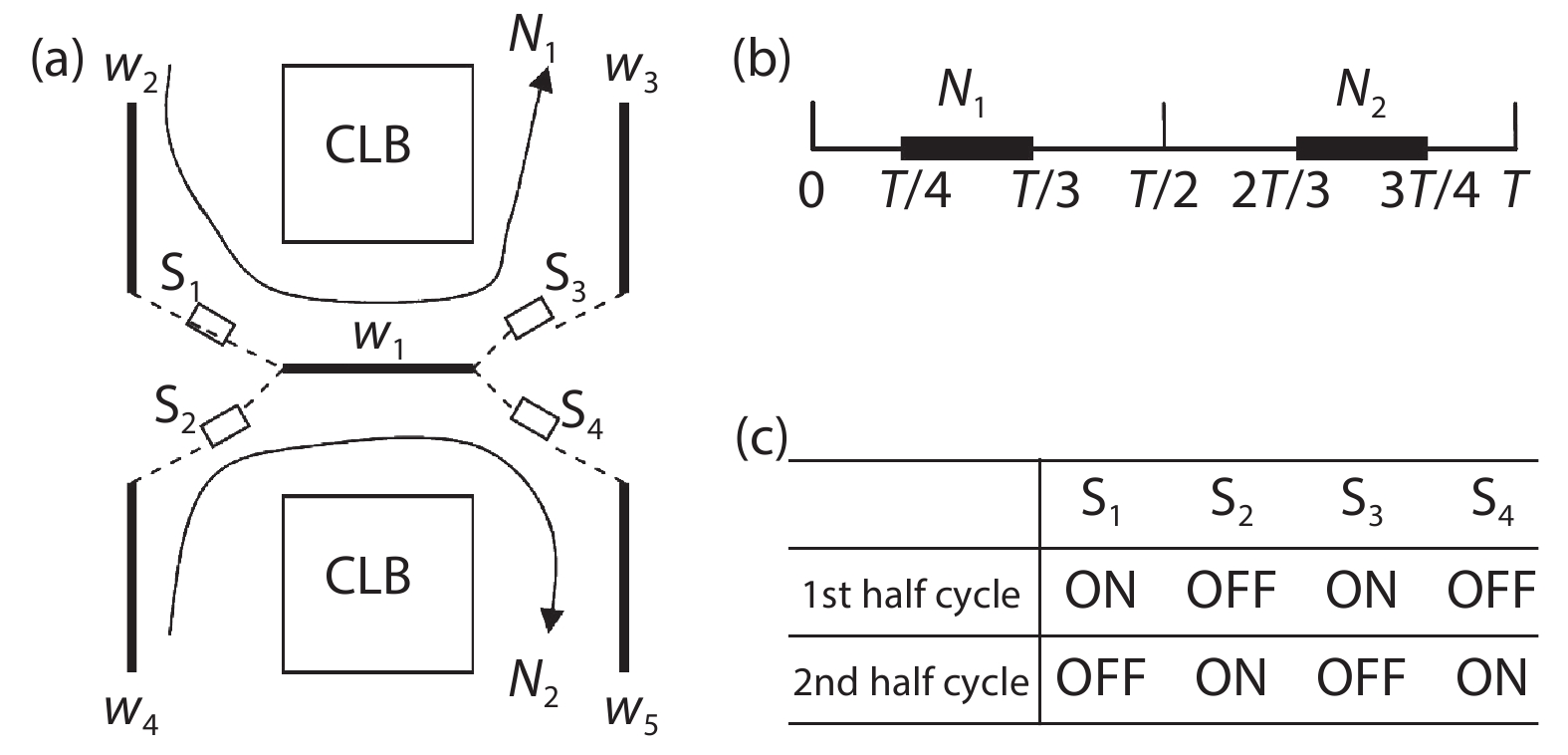

Fig. 2. (a) Signals

and

occupy a wire at different time. (b) In time domain,

and

do not overlap. (c) TM switches’ different states.

Fig. 3. Routing resource graph of TM-ARCH architecture.

Fig. 4. Pseudo code for computing the occupation bitmaps.

Fig. 5. Pseudo code for computing the congestion cost.

Fig. 6. Pseudo code for computing the congestion cost.

Fig. 7. (Color online) The TM-ARCH and TM-ROUTER evaluation framework.

| Routing schedule | Value |

|---|

| 0.5 in the first and the second routing iteration; 1.3 times its previous value from the third iteration onwards. | | 1.0 for all the iterations. |

|

Table 1. Resource utilization of the system.

| Feature parameter | Value/specification |

|---|

| LUT size | 4 | | Logic block size | 10 | | Logic block inputs | 22 | | Amount of bias between horizontal and vertical channels | No bias | | Uniformity of routing channels in the same direction | Uniform | | Aspect ratio | 1 : 1 (Assuming square logic blocks) | | Segmentation distribution | 100% length 4 wires | | Switch types used | Uni-directional single driver switches | | Switch block topology | Wilton | | Switch block internal population | 100% | | Connection block internal population | 100% |

|

Table 2. Main Features of Baseline FPGA Architecture.

| Parameter | | | | | |

|---|

| Alu4 | 48 | 48 | 30 | 36 | 26 | | Apex2 | 62 | 62 | 36 | 34 | 22 | | Apex4 | 64 | 64 | 50 | 36 | 28 | | Bigkey | 44 | 44 | 32 | 32 | 30 | | Clma | 78 | 76 | 74 | 48 | 34 | | Des | 44 | 42 | 34 | 32 | 32 | | Diffeq | 38 | 36 | 34 | 32 | 30 | | Dsip | 38 | 36 | 30 | 30 | 30 | | Elliptic | 62 | 58 | 52 | N.A. | 34 | | Ex1010 | 74 | 74 | 60 | 40 | 34 | | Ex5p | 68 | 68 | 48 | 34 | 22 | | Frisc | 74 | 74 | 44 | 40 | 40 | | Misex3 | 54 | 54 | 42 | 26 | 22 | | Pdc | 90 | 90 | 128 | 60 | 70 | | S298 | 34 | 34 | 28 | 28 | 20 | | S38417 | 48 | 48 | 50 | 26 | 22 | | S38584.1 | 50 | 50 | 48 | 26 | 22 | | Seq | 60 | 60 | 48 | 26 | 22 | | Spla | 74 | 72 | N.A. | 52 | 34 | | Tseng | 46 | 46 | 40 | 34 | 32 | | Geo.Mean | 56 | 55 | 44 | 34 | 29 | | Reduction | – | –1.78% | –21.43% | –39.28% | –48.21% |

|

Table 3. Minimum channel width for different

values.

| Parameter | | | |

|---|

| 1st | 2nd | | 1st | 2nd | 3rd | 4th |

|---|

| Alu4 | 94.59 | 4.67 | | 56.04 | 29.64 | 4.19 | 0.45 | | Apex2 | 97.09 | 2.42 | | 67.82 | 25.32 | 2.17 | 0.21 | | Apex4 | 87.35 | 10.56 | | 28.13 | 56.96 | 9.45 | 1.00 | | Bigkey | 93.65 | 4.77 | | 61.57 | 28.13 | 4.77 | 0.00 | | Clma | 96.50 | 2.97 | | 68.86 | 25.69 | 2.83 | 0.12 | | Des | 90.08 | 9.15 | | 63.16 | 24.61 | 6.50 | 1.96 | | Diffeq | 95.97 | 3.80 | | 74.31 | 18.47 | 3.71 | 0.10 | | Dsip | 94.70 | 4.28 | | 59.70 | 31.89 | 4.04 | 0.18 | | Elliptic | 95.35 | 4.46 | | 87.51 | 7.36 | 3.65 | 0.73 | | Ex1010 | 90.04 | 8.67 | | 23.65 | 64.19 | 7.98 | 0.51 | | Ex5p | 82.63 | 14.85 | | 21.70 | 56.98 | 12.71 | 1.99 | | Frisc | 86.87 | 12.06 | | 68.23 | 18.50 | 10.58 | 1.41 | | Misex3 | 93.09 | 5.60 | | 52.19 | 33.60 | 4.64 | 0.80 | | Pdc | 95.09 | 4.36 | | 46.93 | 42.92 | 3.88 | 0.42 | | S298 | 85.82 | 13.48 | | 63.21 | 21.00 | 9.76 | 3.16 | | S38417 | 92.87 | 6.60 | | 65.09 | 24.77 | 5.83 | 0.67 | | S38584.1 | 97.41 | 1.88 | | 73.30 | 19.91 | 1.59 | 0.26 | | Seq | 97.50 | 2.20 | | 69.24 | 24.66 | 1.99 | 0.17 | | Spla | 95.98 | 3.60 | | 49.20 | 41.06 | 3.31 | 0.25 | | Tseng | 96.48 | 3.34 | | 88.49 | 6.82 | 2.35 | 0.73 | | Geo.Mean | 92.85 | 5.17 | | 55.83 | 26.19 | 4.49 | 0.51 |

|

Table 4. Percentages (%) of wire used in each individual microcycle for 20 benchmark circuits with

.

| Parameter | | | | | | | | | |

|---|

| | | | | | | | | | | | | |

|---|

| Alu4 | 58 | 3.31 | | 58 | 3.31 | | 36 | 3.31 | | 44 | 3.23 | | 32 | 3.45 | | Apex2 | 74 | 3.90 | | 74 | 3.90 | | 46 | 3.69 | | 44 | 3.69 | | 26 | 3.65 | | Apex4 | 76 | 3.80 | | 76 | 3.80 | | 58 | 3.13 | | 40 | 3.20 | | 32 | 3.20 | | Bigkey | 52 | 1.80 | | 52 | 1.87 | | 38 | 1.80 | | 38 | 1.80 | | 38 | 1.80 | | Clma | 94 | 6.74 | | 94 | 6.74 | | 88 | 6.63 | | 58 | 6.70 | | 44 | 6.70 | | Des | 52 | 2.86 | | 48 | N.A. | | 40 | 2.78 | | 38 | 2.85 | | 38 | 2.85 | | Diffeq | 46 | 4.44 | | 44 | 4.51 | | 40 | 4.37 | | 38 | 4.44 | | 36 | 4.37 | | Dsip | 46 | 1.73 | | 44 | 1.73 | | 36 | 1.80 | | 36 | 1.80 | | 36 | 1.80 | | Elliptic | 74 | 6.22 | | 70 | 5.52 | | 62 | 5.66 | | N.A. | N.A. | | 40 | 5.37 | | Ex1010 | 88 | 4.42 | | 88 | 4.42 | | 72 | 4.49 | | 48 | N.A. | | 40 | 4.42 | | Ex5p | 82 | 3.55 | | 82 | 3.55 | | 58 | 3.34 | | 40 | 3.23 | | 26 | 3.37 | | Frisc | 88 | 7.63 | | 88 | 7.63 | | 52 | 7.42 | | 48 | 7.42 | | 48 | 7.49 | | Misex3 | 64 | 3.13 | | 64 | 3.13 | | 50 | 3.06 | | 32 | 3.20 | | 26 | 3.27 | | Pdc | 108 | 5.26 | | 108 | 5.26 | | 154 | 4.49 | | 72 | 4.49 | | 84 | 4.49 | | S298 | 40 | N.A. | | 40 | N.A. | | 34 | 6.14 | | 34 | 6.17 | | 24 | 6.07 | | S38417 | 58 | 4.68 | | 58 | 4.47 | | 60 | 4.47 | | 32 | 4.61 | | 26 | 4.40 | | S38584.1 | 60 | 3.71 | | 60 | 3.71 | | 58 | N.A. | | 32 | 3.64 | | 26 | 3.65 | | Seq | 72 | 3.13 | | 72 | 3.13 | | 58 | 3.06 | | 32 | 3.20 | | 26 | 3.06 | | Spla | 88 | 4.46 | | 88 | 4.46 | | N.A. | N.A. | | 62 | 4.14 | | 40 | 4.07 | | Tseng | 56 | 4.43 | | 52 | 4.43 | | 48 | 4.43 | | 40 | 4.43 | | 38 | 4.43 | | Geo.Mean | 66 | 3.90 | | 65 | 3.95 | | 53 | 3.83 | | 41 | 3.75 | | 35 | 3.85 | | Reduction | N.A. | N.A. | | –1.51% | 1.28% | | –19.69% | –1.79% | | –37.87% | –3.84% | | -46.97% | -1.28% |

|

Table 5. Minimum channel width for different

values.