Zhiqiang Chen, Linghao Cheng, Yuan Bao, Dawei Liu, Jianlin Fan, Zhitao Chen. Architecture of Reconfigurable Transmitter Integrated Circuits for Four-Level Pulse Amplitude Modulation Optical Interconnection System[J]. Laser & Optoelectronics Progress, 2021, 58(21): 2106004

Search by keywords or author

- Laser & Optoelectronics Progress

- Vol. 58, Issue 21, 2106004 (2021)

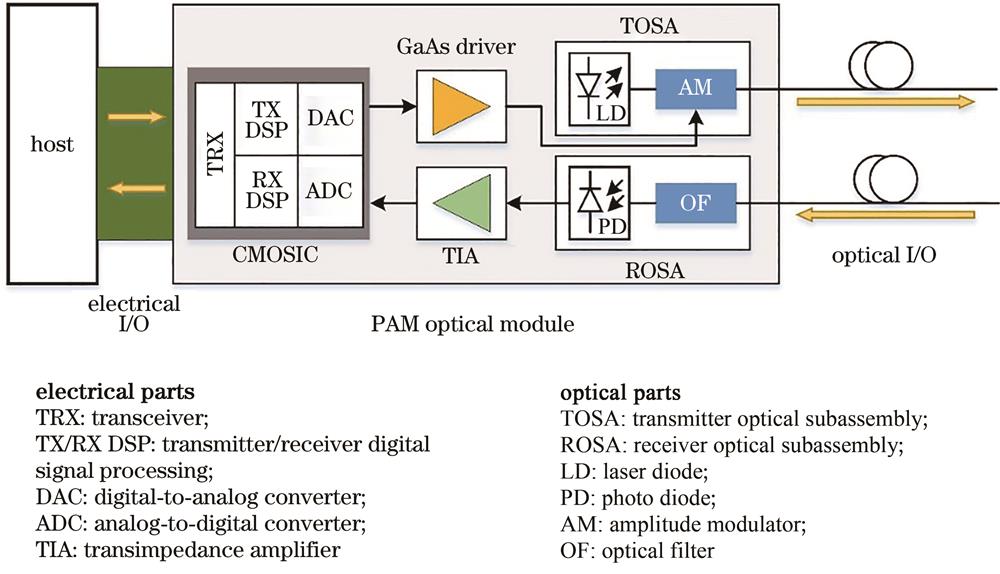

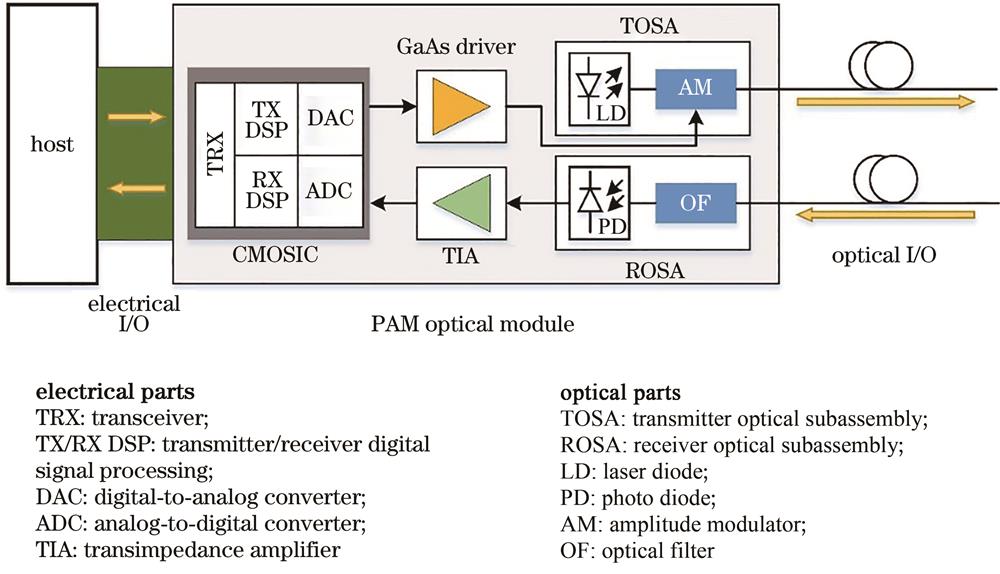

Fig. 1. Block diagram of the PAM4 optical interconnection system

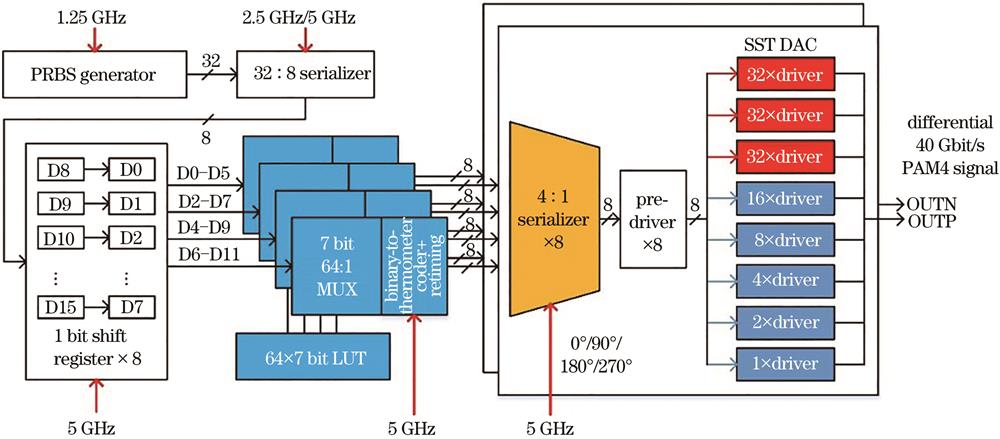

Fig. 2. Architecture of 40 Gbit/s PAM4 transmitter IC

Fig. 3. Architecture of pipelined 64∶1 MUX. (a) Overview circuit; (b) 3 stage pipeline structure; (c) 4∶1 MUX ;(d) dynamic latch and dynamic DFF

Fig. 4. 4∶1 serializer and pre-driver. (a) Circuit structure; (b) synthesis principle of the serializer signal; (c) circuit of 1 UI pulse generator; (d) structure of the pseudo AND gate

Fig. 5. Structure of the DAC

Fig. 6. Layout and simulation. (a) Layout of circuits block; (b) output eye diagram with no equalization; (c) relationship between eye diagram jitter and feedback resistor

Fig. 7. Output eye diagrams with different LUT equalization mode. (a) 2-tap FFE; (b) 3-tap FFE; (c) nonlinear equalization without FFE; (d) nonlinear equalization with 3-tap FFE

|

Table 1. Post simulation results of the delay of each level of pipeline module in 64∶1 MUX

Set citation alerts for the article

Please enter your email address