Qiao Wang, Donglin Zhang, Yulin Zhao, Chao Liu, Xiaoxin Xu, Jianguo Yang, Hangbing Lv. Low-cost dual-stage offset-cancelled sense amplifier with hybrid read reference generator for improved read performance of RRAM at advanced technology nodes[J]. Journal of Semiconductors, 2021, 42(8): 082401

Search by keywords or author

- Journal of Semiconductors

- Vol. 42, Issue 8, 082401 (2021)

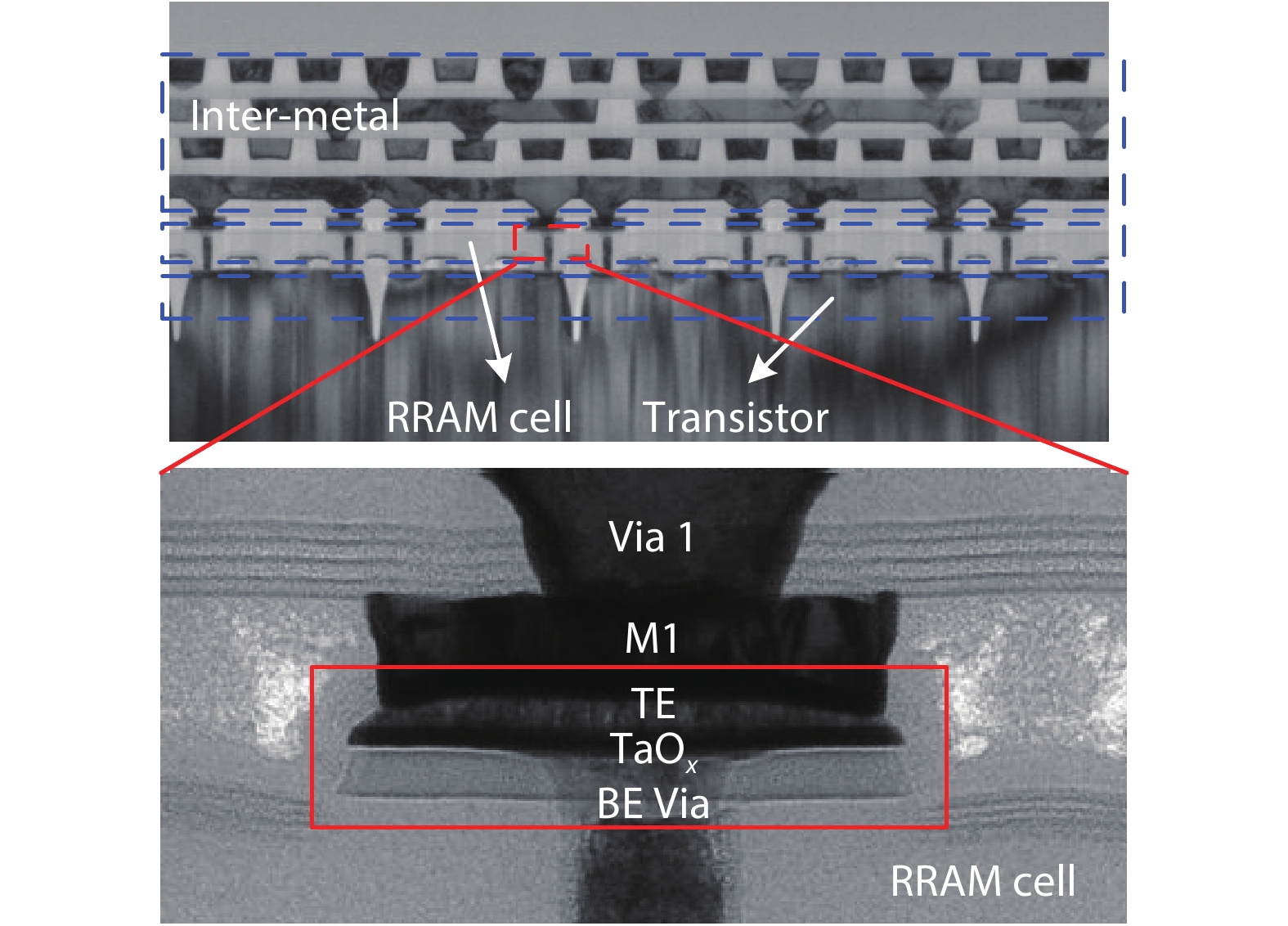

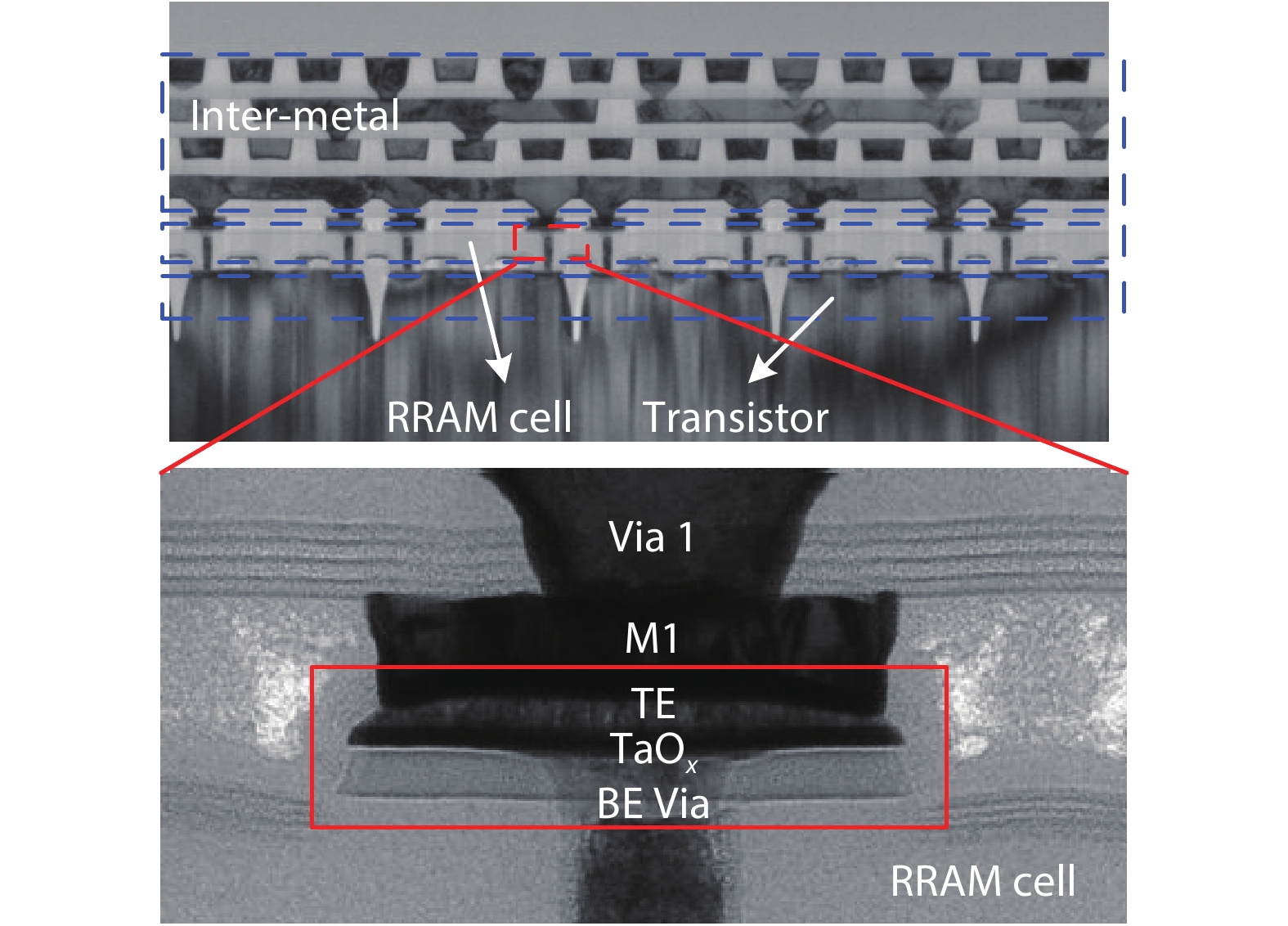

Fig. 1. The TEM images of 1T1R RRAM cells.

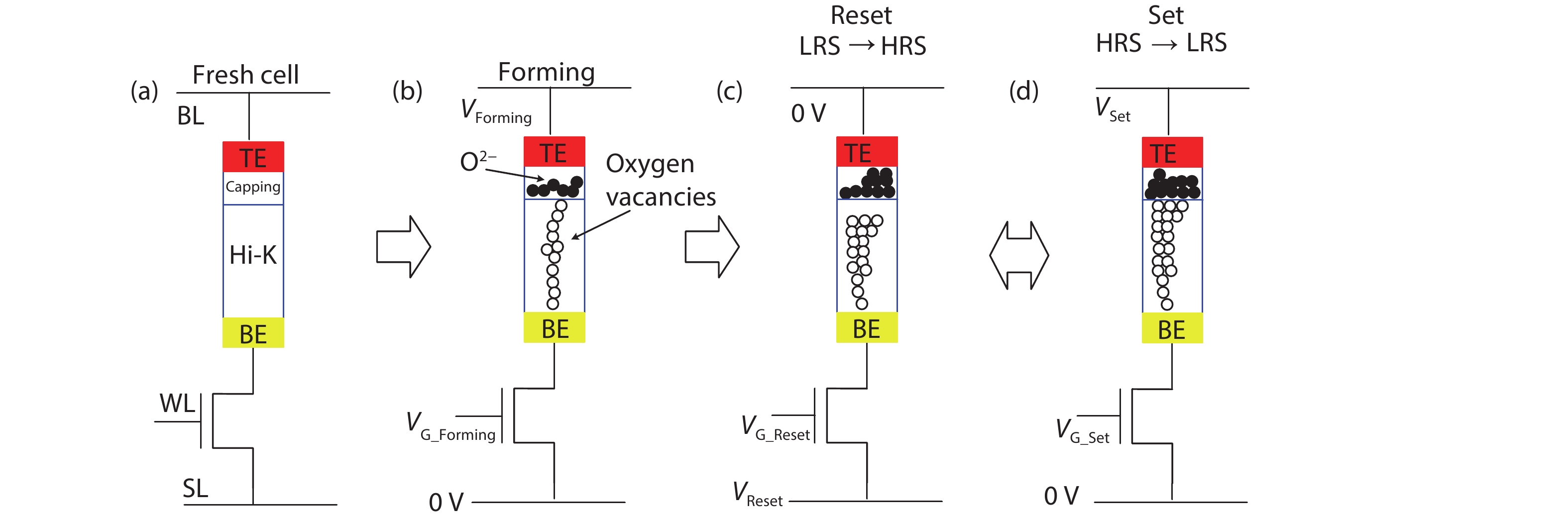

Fig. 2. (Color online) RRAM cell basic operations: CFs forming, Reset and Set.

Fig. 3. (Color online) Measured I–V curve and ideal I–V curve of RRAM cell. Ideal I MP is the mid-point current of the ideal value of I HRS and I LRS. Actual I MP is the mid-point current of the measured value of I HRS and I LRS. The actual I MP is 18.4% lower than the ideal I MP.

Fig. 4. (Color online) Reference cell structure diagrams for SP scheme, PSRC scheme and HRRG scheme.

Fig. 5. (Color online) The distributions of cell current and the reference current.

Fig. 6. (Color online) The maximum latency of the CSA with different reference cells.

Fig. 7. (Color online) Schematic diagram of TSOCC-SA.

Fig. 8. (Color online) The timing of TSOCC-SA.

Fig. 9. (Color online) CSB-SA and proposed TSOCC-SA. Bit-cell state 1 (I cell > I ref) is assumed in the V A and V B waveforms.

Fig. 10. (Color online) (a) Simulated ∆V [= min |V A –V B|] and ∆I [= min |I A –I B|] vs. V TH mismatch between transistors M1 and M2. (b) The maximum V TH mismatch that can be tolerated by TSOCC-SA at different operation voltage.

Fig. 11. (Color online) The extra area overhead and sensing margin of several offset-cancellation techniques.

|

Table 1. RRAM cell operating conditions.

|

Table 2. Performances of several offset-cancellation techniques.

Set citation alerts for the article

Please enter your email address