[1] C W S Yeh, S S Wong. Compact one-transistor-N-RRAM array architecture for advanced CMOS technology. IEEE J Solid-State Circuits, 50, 1299(2015).

[2] J Woo, S M Yu. Two-step read scheme in one-selector and one-RRAM crossbar-based neural network for improved inference robustness. IEEE Trans Electron Devices, 65, 5549(2018).

[3] M F Chang, C W Wu, C C Kuo et al. A 0.5 V 4 Mb logic-process compatible embedded resistive RAM (ReRAM) in 65 nm CMOS using low-voltage current-mode sensing scheme with 45 ns random read time. 2012 IEEE International Solid-State Circuits Conference, 434(2012).

[4] P Jain, U Arslan, M Sekhar et al. 13.2 A 3.6 Mb 10.1Mb/mm2 embedded non-volatile ReRAM macro in 22 nm FinFET technology with adaptive forming/set/reset schemes yielding down to 0.5 V with sensing time of 5 ns at 0.7 V. 2019 IEEE International Solid-State Circuits Conference, 212(2019).

[5] W H Chen, C M Dou, K X Li et al. CMOS-integrated memristive non-volatile computing-in-memory for AI edge processors. Nat Electron, 2, 420(2019).

[6] C C Chou, Z J Lin, C A Lai et al. A 22nm 96K × 144 RRAM macro with a self-tracking reference and a low ripple charge pump to achieve a configurable read window and a wide operating voltage range. IEEE Symposium on VLSI Circuits, 1(2020).

[7] T Na, B Song, J P Kim et al. Offset-canceling current-sampling sense amplifier for resistive nonvolatile memory in 65 nm CMOS. IEEE J Solid-State Circuits, 52, 496(2017).

[8] Q Dong, Z H Wang, J Lim et al. A 1Mb 28nm STT-MRAM with 2.8ns read access time at 1.2V VDD using single-cap offset-cancelled sense amplifier and

[9] M F Chang, S J Shen, C C Liu et al. An offset-tolerant current-sampling-based sense amplifier for sub-100nA-cell-current nonvolatile memory. IEEE International Solid-State Circuits Conference, 206(2011).

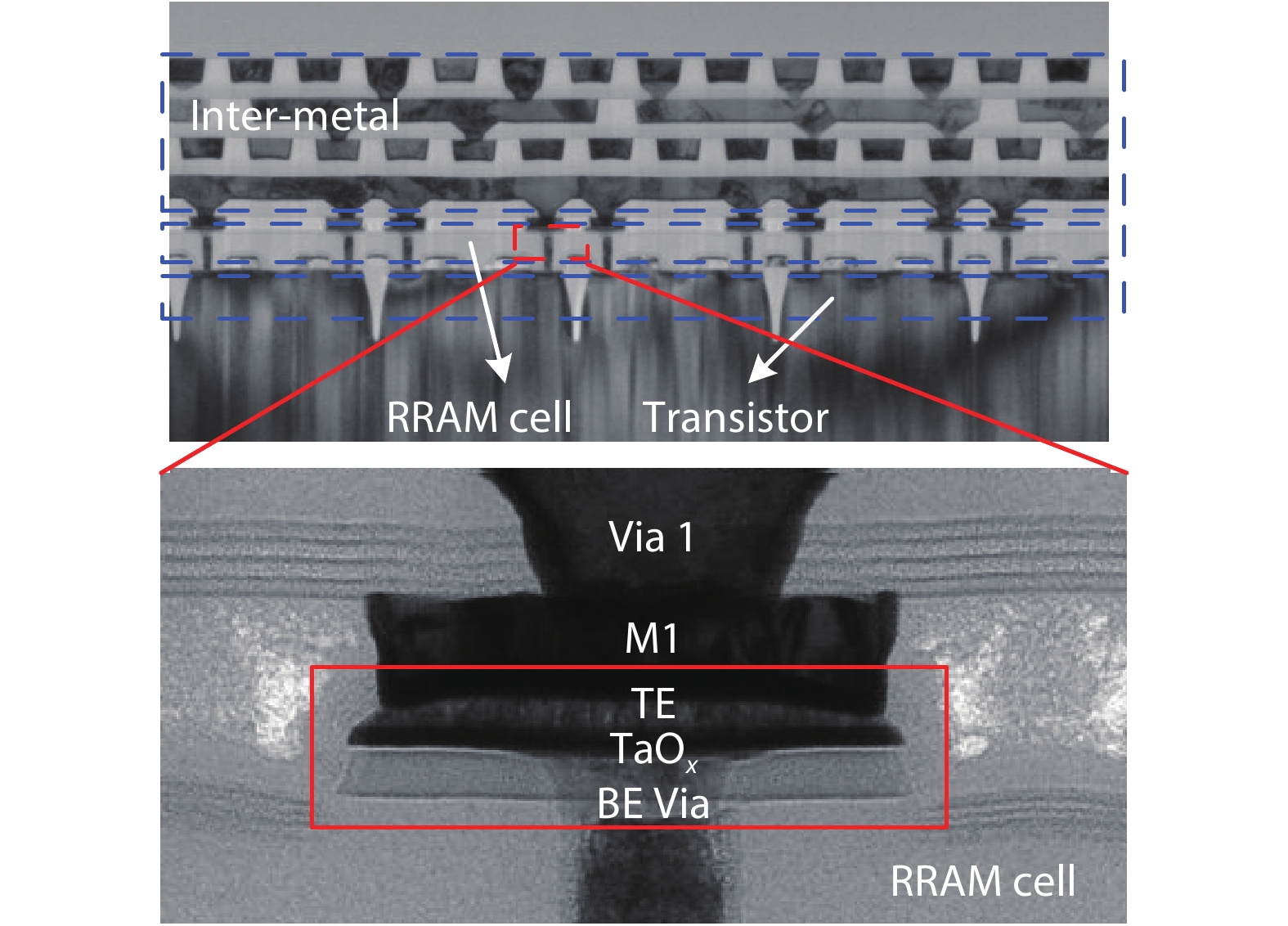

[10] Y L Huang, R Huang, Y M Cai et al. A TaO

[11] C C Chou, Z J Lin, P L Tseng et al. An N40 256K × 44 embedded RRAM macro with SL-precharge SA and low-voltage current limiter to improve read and write performance. IEEE International Solid-State Circuits Conference, 478(2018).

[12] S Chakrabarti, D Jana, M Dutta et al. Impact of AlO

[13] T Na, J Kim, J P Kim et al. Reference-scheme study and novel reference scheme for deep submicrometer STT-RAM. IEEE Trans Circuits Syst I, 61, 3376(2014).

[14] M Durlam, P J Naji, A Omair et al. A 1-Mbit MRAM based on 1T1MTJ bit cell integrated with copper interconnects. IEEE J Solid-State Circuits, 38, 769(2003).

[15] M F Chang, S S Sheu, K F Lin et al. A high-speed 7.2-ns read-write random access 4-mb embedded resistive RAM (ReRAM) macro using process-variation-tolerant current-mode read schemes. IEEE J Solid-State Circuits, 48, 878(2013).

[16] Q K Trinh, S Ruocco, M Alioto. Dynamic reference voltage sensing scheme for read margin improvement in STT-MRAMs. IEEE Trans Circuits Syst I, 65, 1269(2018).

[17] W Kang, T T Pang, W Lv et al. Dynamic dual-reference sensing scheme for deep submicrometer STT-MRAM. IEEE Trans Circuits Syst I, 64, 122(2017).

[18] Y L Zhou, H Cai, L Xie et al. A self-timed voltage-mode sensing scheme with successive sensing and checking for STT-MRAM. IEEE Trans Circuits Syst I, 67, 1602(2020).