- Journal of Semiconductors

- Vol. 42, Issue 8, 082401 (2021)

Abstract

1. Introduction

Resistive random access memory (RRAM) has been studied as a promising candidate for the next generation of embedded non-volatile memory due to its advantages such as high scalability, low power consumption, high speed and non-volatility[

In this work, a two-stage offset-cancelled current sense amplifier (TSOCC-SA) with only two capacitors is proposed. Two capacitors are used to maximize the sensing margin of RRAM and the tolerance of device mismatch. In addition, a hybrid read reference generator (HRRG) is designed by combining RRAM cells and linear resistors to provide a read reference that can track PVT variations and solve the nonlinear issue of the RRAM cells.

2. RRAM cell and its nonlinearity

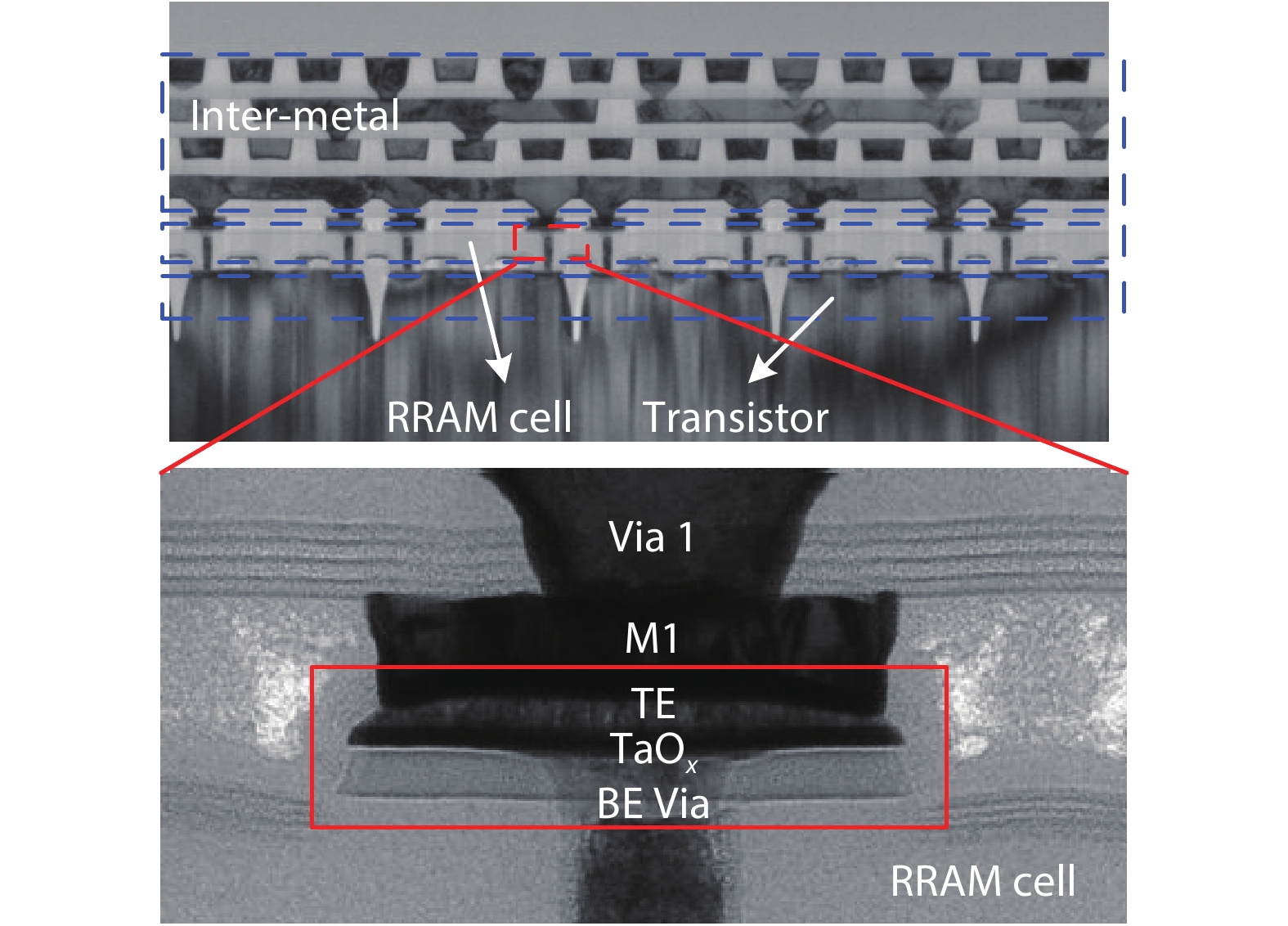

The structure of the 1T1R RRAM cell used in this study includes an NMOS switch transistor and a TaOx-based bipolar resistor memory device. Fig. 1 shows the cross-section transmission electron microscope (TEM) images of the fabricated RRAM cells in the 28 nm CMOS process. The RRAM is fabricated at the back end of line (BEOL) process and is fully compatible with the logic process[

![]()

Figure 1.The TEM images of 1T1R RRAM cells.

The schematic of the 1T1R RRAM cell is shown in Fig. 2, including the word line (WL) used to select the cell, and the bit line (BL) and source line (SL) used to apply the corresponding operation voltage. A fresh RRAM cell is in an initial state with extremely high resistance[

![]()

Figure 2.(Color online) RRAM cell basic operations: CFs forming, Reset and Set.

In the read operation, a small read voltage (Vread is much lower than set voltage) is applied to the BL and then the CSA detects the current in the read path to determine the state of the cell resistance. The Vread applied to the BL will cause the migration of a small number of oxygen atoms. Then the distribution of oxygen vacancies inside the RRAM cell is changed and the resistance of RRAM cells exhibits nonlinearity. As shown in Fig. 3, the ideal linear I–V curve of HRS and LRS is not exactly consistent with the measured I–V curve.

![]()

Figure 3.(Color online) Measured

Table 1 shows the operating conditions of the 1T1R RRAM cell used in this study. The RRAM cell has a large resistance variation (R-variation). R-variation leads to the wide distribution of cell current (Icell) and references current (Iref) that will cause sensing yield issues[

3. Hybrid read reference generator

The previous dummy reference cell structures of the Serial-Parallel (SP) scheme[

![]()

Figure 4.(Color online) Reference cell structure diagrams for SP scheme, PSRC scheme and HRRG scheme.

The average of HRS RRAM cell and LRS RRAM cell is used as the reference in the SP scheme, and the Isp is as Eq. (1).

Fig. 5 shows the simulated reference current (Iref) distributions of conventional reference schemes and the proposed hybrid read reference, not considering the nonlinearity of the RRAM cell. The ideal reference for CSA should be the mid-point current of the two neighboring memory states (IMP). The reference current generated by SP schemes is closer to the current of HRS (IHRS) and the existing overlap may cause sensing failure with PVT variations. The reference current generated by PSRC (IPSRC) and the proposed HRRG (IHRRG) is in the middle of IHRS and ILRS, as shown in Eq. (2).

![]()

Figure 5.(Color online) The distributions of cell current and the reference current.

This is very close to the ideal reference for the CSA. In addition, as shown in Fig. 5, the HRRG can achieve a narrower distribution compared with the PSRC. Specifically, the HRRG reduces the σ-IREF by 49% compared with the PSRC scheme. The difference between the proposed HRRG and the previous PSRC scheme is that the pair of parallel RRAM cells in the PSRC scheme is replaced by linear resistors to solve the nonlinear issue of RRAM cells, as shown in Fig. 4. The two linear resistors are trimmed close to HRS and LRS of RRAM cells, respectively. Assuming that the four linear resistors are used in HRRG, the reference current with the most narrower distribution range can be obtained. However, it will not be able to track the PVT variations of the RRAM cell.

As shown in Fig. 3, the resistance of the RRAM cell is nonlinear. The voltage falling on two pairs of parallel resistors is about Vread/2 according to Ohm’s law. Therefore, the expression of the actual currents of the PSRC scheme and the HRRG scheme can be described as Eq. (3).

Taking into account the nonlinearity of the RRAM cell, Fig. 3 shows the measured ILRS and IHRS which are 25% and 70% lower than the ideal value at a read voltage of 0.3 V, respectively. Hence, the actual value of the IMP is 18.4% lower than the ideal value of the IMP. The IPSRC is 14.86% higher than the actual value of the IMP calculated from the I–V curve in Fig. 3. By contrast, the proposed IHRRG is only 0.49% higher than the actual value of the IMP.

Using the proposed HRRG scheme, the reference current shows a more concentrated distribution and is more agreed with the true value of IMP. Hence, the sensing margin is maximized and the accuracy of the reading is improved. Moreover, the latency of the CSA with HRRG is minimum compared with the CSA with SP or PSRC, as shown in Fig. 6.

![]()

Figure 6.(Color online) The maximum latency of the CSA with different reference cells.

4. Two-stage offset-cancelled current sense amplifier

A two-stage offset-cancelled current sense amplifier (TSOCC-SA) with only two capacitors is proposed to improve the sensing margin. Fig. 7 shows the schematic of TSOCC-SA. The TSOCC-SA is comprised of a current-sampling and a latch. Compared to the previous OCCS-SA in Ref. [7], the proposed TSOCC-SA uses two cross switches (S1 and S2) for offset-cancellation. The switches (S3 and S4) are used to enlarge the sensing margin. Combined with the use of switches S1, S2, S3, and S4, only one capacitor can realize the function in Ref. [7], which significantly reduces the area of the circuit. The offset cancellation of the second stage of TSOCC-SA is realized by using a similar scheme proposed by Dong[

![]()

Figure 7.(Color online) Schematic diagram of TSOCC-SA.

Fig. 8 shows the timing of TSOCC-SA. In P1, the outputs of the two inverters are connected to their inputs, respectively. The difference between the trip voltages of the two inverters (VTR – VTL) is sampled by capacitor C2. In P2, the outputs of the two inverters are reset to “0”. And, the input of the right inverter becomes “VTR – VTL” while that of the left inverter remains “0”. In P3, two diode-connected transistors (M1 and M2) supply pre-charge currents (Ipre1 and Ipre2) to A and B nodes. After a sufficient pre-charge time, the currents of M1 and M2 (IM1 and IM2) decrease to nearIref and Icell, regardless of the device mismatch in M1 (M2) as long as Icell and Iref are constant in P3. Finally, the gate voltages (VG1 and VG2) of M1 and M2 are stored at the left and right ends of capacitor C1, respectively. In P4, the four switches (S5–S8) are turned off and the two switches (S1 and S2) are turned on. The A (B) node has a current path to GND through S3 (S4), resulting in strong positive feedback. In P5, the latch comparator starts to work and outputs “1” or “0”.

![]()

Figure 8.(Color online) The timing of TSOCC-SA.

Fig. 9 shows the simulated waveforms of the CSB-SA[

![]()

Figure 9.(Color online) CSB-SA and proposed TSOCC-SA. Bit-cell state 1 (

Fig. 10(a) shows the sensing margin development with VTH mismatch between M1 and M2. For TSOCC-SA, when the device mismatch reaches 64% of the threshold voltage, the sensing margin is still enough, and the sense amplifier is valid. It clearly shows that the TSOCC-SA has higher offset-tolerance than the CSB-SA in Ref. [9]. And the TSOCC-SA can work at a lower operation voltage to reduce power consumption by introducing offset-cancellation techniques, as shown in Fig. 10(b). In addition, when the mismatch between M1 and M2 exceeds 225 mV, the swing between A and B is lower or even only tens of millivolts. Then, the mismatch between M4 and M5, M6 and M7 in the latch comparator will lead to the invalidation of SA. Hence, it is extremely necessary to introduce the cross-coupling capacitor C2 in the latch comparator to cancel these device mismatches, which can further improve the accuracy of SA. Dong et al. have proved that the standard deviation of the mismatches is reduced by more than 60% by C2[

![]()

Figure 10.(Color online) (a) Simulated ∆

Moreover, the TSOCC-SA avoids excessive area overhead. In the layout, the area of the coupling capacitor is equivalent to that of a transistor. Fig. 11 shows the sensing margin of several offset-cancellation techniques (CSB-SA[

![]()

Figure 11.(Color online) The extra area overhead and sensing margin of several offset-cancellation techniques.

Table 2 shows the performance comparison of several offset-cancellation techniques. The area is characterized by the number of coupling capacitors (Caps). Stage indicates that the mismatch of how many stages of SA can be cancelled. Cancellation ability indicates the percentage of the mismatch voltage to the threshold voltage that can be tolerated by SA.

5. Conclusion

In this paper, we proposed a two-stage offset-cancelled current sense amplifier (TSOCC-SA) with only two capacitors for RRAM at an advanced technology node. A hybrid read reference generator (HRRG) is designed by combining RRAM cells and resistors to provide a read reference that tracking PVT variations and to solve the nonlinear issue of the RRAM cells. The simulation results in the 28 nm CMOS process have proved the effectiveness of HRRG and the reliability of the TSOCC-SA.

Acknowledgements

This work was supported in part by the National Key R&D Program of China under Grant No. 2019YFB2204800 and in part by the Major Scientific Research Project of Zhejiang Lab (Grant No. 2019KC0AD02) and in part by the National Natural Science Foundation of China under Grants 61904200 and the Strategic Priority Research Program of the Chinese Academy of Sciences under Grant No. XDB44000000.

References

[1] C W S Yeh, S S Wong. Compact one-transistor-N-RRAM array architecture for advanced CMOS technology. IEEE J Solid-State Circuits, 50, 1299(2015).

[2] J Woo, S M Yu. Two-step read scheme in one-selector and one-RRAM crossbar-based neural network for improved inference robustness. IEEE Trans Electron Devices, 65, 5549(2018).

[3] M F Chang, C W Wu, C C Kuo et al. A 0.5 V 4 Mb logic-process compatible embedded resistive RAM (ReRAM) in 65 nm CMOS using low-voltage current-mode sensing scheme with 45 ns random read time. 2012 IEEE International Solid-State Circuits Conference, 434(2012).

[4] P Jain, U Arslan, M Sekhar et al. 13.2 A 3.6 Mb 10.1Mb/mm2 embedded non-volatile ReRAM macro in 22 nm FinFET technology with adaptive forming/set/reset schemes yielding down to 0.5 V with sensing time of 5 ns at 0.7 V. 2019 IEEE International Solid-State Circuits Conference, 212(2019).

[5] W H Chen, C M Dou, K X Li et al. CMOS-integrated memristive non-volatile computing-in-memory for AI edge processors. Nat Electron, 2, 420(2019).

[6] C C Chou, Z J Lin, C A Lai et al. A 22nm 96K × 144 RRAM macro with a self-tracking reference and a low ripple charge pump to achieve a configurable read window and a wide operating voltage range. IEEE Symposium on VLSI Circuits, 1(2020).

[7] T Na, B Song, J P Kim et al. Offset-canceling current-sampling sense amplifier for resistive nonvolatile memory in 65 nm CMOS. IEEE J Solid-State Circuits, 52, 496(2017).

[8] Q Dong, Z H Wang, J Lim et al. A 1Mb 28nm STT-MRAM with 2.8ns read access time at 1.2V VDD using single-cap offset-cancelled sense amplifier and

[9] M F Chang, S J Shen, C C Liu et al. An offset-tolerant current-sampling-based sense amplifier for sub-100nA-cell-current nonvolatile memory. IEEE International Solid-State Circuits Conference, 206(2011).

[10] Y L Huang, R Huang, Y M Cai et al. A TaO

[11] C C Chou, Z J Lin, P L Tseng et al. An N40 256K × 44 embedded RRAM macro with SL-precharge SA and low-voltage current limiter to improve read and write performance. IEEE International Solid-State Circuits Conference, 478(2018).

[12] S Chakrabarti, D Jana, M Dutta et al. Impact of AlO

[13] T Na, J Kim, J P Kim et al. Reference-scheme study and novel reference scheme for deep submicrometer STT-RAM. IEEE Trans Circuits Syst I, 61, 3376(2014).

[14] M Durlam, P J Naji, A Omair et al. A 1-Mbit MRAM based on 1T1MTJ bit cell integrated with copper interconnects. IEEE J Solid-State Circuits, 38, 769(2003).

[15] M F Chang, S S Sheu, K F Lin et al. A high-speed 7.2-ns read-write random access 4-mb embedded resistive RAM (ReRAM) macro using process-variation-tolerant current-mode read schemes. IEEE J Solid-State Circuits, 48, 878(2013).

[16] Q K Trinh, S Ruocco, M Alioto. Dynamic reference voltage sensing scheme for read margin improvement in STT-MRAMs. IEEE Trans Circuits Syst I, 65, 1269(2018).

[17] W Kang, T T Pang, W Lv et al. Dynamic dual-reference sensing scheme for deep submicrometer STT-MRAM. IEEE Trans Circuits Syst I, 64, 122(2017).

[18] Y L Zhou, H Cai, L Xie et al. A self-timed voltage-mode sensing scheme with successive sensing and checking for STT-MRAM. IEEE Trans Circuits Syst I, 67, 1602(2020).

Set citation alerts for the article

Please enter your email address