[1] ArikanE. Channel polarization: a method for constructing capacity-achieving codes[C]∥2008 IEEE International Symposium on Information Theory, July 6-11, 2008, Toronto, ON, Canada. New York: IEEE Press, 2008: 1173- 1177.

[2] Cao Y, Li Y, Li X H. Research on construction method of polarization code in wireless optical communication[J]. Acta Optica Sinica, 40, 2106003(2020).

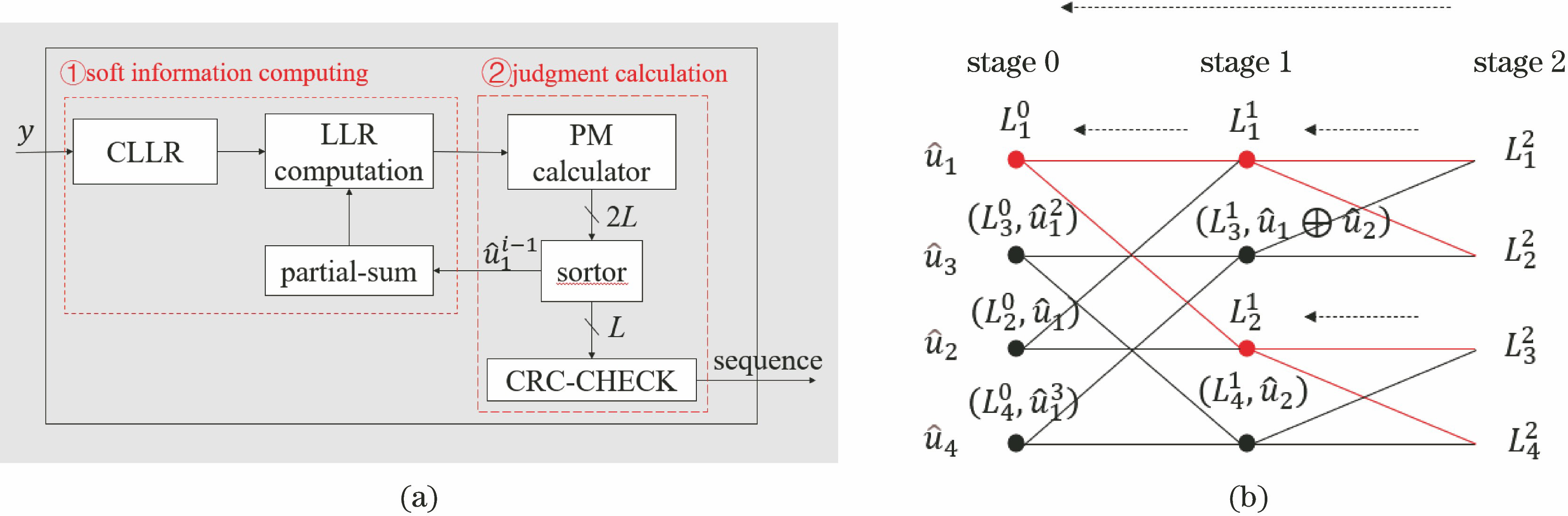

[3] Tal I, Vardy A. List decoding of polar codes[J]. IEEE Transactions on Information Theory, 61, 2213-2226(2015).

[6] NiuK, ChenK, Lin JR. Beyond turbo codes: rate-compatible punctured polar codes[C]∥2013 IEEE International Conference on Communications (ICC), June 9-13, 2013, Budapest, Hungary. New York: IEEE Press, 2013: 3423- 3427.

[7] Balatsoukas-Stimming A, Raymond A J, Gross W J et al. Hardware architecture for list successive cancellation decoding of polar codes[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 61, 609-613(2014).

[8] Balatsoukas-Stimming A, Parizi M B, Burg A. LLR-based successive cancellation list decoding of polar codes[J]. IEEE Transactions on Signal Processing, 63, 5165-5179(2015).

[9] Yuan B, Parhi K K. Low-latency successive-cancellation list decoders for polar codes with multibit decision[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 23, 2268-2280(2015).

[10] Tao Y Y, Cho S G, Zhang Z Y. A configurable successive-cancellation list polar decoder using split-tree architecture[J]. IEEE Journal of Solid-State Circuits, 56, 612-623(2021).

[11] Xia C Y, Fan Y Z. -05-22)[2021-02-01]. https: ∥arxiv., org/abs/1905, 09120(2019).

[12] Chen W, Song Y X, Li Z X et al. 50 Gbit/s NRZ IM-DD downstream transmission system based on 25G-class optical components[J]. Acta Optica Sinica, 39, 0606003(2019).

[13] Luo J W, Liu K, Wei Q et al. Integrated chip for simultaneous transmission and reception in optical communication links[J]. Acta Optica Sinica, 39, 0806003(2019).

[14] Lehnigk-Emden T, Alles M, Kestel C et al. Polar code decoder framework[C]∥2019 Design, Automation & Test in Europe Conference & Exhibition (DATE), March 25-29, 2019, Florence, Italy., 1208-1209(2019).

[15] Giard P, Balatsoukas-Stimming A, Müller T C et al. A multi-Gbps unrolled hardware list decoder for a systematic polar code[C]∥2016 50th Asilomar Conference on Signals, Systems and Computers, November 6-9, 2016, Pacific Grove, CA, USA., 1194-1198(2016).

[16] Arikan E. Channel polarization: a method for constructing capacity-achieving codes for symmetric binary-input memoryless channels[J]. IEEE Transactions on Information Theory, 55, 3051-3073(2009).

[18] Leroux C, Tal I, Vardy A et al. Hardware architectures for successive cancellation decoding of polar codes[C]∥2011 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), May 22-27, 2011, Prague, Czech Republic., 1665-1668(2011).

[19] Zhang C, Yuan B, Parhi K K. Reduced-latency SC polar decoder architectures[C]∥2012 IEEE International Conference on Communications (ICC), June 10-15, 2012, Ottawa, ON, Canada., 3471-3475(2012).

[20] Kestel C, Weithoffer S, Wehn N. Polar code decoder exploration framework[J]. Advances in Radio Science, 16, 43-50(2018).

[21] Afisiadis O, Balatsoukas-Stimming A, Burg A. Alow-complexity improved successive cancellation decoder for polar codes[C]∥2014 48th Asilomar Conference on Signals, Systems and Computers, November 2-5, 2014, Pacific Grove, CA, USA., 2116-2120(2014).