Yanjun Liu, Yan Li, Yuyang Liu, Xiaoshuo Jia, Honghang Zhou, Xiaobin Hong, Jifang Qiu, Hongxiang Guo, Yong Zuo, Wei Li, Jian Wu. Implementation of FPGA Based on High Throughput Parallel CRC-SCL Decoder of Polar Codes[J]. Acta Optica Sinica, 2021, 41(17): 1706002

Search by keywords or author

- Acta Optica Sinica

- Vol. 41, Issue 17, 1706002 (2021)

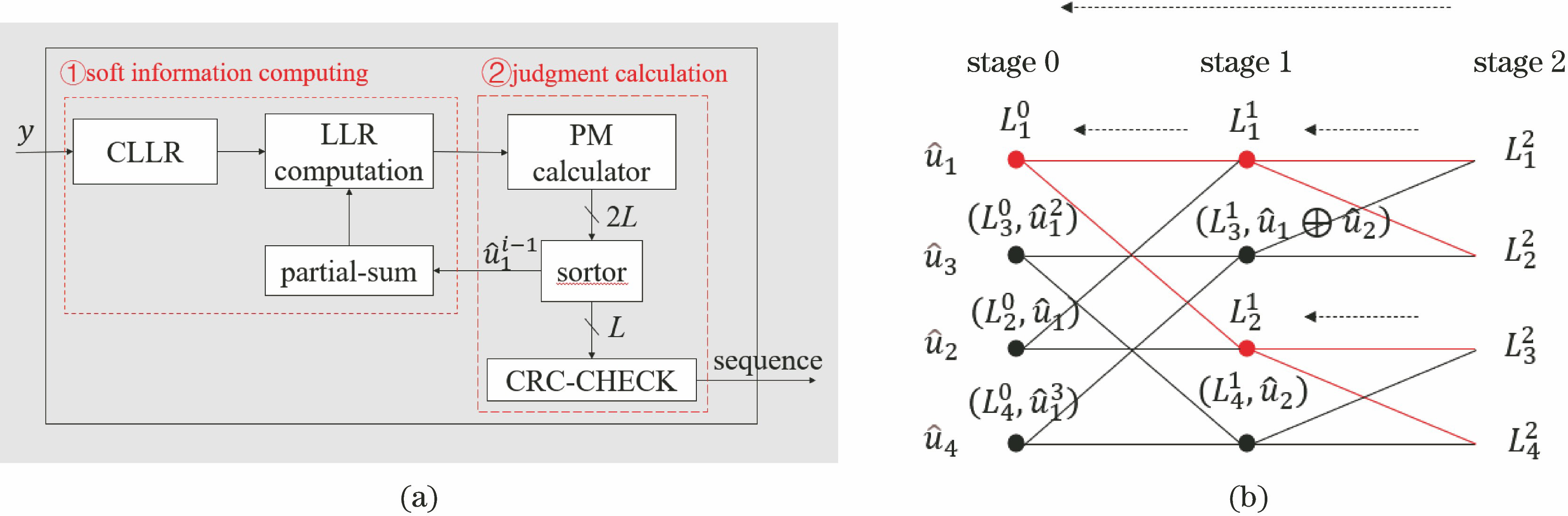

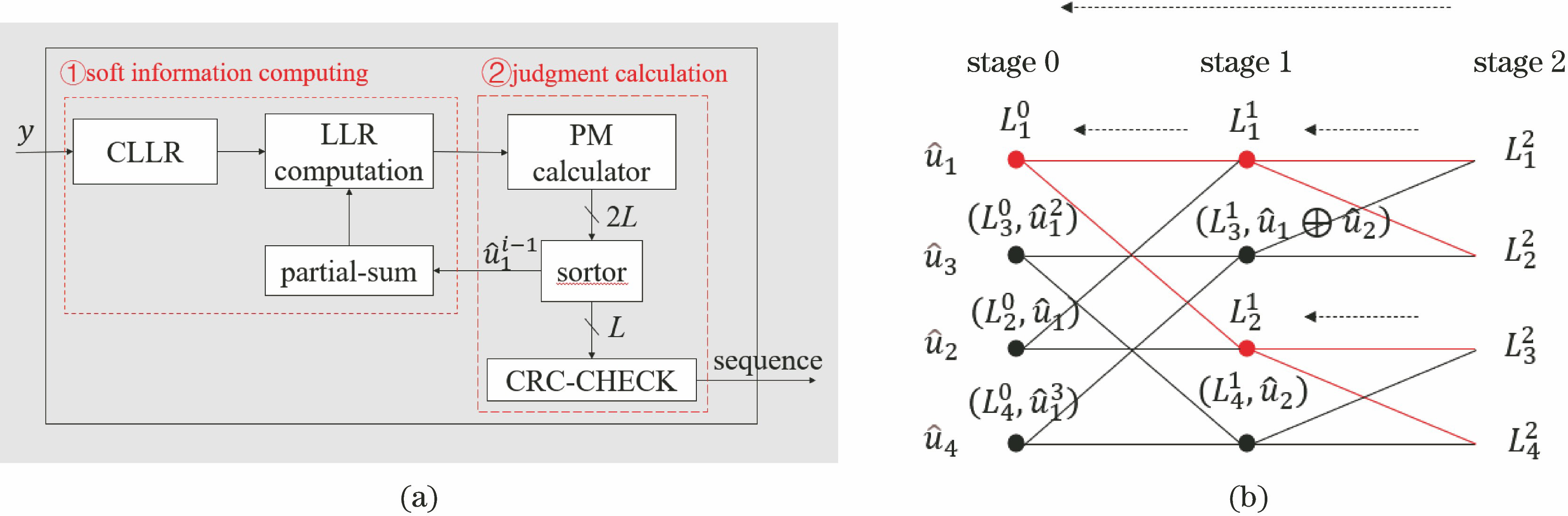

Fig. 1. Block diagrams of CRC-SCL. (a) Overview of CRC-SCL framework; (b) decoding butterfly graph of polar codes for N=4

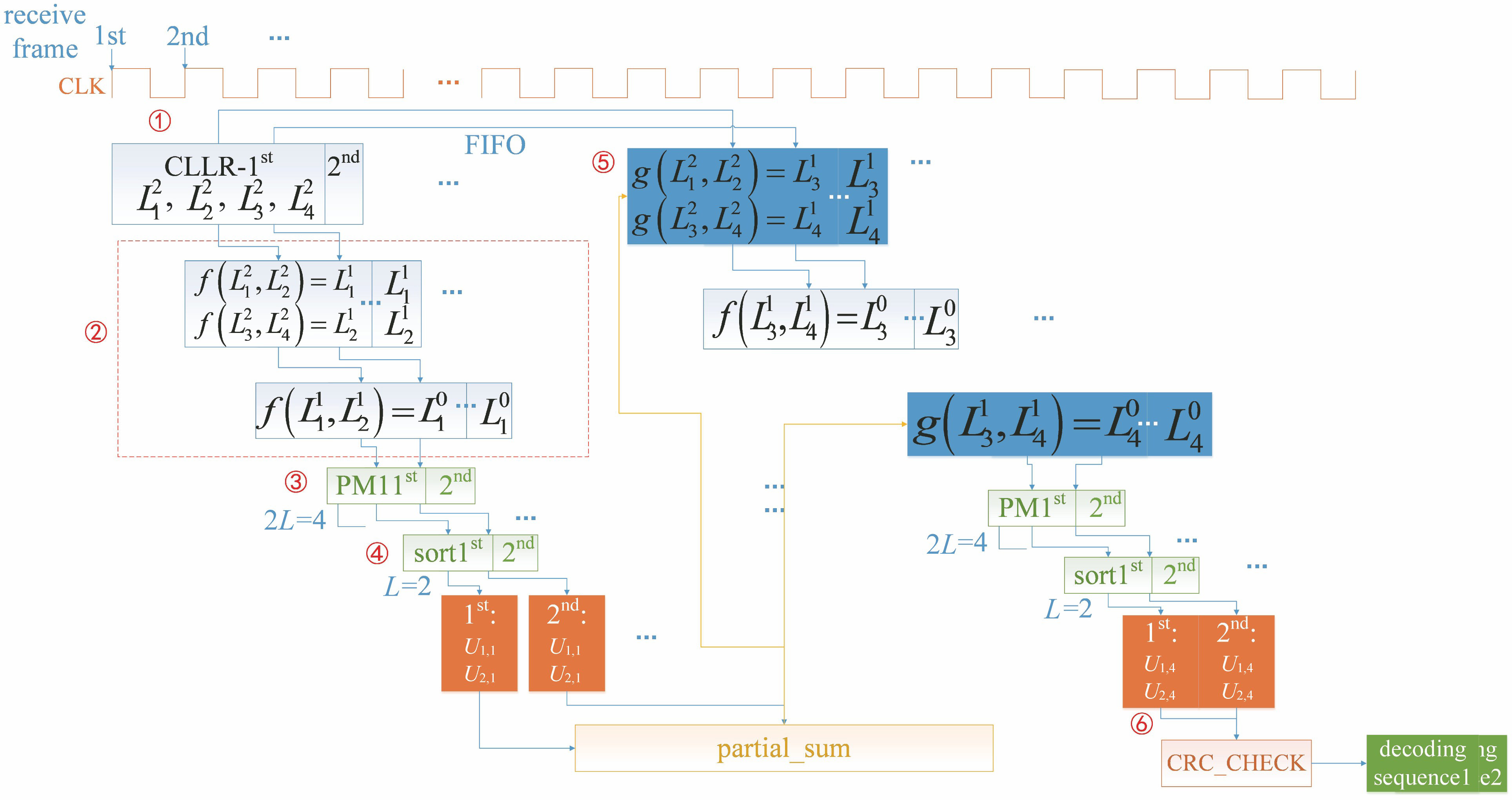

Fig. 2. Decoding flow chart of N=4 polar codes based on fully-unrolled pipeline architecture

Fig. 3. Experimental setup for Polar-QPSK system

Fig. 4. Results of back to back (B2B) experiments in polar-QPSK system. (a) Relationship between BER and ROP of CRC-SCL; (b) performance comparison of SC and CRC-SCL when R=1/2; (c) performance comparison of SC and CRC-SCL when R=4/5; (d) performance comparison of SC and CRC-SCL when R=2/3

Fig. 5. Effect of quantization on error-correction performance of CRC-SCL decoder with N=256

Fig. 6. Simulation results for CRC-SCL decoder with N=256 over AWGN channel

|

Table 1. Effect of quantization on hardware resource of CRC-SCL decoder with N=256

|

Table 2. Comparison of high throughput polar decoders

Set citation alerts for the article

Please enter your email address