Mo Huang, Yan Lu, Rui P. Martins. A comparative study of digital low dropout regulators[J]. Journal of Semiconductors, 2020, 41(11): 111405

Search by keywords or author

- Journal of Semiconductors

- Vol. 41, Issue 11, 111405 (2020)

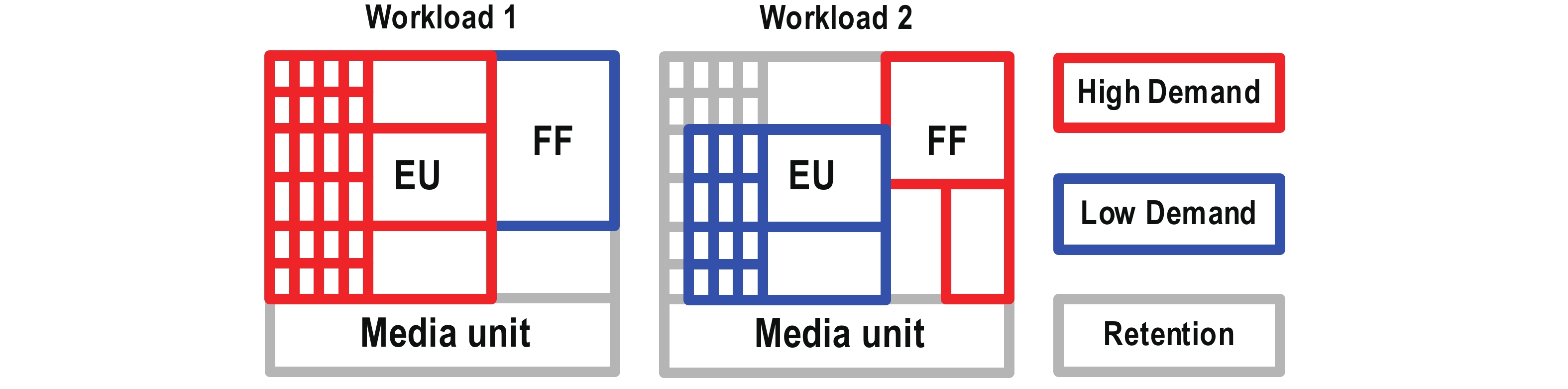

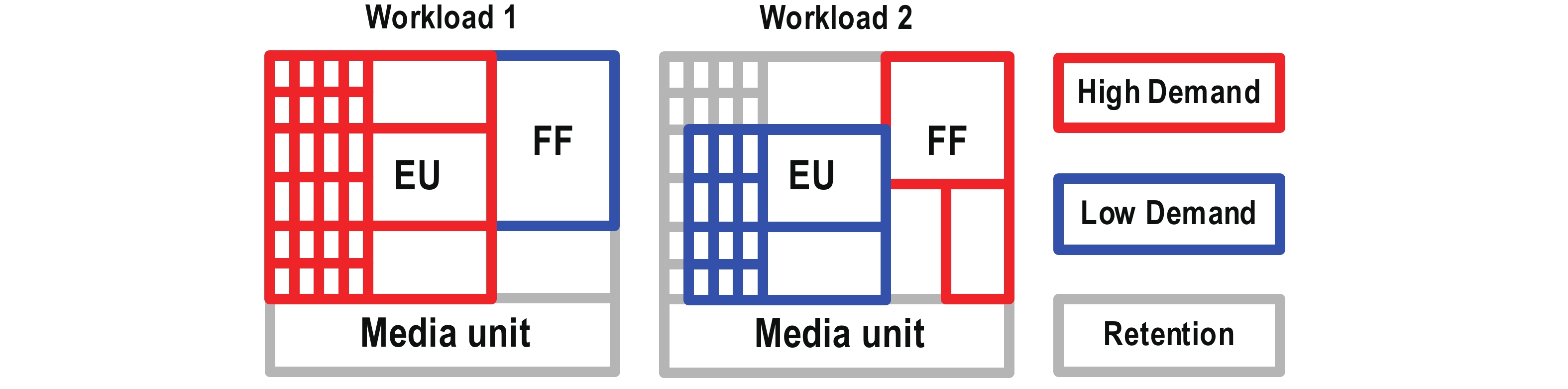

Fig. 1. (Color online) Granular power management in an SoC.

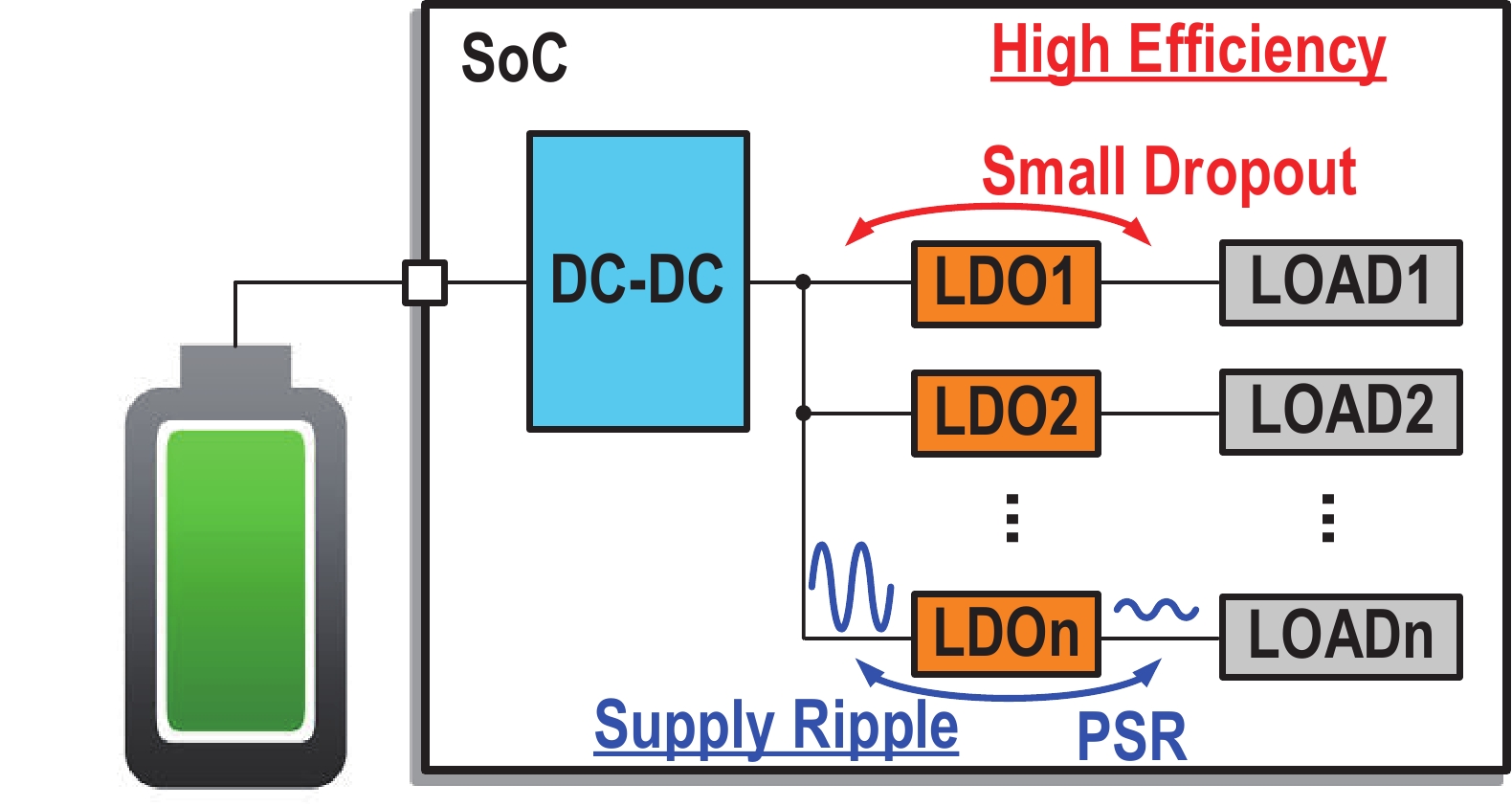

Fig. 2. (Color online) DLDO requirements in an SoC.

Fig. 3. Block diagram of (a) ALDO and (b) DLDO.

Fig. 4. (Color online) The output voltage undershoot analysis of DLDO.

Fig. 5. (a) Measured LCO of DLDO, (b) small-signal model of DLDO, and (c) root locus of 2-level quantized DLDO.

Fig. 6. (Color online) Power supply rejection process of a conventional DLDO.

Fig. 7. Latch-based comparator.

Fig. 8. Continuous multi-bit quantizer based on (a) current-mirror and (b) inverter.

Fig. 9. DLDO based on a VCO quantizer.

Fig. 10. (Color online) Output voltage transient response under I-only, P-only, PI, and PID control.

Fig. 11. Change CLK when V OUT exceeds the V REF window.

Fig. 12. (Color online) Analog-assisted loop in (a)[15 –17 ], (b)[18 ], and (c)[31 ].

Fig. 13. (a) Analog circuits help PSR improvement and (b) block diagram of the hybrid LDO.

Fig. 14. Improving PSR using (a) feedforward PSR cancellation[33 ] and (b) replica loop[34 , 35 ].

Fig. 15. (Color online) Simulated PSRs of the conventional DLDO, hybrid LDOs without replica loop, and with replica loop.

Fig. 16. (Color online) Multi-LDOs assisting a neighboring load step.

|

Table 1. Features of the quantizers in DLDO design.

|

Table 2. FoM of speed versus process nodes.

Set citation alerts for the article

Please enter your email address