- Journal of Semiconductors

- Vol. 41, Issue 11, 111405 (2020)

Abstract

1. Introduction

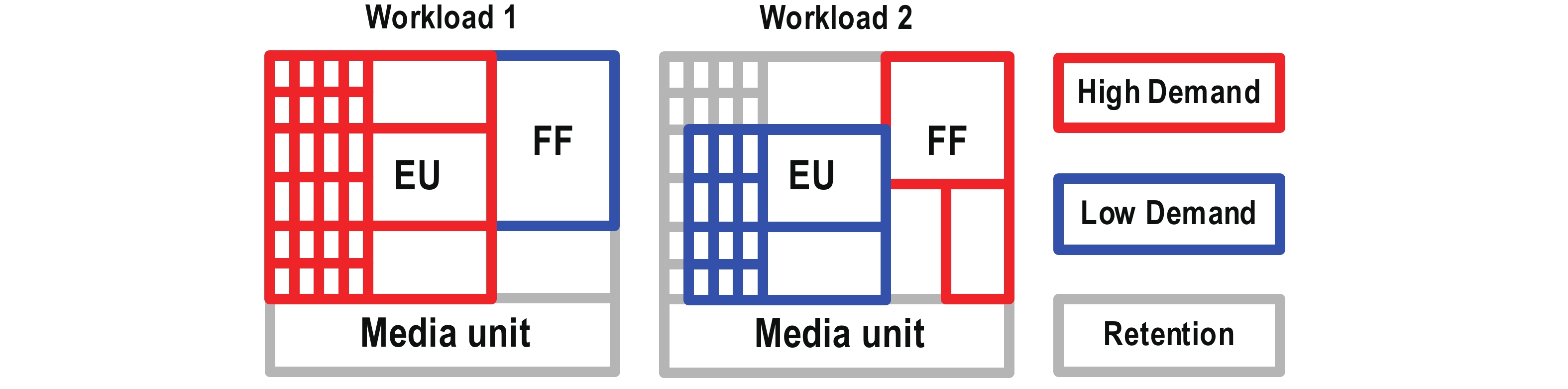

Resources in system-on-a-chip (SoC) are highly dynamic. Fig. 1 shows, under different workloads, resources such as execution units (EUs), fixed functions (FFs), and media units that can be in high demand, low demand, or retention modes. Therefore, for good system energy efficiency, we should use individual supply voltage domains for these units, each with a voltage regulator, a. k. a. granular power management[

![]()

Figure 1.(Color online) Granular power management in an SoC.

However, for an energy-efficient SoC, the load circuits may operate at a near-threshold supply voltage like 0.5 V, while the dropout voltage should be small, for example 50 mV. These working conditions hardly suit analog LDOs (ALDOs)[

On the other hand, digital LDOs (DLDO) are a good alternative[

![]()

Figure 2.(Color online) DLDO requirements in an SoC.

The widely-adopted shift-register-based DLDO firstly proposed in Ref. [10], included a power switch array, a clocked comparator to sense the output and the reference voltage difference, plus a shift-register (acting as an integrator) to generate a control word of the power switch array. Yet the synchronized shift-register only changes the control word by 1-bit every clock cycle, and thus only a high-frequency clock will allow a fast response. This increases the power consumption of the synchronized circuits. To address this trade-off, many techniques have been proposed, they will be addressed and discussed in this paper.

Another issue faced by DLDO is the power supply rejection (PSR). Fig. 2 illustrates how the load current change from a neighbor load may cause voltage ripple on the shared DLDO input. Also, input ripple can come from the pre-stage DC–DC converter. Unfortunately, the PSR of the DLDO is inherently inferior to that of the ALDO, especially when we maintain the control clock as low under the power consumption constraint. As a result, significant ripples may also occur at the DLDO output node. To prevent abnormal/interrupt operations of the load circuits caused by these supply ripples, implies the addition of a margin above the minimum workable supply voltage VMIN, which undermines the efficiency. Therefore, this paper will also investigate PSR enhancing techniques for DLDO[

This paper has the following organization: Section 2 discusses the pros and cons of the ALDO and the DLDO. Section 3 reviews the DLDO techniques on how to minimize output voltage spike, recovery time, and improve PSR. Section 4 presents the possible future trends of the DLDO design, and draws the conclusion.

2. Comparison between analog and digital LDOs

2.1. Low voltage operation and process scalability

Fig. 3 presents the basic block diagrams of the ALDO and the DLDO. The ALDO compares the output voltage (VOUT) with the reference voltage (VREF) through an error amplifier (EA). The EA’s output feeds a power transistor that operates in the saturation region in most of the cases, although it sometimes operates in the linear region as well. To maintain good output accuracy, the ALDO should have an EA with sufficient loop gain. To circumvent the stability issue of a multistage system, it would be necessary to have a one- or two-stage EA with cascode devices. Yet, more cascode devices stacked imply a larger voltage headroom, which limits the minimum supply voltage of an energy-efficient SoC. Moreover, the analog EA has a weak process scalability, and requires re-design in process migration.

![]()

Figure 3.Block diagram of (a) ALDO and (b) DLDO.

The DLDO replaces the analog EA by a VOUT sensor and a controller (integrator) implemented with digital circuits. The digital integrator manages to provide a very high DC gain that is irrelavent to its supply voltage, breaking the trade-off between loop gain and supply voltage in the analog design. As such, DLDO works well with a low supply voltage, and scales naturally with an advanced process. Meanwhile, the switch operation of the power transistors conducts more current with a full turn-on voltage (VDD), saving silicon area.

In recent years, the inverter-based LDO[

2.2. Power-speed trade-off

The widely adopted figure of merit (FoM) of speed proposed in Ref. [45] explains the power-speed trade-off of LDO:

where TR is the transient response time, IQ is the quiescent current, IMAX is the maximum load current, COUT is output capacitor, and ΔVOUT is the output voltage spike with the IMAX load step.

For an ALDO, TR is mainly determined by the bandwidth of the LDO loop and slew rate, which should be inversely proportional to the IQ. Multiple-loop schemes could be a good way to reduce TR without significantly increasing IQ[

The synchronous DLDO should have a longer TR and thus a slower transient response under the IQ constraint, due to the conventionally discrete VOUT sampling and synchronized control word changing, as illustrated in Fig. 4. When a load current (ILOAD) step comes at t1, DLDO fails to respond instantly. The output capacitor compensates the difference between ILOAD and LDO output current ILDO, leading to a VOUT drop, until the next clock (CLK) rising edge (t2) when the synchronized comparator can respond. To prevent metastability, the controller, lagging one-cycle behind t2 (t3), processes the comparator’s output (CMPOUT). After that, the control word n begins to increase, providing additional current ILDO. We define ΔtD = t3 − t1 as the loop delay, and VOUT the undershoot caused by ΔtD is ΔVDLY. Subsequently, VOUT does not stop decreasing until ILDO = ILOAD, depending on how fast the controller can find the desired control word within the processing time (ΔtP). This adds an additional voltage drop ΔVREACT to the overall undershoot ΔVMAX = ΔVDLY + ΔVREACT. Consequently, the TR of the DLDO consists of ΔtD and ΔtP, where only ΔtP contributes to the TR in analog counterparts.

![]()

Figure 4.(Color online) The output voltage undershoot analysis of DLDO.

Due to the discrete sampling, the maximum ΔtD is two-clock cycle. Hence under the power consumption constraint, ΔVDLY of the DLDO would be larger than that of the ALDO. To reduce ΔtD, continuous or asynchronous sampling techniques emerged, presented next in Section 3.

To reduce ΔVREACT, many recent DLDO techniques tried to find out the desired control word within a few cycles, taking the advantage of digital operations (discussed in Section 4). This imposes the DLDO to have a comparable or even smaller ΔVREACT than the ALDO.

2.3. Stability and limit cycle oscillation

For conventional ALDO designs, an ALDO will become unstable or even oscillate once its phase margin is not enough. But regarding the DLDO, which typically has a DC pole from the digital integrator, large signal unstable behaviour is less likely to happen. However, DLDOs suffer from another oscillation phenomenon inhexistent in ALDOs. Because of the digitized output current with limited resolution, there will always be a quantization error in the DLDO, inciting a limit cycle oscillation (LCO).

The quantization level determines the quantization error. Fig. 5(a) displays a measured VOUT LCO waveform of a two-level quantized DLDO[

![]()

Figure 5.(a) Measured LCO of DLDO, (b) small-signal model of DLDO, and (c) root locus of 2-level quantized DLDO.

Generally speaking, a smaller least significant bit (LSB) current reduces the quantization error and subsequently the LCO. Nonetheless, the small LSB exponentially increases the control bits required for the targeted output current. A pulse-width-modulated (PWM) LSB scheme proposed in Ref. [14] reduces the effective LSB. Additionally, Ref. [11] added an auxiliary path to reduce the LCO mode to 1 across a wide load current range.

2.4. Power supply rejection

An ALDO can achieve a good PSR with a properly designed EA and a dominant pole allocation[

Fig. 6 illustrates the power supply ripple rejection process of a DLDO, where discontinuous sampling and control word changing will excite significant glitches with a supply voltage ripple. We define the optimum control word n (nopt) that imposes VOUT = VREF in the steady-state, with the change of n synchronized with the clock rising edge. In an ideal case, the controller manages to find out nopt (n1 = nopt) at each sampling point (t0, t1, t2, t3), with VOUT pulled-back to VREF. However, during the sampling intervals, e.g., from t0 to t1, with n fixed, the instant PSR becomes:

![]()

Figure 6.(Color online) Power supply rejection process of a conventional DLDO.

where rds represents the instance resistance of the power transistor (constant value during the intervals), RLOAD is the load resistance. This indicates that the DLDO is vulnerable to the supply ripple during the sampling intervals.

For the non-ideal cases when n1 ≠ nopt, e.g., at t1, it causes an error Ve = VOUT − VREF. Then before the next sampling, VOUT starts to increase with VIN from Ve, leading to a larger VOUT ripple. Therefore, the only way for a conventional DLDO to improve the PSR is to minimize the sampling interval using a faster CLK. Unfortunately, this contradicts the power-efficient prerequisite. Section 5 introduces several techniques to incorporate a continuous analog path to enhance the PSR.

3. Design considerations about the DLDO

3.1. Quantizer

A quantizer will approximate the voltage error between VOUT and VREF for further processing. Conventional DLDOs use a two-level, synchronized, latch-based comparator[

![]()

Figure 7.Latch-based comparator.

High-performance DLDO designs[

![]()

Figure 8.Continuous multi-bit quantizer based on (a) current-mirror and (b) inverter.

A voltage-controlled oscillator (VCO) can also be a continuous quantizer[

![]()

Figure 9.DLDO based on a VCO quantizer.

As a brief summary, the features of the quantizers in DLDO design are included in Table 1.

3.2. PID control

One of the possible solutions to address the power-speed trade-off of the DLDO is to use asynchronous control logic[

Another straightforward way combines the proportional, integral (PI), and even derivative (PID) controls[

![]()

Figure 10.(Color online) Output voltage transient response under I-only, P-only, PI, and PID control.

3.2.1. Digital PID control

As discussed above, the number of the quantization levels should be proportional to the power consumption. For a low power design, the detection of whether VOUT exceeds the VREF window[

![]()

Figure 11.Change CLK when

High-performance designs employ typically a multi-level quantization with an ADC[

Granular power management oversees not only the VOUT overshoot/undershoot, but also the recovery time. For a linear increment control used in the conventional DLDO[

where the recovery time may be a bit longer than the binary search.

3.2.2. Analog-assisted loop

By using analog circuits to sense VOUT[

Fig. 12(a) presents an “analog-assisted” method proposed in Refs. [15, 16]. A passive high-pass network RC and CC couples to the ground of the driving inverters (VSSB) the high-frequency components of VOUT.RC biases VSSB to the ground in the steady-state, while drops to a negative value (almost equal to the VOUT undershoot) at the load transient with a minor delay, allowing the power transistors to generate more instantaneous output current as a high-pass path. Ref. [17] further reduces the VOUT undershoot by providing more instantaneous current, through coupling VOUT to the body of the power transistors. The drawback of these schemes is that the analog circuit can only assist the turned-on power transistors, setting a limit on the minimum output current. Ref. [18] proposed an improved version (Fig. 12(b)), where analog paths include not only the high-pass network (P2), but also NMOS pass devices (P1). This advances the PMOS counterpart, by providing more instantaneous current from both turned-on and -off pass devices. Nevertheless, this benefit trades with the need for a gate drive voltage higher than the supply voltage. Ref. [31], although not implemented from a digitized output power transistor array, also utilizes a capacitor to couple the output spike to the gate of the power transistor as a high-pass path (Fig. 12(c)). A charge pump generates the gate voltage of the power transistor. Though it is analog in nature, it can be a good candidate for a low-power DLDO.

![]()

Figure 12.(Color online) Analog-assisted loop in (a)[

In addition, the analog-assisted methods can be an effective solution to improve the DLDO transient response without using advanced process. Table 2 summarizes the process nodes and FoMs (from (1)) of state-of-the-art DLDO works, to evaluate how the process advancement enhances the DLDO performance. As can be seen, the FoM value decreases with process scaling down for the ADC-based DLDO designs[

3.3. PSR improvements

As discussed in Section 2, the DLDO has inherently mediocre PSR even when the optimum control word can be found. Instead, analog circuits may be the only solution under the power consumption constraint. As illustrated in Fig. 13(a), by parallelizing an analog resistance rds,A with the digitized resistance rds,D, the overall resistance can change continuously. Additionally, feedback loops may adjust rds,A from the supply voltage noise, just like in the ALDO. Then, with the supply voltage VIN-to-VOUT response mainly determined by the analog circuits, they allow a longer digital sampling interval (t4 to t5), and thus higher power consumption. Fig. 13(b) exhibits a topology that combines analog and digitized resistance classified as an hybrid LDO[

![]()

Figure 13.(a) Analog circuits help PSR improvement and (b) block diagram of the hybrid LDO.

Although the working principle of the PSR improving techniques in the digital/hybrid LDO are similar to those in the ALDO, there are two critical issues remaining. Firstly, we expect the current provided by the analog part to be small. Hence even with a continuously adjustable rds,A, this LDO fails to respond to a large supply ripple. Secondly, the limited supply voltage and dropout undermine the achievable PSR of the analog circuits.

Ref. [33] employed one ALDO array and one DLDO array, and proposed a feedforward PSR cancellation technique (Fig. 14(a)), implemented with a resistor and capacitor between the supply voltage and the gate node of the power transistor. It improves the light-load PSR, degraded at heavy load. To maintain the PSR performance, the architecture should comprise more ALDOs and less DLDOs under heavy load conditions.

![]()

Figure 14.Improving PSR using (a) feedforward PSR cancellation[

As presented in Fig. 14 (b), Refs. [34, 35] added an active replica loop to enhance the PSR. The main part of the ALDO constructed from a flipped voltage follower (FVF)[

![]()

Figure 15.(Color online) Simulated PSRs of the conventional DLDO, hybrid LDOs without replica loop, and with replica loop.

4. Discussion and conclusion

With the development of efficient computing and granular power management techniques, the DLDO has drawn significant attention in recent years. When compared with its analog counterpart, the DLDO suits well the requirements of low voltage operation and process scalability. However, inferior performances in the transient response, recovery, and PSR prevent its further application. Previous works proposed partially address these issues. Alternatively, analog techniques complementary to the DLDO can improve the transient response and the PSR. Yet, the achieved PSR so far is still too low to supply analog or RF circuits.

For the future design trends, it would not be easy for the DLDO to achieve a similar or even better performance than the ALDO, at circuit level. Instead, the performance should be significantly improved in the digital domain, or at the system-level. For instance, to maintain the stability and fast response, the PID coefficients were dynamically set in Ref. [39] through a digital calibration algorithm. Meanwhile, Ref. [40] proposed a computational scheme to determine the duration of the fully turn-on/turn-off power transistor array, for a very fast transient response. It would be possible to incorporate machine-learning techniques to predict, study, and respond to the load and supply changes. Moreover, fully synthesizable DLDOs[

![]()

Figure 16.(Color online) Multi-LDOs assisting a neighboring load step.

Acknowledgements

This work was supported by the National Natural Science Foundation of China (No. 61974046), the Provincial Key Research and Development Program of Guangdong (2019B010140002), the Macao Science & Technology Development Fund (FDCT) 145/2019/A3 and SKL-AMSV(UM)-2020-2022.

References

[1] P A Meinerzhagen, C Tokunaga, A Malavasi et al. An energy-efficient graphics processor in 14-nm tri-gate CMOS featuring integrated voltage regulators for fine-grain DVFS, retentive sleep, and

[2]

[3] S Chong, P K Chan. A 0.9-

[4] Y Lu, Y P Wang, Q Pan et al. A fully-integrated low-dropout regulator with full-spectrum power supply rejection. IEEE Trans Circuits Syst I, 62, 707(2015).

[5] M Huang, H G Feng, Y Lu. A fully integrated FVF-based low-dropout regulator with wide load capacitance and current ranges. IEEE Trans Power Electron, 34, 11880(2019).

[6]

[7] C J Park, M Onabajo, J Silva-Martinez. External capacitor-less low drop-out regulator with 25 dB superior power supply rejection in the 0.4–4 MHz range. IEEE J Solid-State Circuits, 49, 486(2014).

[8] Y Lu, R P Martins, U Seng-Pan et al. A 312 ps response-time LDO with enhanced super source follower in 28 nm CMOS. Electron Lett, 52, 1368(2016).

[9] V Gupta, G A Rincon-Mora, P Raha. Analysis and design of monolithic, high PSR, linear regulators for SoC applications. IEEE International SOC Conference, 311(2004).

[10] Y Okuma, K Ishida, Y Ryu et al. 0.5-V input digital LDO with 98.7% current efficiency and 2.7-

[11] M Huang, Y Lu, S W Sin et al. Limit cycle oscillation reduction for digital low dropout regulators. IEEE Trans Circuits Syst II, 63, 903(2016).

[12]

[13] M Huang, Y Lu, S W Sin et al. A fully integrated digital LDO with coarse-fine-tuning and burst-mode operation. IEEE Trans Circuits Syst II, 63, 683(2016).

[14] L G Salem, J Warchall, P P Mercier. A successive approximation recursive digital low-dropout voltage regulator with PD compensation and sub-LSB duty control. IEEE J Solid-State Circuits, 53, 35(2018).

[15]

[16] M Huang, Y Lu, S P U et al. An analog-assisted tri-loop digital low-dropout regulator. IEEE J Solid-State Circuits, 53, 20(2018).

[17] M Huang, Y Lu, X Lu. Partial analogue-assisted digital low dropout regulator with transient body-drive and 2.5 × FOM improvement. Electron Lett, 54, 282(2018).

[18]

[19] M A Akram, W Hong, I C Hwang. Fast transient fully standard-cell-based all digital low-dropout regulator with 99.97% current efficiency. IEEE Trans Power Electron, 33, 8011(2018).

[20]

[21]

[22]

[23]

[24] S Gangopadhyay, D Somasekhar, J W Tschanz et al. A 32 nm embedded, fully-digital, phase-locked low dropout regulator for fine grained power management in digital circuits. IEEE J Solid-State Circuits, 49, 2684(2014).

[25] S Kundu, M Q Liu, S J Wen et al. A fully integrated digital LDO with built-in adaptive sampling and active voltage positioning using a beat-frequency quantizer. IEEE J Solid-State Circuits, 54, 109(2019).

[26] Y H Lee, S Y Peng, C C Chiu et al. A low quiescent current asynchronous digital-LDO with PLL-modulated fast-DVS power management in 40 nm SoC for MIPS performance improvement. IEEE J Solid-State Circuits, 48, 1018(2013).

[27] F Yang, P K T Mok. A nanosecond-transient fine-grained digital LDO with multi-step switching scheme and asynchronous adaptive pipeline control. IEEE J Solid-State Circuits, 52, 2463(2017).

[28]

[29]

[30] Y N Zhang, H X Song, R R Zhou et al. A capacitor-less ripple-less hybrid LDO with exponential ratio array and 4000x load current range. IEEE Trans Circuits Syst II, 66, 36(2019).

[31] X Y Wang, P P Mercier. A dynamically high-impedance charge-pump-based LDO with digital-LDO-like properties achieving a sub-4-fs FoM. IEEE J Solid-State Circuits, 55, 719(2020).

[32] S B Nasir, S Sen, A Raychowdhury. Switched-mode-control based hybrid LDO for fine-grain power management of digital load circuits. IEEE J Solid-State Circuits, 53, 569(2018).

[33]

[34]

[35] M Huang, Y Lu, R P Martins. An analog-proportional digital-integral multiloop digital LDO with PSR improvement and LCO reduction. IEEE J Solid-State Circuits, 55, 1637(2020).

[36]

[37] Y F Li, X Y Zhang, Z Zhang et al. A 0.45-to-1.2-V fully digital low-dropout voltage regulator with fast-transient controller for near/subthreshold circuits. IEEE Trans Power Electron, 31, 6341(2016).

[38]

[39] A Singh, M Kar, V C K Chekuri et al. A digital low-dropout regulator with autotuned PID compensator and dynamic gain control for improved transient performance under process variations and aging. IEEE Trans Power Electron, 35, 3242(2020).

[40] K Z Ahmed, H K Krishnamurthy, C Augustine et al. A variation-adaptive integrated computational digital LDO in 22-nm CMOS with fast transient response. IEEE J Solid-State Circuits, 55, 977(2020).

[41]

[42] B Hershberg, S Weaver, K Sobue et al. Ring amplifiers for switched capacitor circuits. IEEE J Solid-State Circuits, 47, 2928(2012).

[43]

[44]

[45] P Hazucha, T Karnik, B A Bloechel et al. Area-efficient linear regulator with ultra-fast load regulation. IEEE J Solid-State Circuits, 40, 933(2005).

[46] Q H Duong, H H Nguyen, J W Kong et al. Multiple-loop design technique for high-performance low-dropout regulator. IEEE J Solid-State Circuits, 52, 2533(2017).

Set citation alerts for the article

Please enter your email address