Lixin Tian, Zechen Du, Rui Liu, Xiping Niu, Wenting Zhang, Yunlai An, Zhanwei Shen, Fei Yang, Xiaoguang Wei. Influence of epitaxial layer structure and cell structure on electrical performance of 6.5 kV SiC MOSFET[J]. Journal of Semiconductors, 2022, 43(8): 082802

Search by keywords or author

- Journal of Semiconductors

- Vol. 43, Issue 8, 082802 (2022)

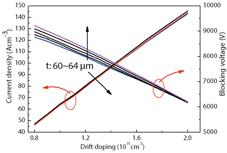

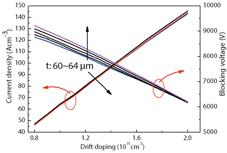

Fig. 1. (Color online) Current density and blocking voltage variation with doping concentration and thickness of epitaxial layer.

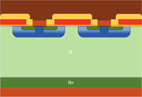

Fig. 2. (Color online) Schematic cross-section of 6.5 kV SiC MOSFET.

Fig. 3. (Color online) 6.5 kV SiC MOSFET devices on the 6-inch wafer.

Fig. 4. (Color online) Comparison of output current of five chips on three wafers.

Fig. 5. (Color online) Comparison of output, transfer and derivative parameters of five cell structures. (a) Output characteristic curves. (b) Transfer characteristic curves. (c) Transconductance comparison of different channel lengths. (d) Cell transconductance comparison of different JFET widths.

Fig. 6. (Color online) Breakdown characteristics of test pattern gate oxide capacitors.

Fig. 7. (Color online) The transforming curves of the gate oxide capacitor I–V curves.

Fig. 8. (Color online) The relationship between barrier height and slope.

Fig. 9. (Color online) 6.5 kV SiC MOSFET package layout and outline.

Fig. 10. High temperature gate bias reliability. (a) Forward gate voltage test results. (b) Reverse gate voltage test results.

Fig. 11. The results of high temperature reverse bias reliability.

|

Table 0. Chip yield of 3 wafers.

|

Table 0. Cell parameter table.

|

Table 0. Epitaxial layer thickness and doping concentration.

Set citation alerts for the article

Please enter your email address