[1] K Kuhn. Considerations for ultimate CMOS scaling. IEEE Trans Electron Devices, 59, 1813(2012).

[2] C Auth, A Aliyarukunju, M Asoro et al. A 10 nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, self-aligned quad patterning, contact over active gate and cobalt local interconnects. IEDM Tech Dig, 29.1(2017).

[3] S Narasimha, B Jagannathan, A Ogino et al. A 7 nm CMOS technology platform for mobile and high performance compute application. IEDM Tech Dig, 29.5(2017).

[4]

[5] K Rim, J Welser, J L Hoyt et al. Enhanced hole mobilities in surface-channel strained-Si p-MOSFETs. IEDM Tech Dig, 517(1995).

[6] S Takagi, J L Hoyt, J J Welser et al. Comparative study of phonon-limited mobility of two-dimensional electrons in strained and unstrained Si metal–oxide–semiconductor field-effect transistors. J Appl Phys, 80, 1567(1996).

[7] S Takagi, T Mizuno, T Tezuka et al. Channel structure design, fabrication and carrier transport properties of strained-Si/SiGe-on-insulator (strained-SOI) MOSFETs. IEDM Tech Dig, 57(2003).

[8] H Shang, M M Frank, E P Gusev et al. Germanium channel MOSFETs: Opportunities and challenges. IBM J Res Dev, 50, 377(2006).

[9] K C Saraswat, C O Chui, T Krishnamohan et al. Ge based high performance nanoscale MOSFETs. Microelectron Eng, 80, 15(2005).

[10] S Gupta, R Chen, B Magyari-Kope et al. GeSn technology: Extending the Ge electronics roadmap. IEEE Tech Dig, 16.6(2011).

[11] X Gong, G Q Han, F Bai et al. Germanium-tin (GeSn) p-channel MOSFETs fabricated on (100) and (111) surface orientations with sub-400 oC Si2H6 passivation. IEEE Electron Device Lett, 34, 339(2013).

[12] R R Lieten, T Maeda, W Jevasuwan et al. Tensile-strained GeSn metal-oxide-semiconductor field-effect transistor devices on Si (111) using solid phase epitaxy. Appl Phys Exp, 6, 101301(2013).

[13] R Xie, T H Phung, W He et al. High mobility high-k/Ge pMOSFETs with 1 nm EOT – New concept on interface engineering and interface characterization. IEDM Tech Dig, 393(2008).

[14] J Mitard, C Shea, B DeJaeger et al. Impact of EOT scaling down to 0.85 nm on 70 nm Ge-pFETs technology with STI. VLSI Symp Tech Dig, 82(2009).

[15] Y Kamata, K Ikeda, Y Kamimuta et al. High-k/Ge p- & n-MISFETs with strontium germanide interlayer for EOT scalable CMIS application. VLSI Symp Tech Dig, 211(2009).

[16] S Gupta, B Vincent, B Yang et al. Towards high mobility GeSn channel nMOSFETs: Improved surface passivation using novel ozone oxidation method. IEDM Tech Dig, 16.2(2012).

[17] L Liu, R R Liang, J Wang et al. Hole mobility enhancement of GeSn/Ge pMOSFETs with an interlayer formed by Sn-assisted oxynitridation. ECS Solid State Lett, 3, Q76(2014).

[18] T Haffner, M A Mahjoub, S Labau et al. Improvement of the electrical performance of Au/Ti/HfO2/Ge0.9Sn0.1 p-MOS capacitors by using interfacial layers. Appl Phys Lett, 115, 171601(2019).

[19] Y Nakakita, R Nakane, T Sasada et al. Interface-controlled self-align source/drain Ge p-channel metal-oxide-semiconductor field-effect transistors fabricated using thermally oxidized GeO2 interfacial layers. Jpn J Appl Phys, 50, 010109(2011).

[20] K Morii, T Iwasaki, R Nakane et al. High performance GeO2/Ge nMOSFETs with source/drain junctions formed by gas phase doping. IEEE Electron Device Lett, 31, 1092(2010).

[21] C H Lee, T Nishimura, T Tabata et al. Ge MOSFETs performance: Impact of Ge interface passivation. IEDM Tech Dig, 416(2010).

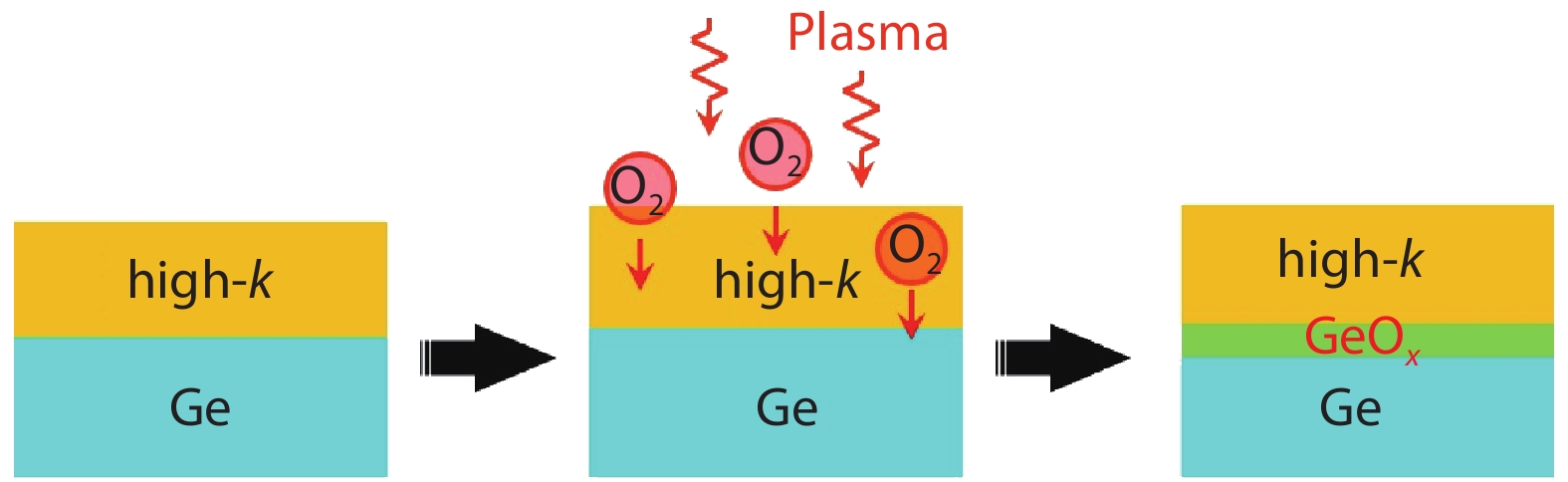

[22] R Zhang, T Iwasaki, N Taoka et al. Al2O3/GeOx/Ge gate stacks with low interface trap density fabricated by electron cyclotron resonance plasma postoxidation. Appl Phys Lett, 98, 112902(2011).

[23] R Zhang, T Iwasaki, N Taoka et al. Impact of GeO

[24] R Zhang, T Iwasaki, N Taoka et al. High-mobility Ge pMOSFET with 1-nm-thick EOT Al2O3/GeO

[25] R Zhang, P C Huang, J C Lin et al. High-mobility Ge p- and n-MOSFET with 0.7-nm EOT using HfO2/Al2O3/GeO

[26] N Taoka, K Ikeda, Y Yamashita et al. Quantitative evaluation of interface trap density in Ge-MIS interfaces. Ext Abst SSDM, 396(2006).

[27] H Matsubara, H Kumagai, S Sugahara et al. Evaluation of SiO2/GeO2/Ge MIS interface properties by low temperature conductance method. Ext Abst SSDM, 18(2007).

[28] K Martens, B D Jaeger, R Bonzom et al. New interface state density extraction method applicable to peaked and high-density distributions for Ge MOSFET development. IEEE Electron Device Lett, 27, 405(2006).

[29] J R Brews. Rapid interface parameterization using a single MOS conductance curve. Solid-State Electron, 26, 711(1983).

[30] G S Smith, P B Isaacs. The crystal structure of quartz-like GeO2. Acta Cryst, 17, 842(1964).

[31] S Van Elshocht, M Caymax, T Conard et al. Effect of hafnium germinate formation on the interface of HfO2/germanium metal oxide semiconductor devices. Appl Phys Lett, 88, 141904(2006).

[32] M Houssa, G Pourtois, M Caymax et al. First-principles study of the structural and electronic properties of (100) Ge/Ge(M)O2 interfaces (M = Al, La, or Hf). Appl Phys Lett, 92, 242101(2008).

[33] S Migita, Y Watanabe, H Ota et al. Design and demonstration of very high-k (k similar to 50) HfO2 for ultra-scaled Si CMOS. VLSI Symp Tech Dig, 119(2008).

[34] P Tsipas, S N Volkos, A Sotiropoulos et al. Germanium-induced stabilization of a very high-k zirconia phase in ZrO2/GeO2 gate stacks. Appl Phys Lett, 93, 082904(2008).

[35] D Tsoutsou, G Apostolopoulos, S Galata et al. Stabilization of a very high-k tetragonal ZrO2 phase by direct doping with germanium. Microelectron Eng, 86, 1626(2009).

[36] Y Oshima, M Shandalov, Y Sun et al. Hafnium oxide/germanium oxynitride gate stacks on germanium: Capacitance scaling and interface state density. Appl Phys Lett, 94, 183102(2009).

[37] C H Fu, K S Chang-Liao, L J Liu et al. An ultralow EOT Ge MOS device with tetragonal HfO2 and high quality Hf

[38] G Han, S Su, C Zhan, Q Zhou et al. High-mobility germanium-tin (GeSn) p-channel MOSFETs featuring metallic source/drain and sub-370 oC process modules. IEDM Tech Dig, 402(2011).

[39] S Gupta, Y C Huang, Y Kim et al. Hole enhancement in compressively strained Ge0.93Sn0.07 pMOSFETs. IEEE Electron Device Lett, 34, 58(2013).

[40] M Liu, G Han, Y Liu et al. Undoped Ge0.92Sn0.08 quantum well pMOSFETs on (001), (011) and (111) substrates with in situ Si2H6 passivation: High hole mobility and dependence of performance on orientation. VLSI Symp Tech Dig, 100(2014).

[41] T Mizuno, S Takagi, N Sugiyama et al. Electron and hole mobility enhancement in strained-Si MOSFET's on SiGe-on-insulator substrates fabricated by SIMOX technology. IEEE Electron Device Lett, 21, 230(2000).

[42] S E Thompson, M Armstrong, C Auth et al. A 90-nm logic technology featuring strained-silicon. IEEE Trans Electron Device, 51, 1790(2004).

[43] M L Lee, E A Fitzgerald, M T Bulsara et al. Strained Si, and Ge channels for high-mobility metal –oxide –semiconductor field-effect transistors. J Appl Phys, 97, 011101(2005).

[44] S Nakaharai, T Tezuka, N Sugiyama et al. Characterization of 7-nm-thick strained Ge-on-insulator layer fabricated by Ge-condensation technique. Appl Phys Phys, 83, 3516(2003).

[45] T Krishnamohan, Z Krivokapic, K Uchida et al. High-mobility ultrathin strained Ge MOSFETs on bulk and SOI with low band-to-band tunneling leakage: Experiments. IEEE Trans Electron Devices, 53, 990(2006).

[46] S Gupta, B Magyari-Kope, Y Nishi et al. Achieving direct band gap in germanium through integration of Sn alloying and external strain. J Appl Phys, 113, 073707(2014).

[47] Y Yang, K L Low, W Wang et al. Germanium-tin n-channel tunneling field-effect transistor: Device physics and simulation study. J Appl Phys, 113, 194507(2013).