Jiaxin Liu, Xiyuan Tang, Linxiao Shen, Shaolan Li, Zhelu Li, Wenjuan Guo, Nan Sun. Error suppression techniques for energy-efficient high-resolution SAR ADCs[J]. Journal of Semiconductors, 2020, 41(11): 111403

Search by keywords or author

- Journal of Semiconductors

- Vol. 41, Issue 11, 111403 (2020)

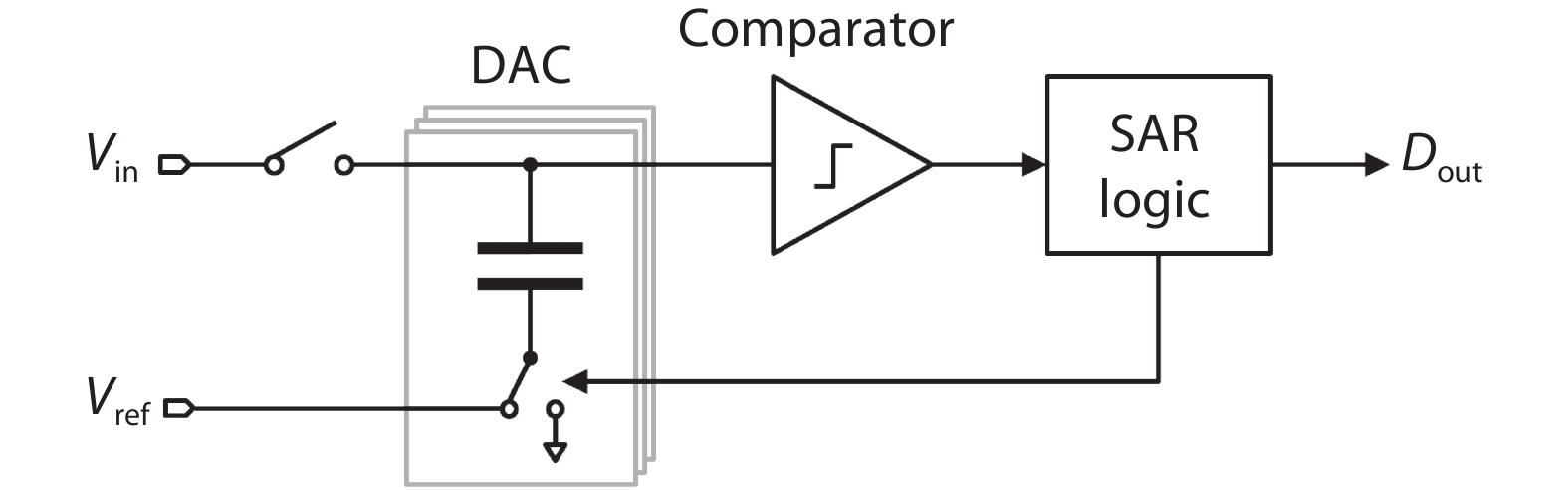

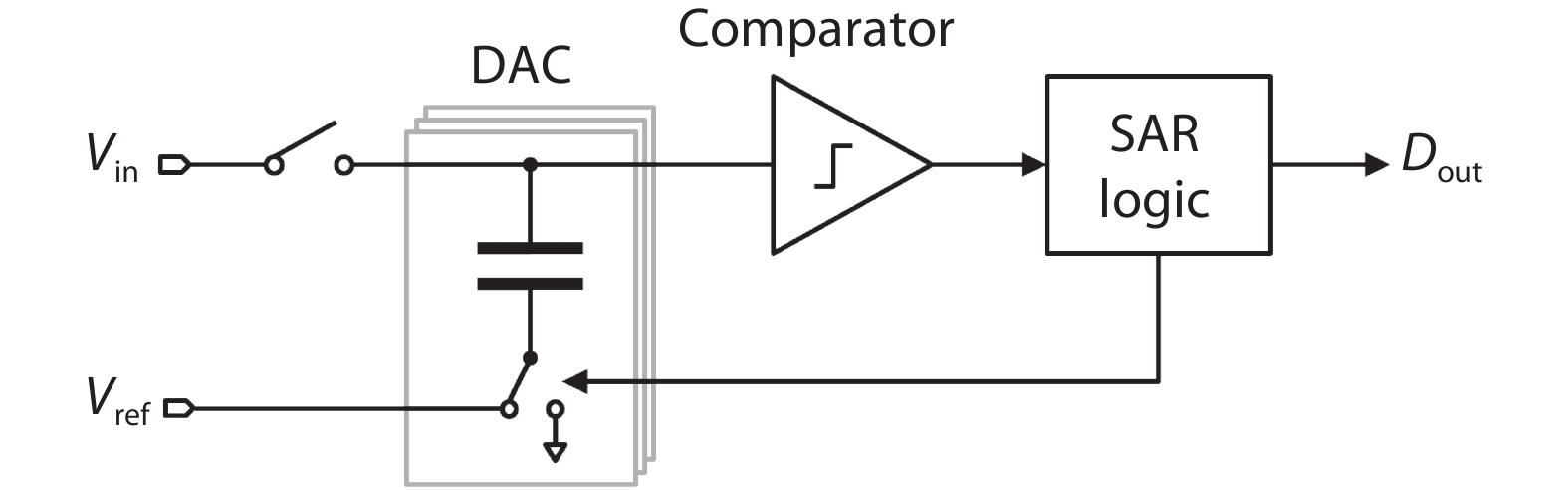

Fig. 1. Generic block diagram of a SAR ADC.

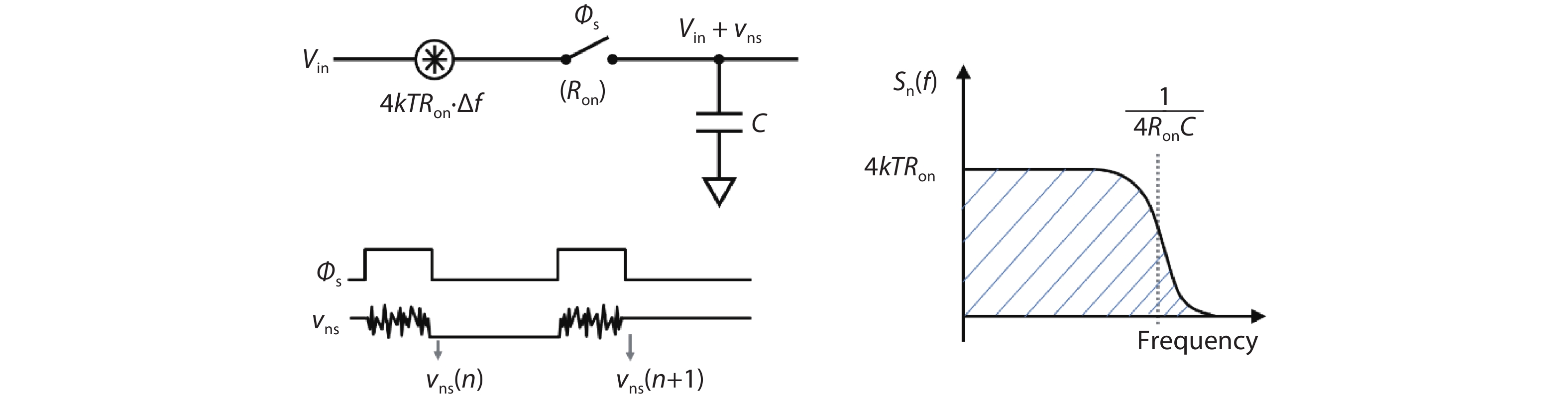

Fig. 2. A sampling circuit with kT /C noise.

Fig. 3. Strong-ARM latch[1 ].

Fig. 4. A SAR ADC with DAC mismatch: (a) operation scheme, (b) behavioral operation model.

Fig. 5. Two-step SAR ADC with a continuous-time first stage[3 ].

Fig. 6. SAR ADC with kT /C noise cancellation[4 ].

Fig. 7. kT /C noise reduction by decoupling Noise PSD and bandwidth[11 ].

Fig. 8. Generic block diagram of a NS- SAR ADC.

Fig. 9. NS-SAR ADC with close-loop amplifier-based noise-shaping filter[12 ].

Fig. 10. Closed-Loop Dynamic Amplifier-based noise-shaping filter[15 ].

Fig. 11. Open-loop dynamic amplifier-based NS-SAR[16 ].

Fig. 12. NS-SAR ADC with EF structure and open-loop dynamic amplifier[17 ].

Fig. 13. (a) Simplified core schematic and (b) 3-input-pair comparator of the second-order NS-SAR ADC[22 ].

Fig. 14. (Color online) Operation of the NS SAR ADC in Ref. [26 ]: (a) integration phase, (b) conversion phase.

Fig. 15. (Color online) A SAR ADC with first-order EF MES[13 ].

Fig. 16. (Color online) Second-order EF MES with digital prediction[26 ].

Set citation alerts for the article

Please enter your email address