Zhi LIU, Guodong GAO, Junhui YUE, Jianshe CAO, Yaoyao DU, Huizhou MA, Jun HE, Qiang YE, Xuhui TANG, Yukun LI, Jing YANG, Shujun WEI. Design and verification of data acquisition clock circuit based on dual-loop phase-locked loop[J]. NUCLEAR TECHNIQUES, 2022, 45(10): 100401

Search by keywords or author

- NUCLEAR TECHNIQUES

- Vol. 45, Issue 10, 100401 (2022)

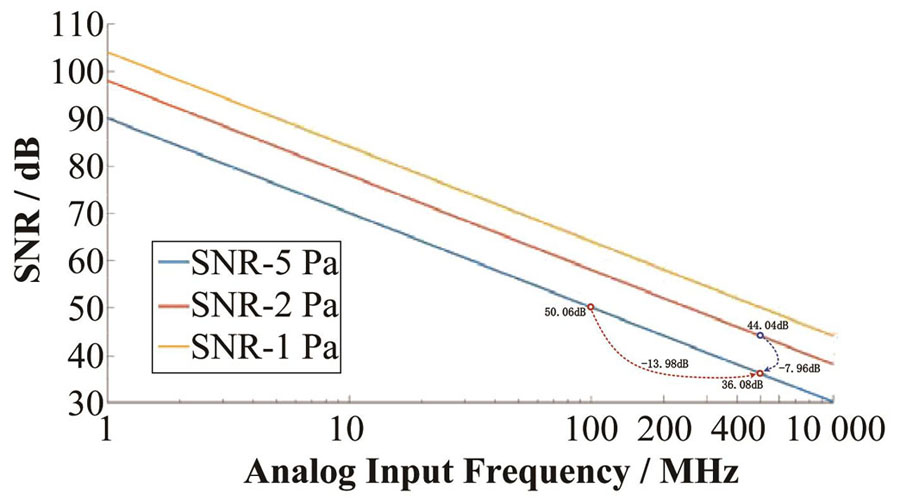

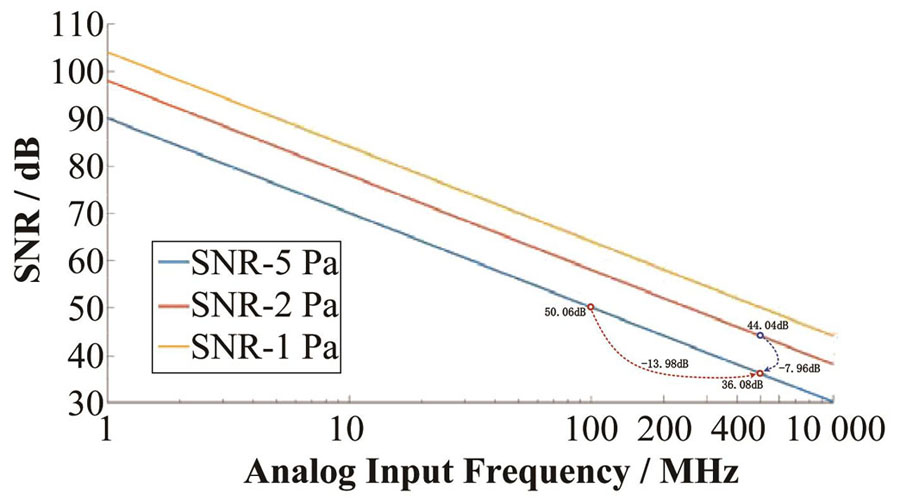

Fig. 1. SNR of ADC when clock jitter is 1 ps, 2 ps and 5 ps

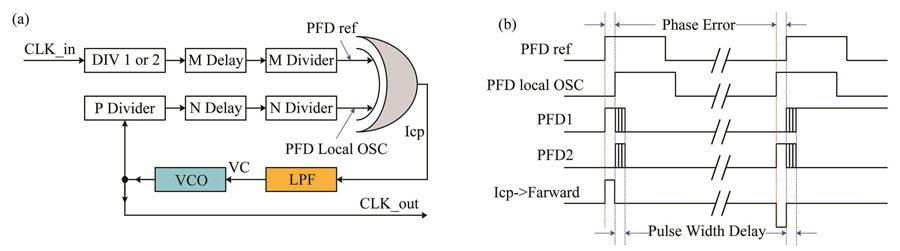

Fig. 2. The working principle of PLL

Fig. 3. Simplified functional block diagram for LMK04610

Fig. 4. Block diagram of dual-loop phase-locked loop system overall design

Fig. 5. Diagrammatic drawing of power supply design

Fig. 6. Diagrammatic drawing of the configuration circuit

Fig. 7. Equivalent circuit model of Balun (a), diagrammatic drawing of input/output (b)

Fig. 8. Design of PLL1 LPF and its phase noise

Fig. 9. Test for jitter performance (a) The jitter of source clock, (b) The jitter of processed clock

Fig. 10. SNR of ADC band-pass sampling data when the clock jitter is 1.8 ps

Set citation alerts for the article

Please enter your email address