Shan-Zhe YU, Ya-Cong ZHANG, Yu-Ze NIU, Ye ZHOU, Yi ZHUO, Ding MA, Wen-Gao LU, Zhong-Jian CHEN, Xiang-Yang LI. A 48 mW DROIC with 15-bit pixel-level ADC for 640×512 mid-wave infrared imagers[J]. Journal of Infrared and Millimeter Waves, 2022, 41(4): 785

Search by keywords or author

- Journal of Infrared and Millimeter Waves

- Vol. 41, Issue 4, 785 (2022)

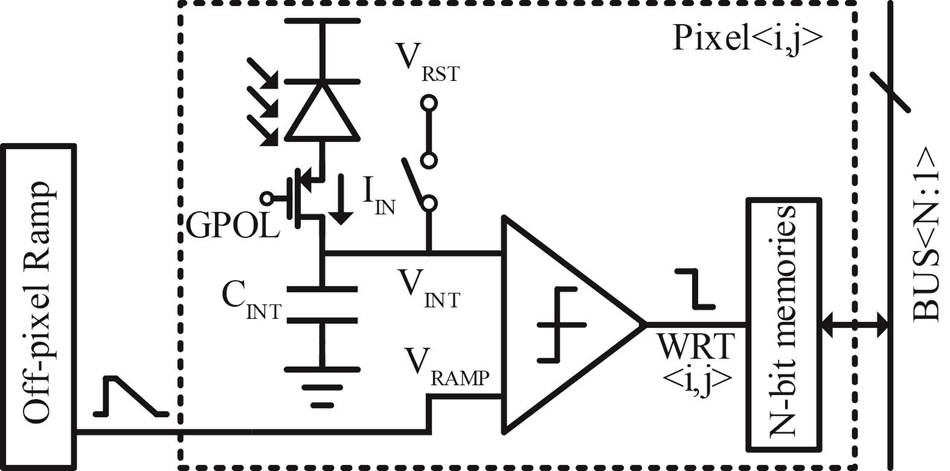

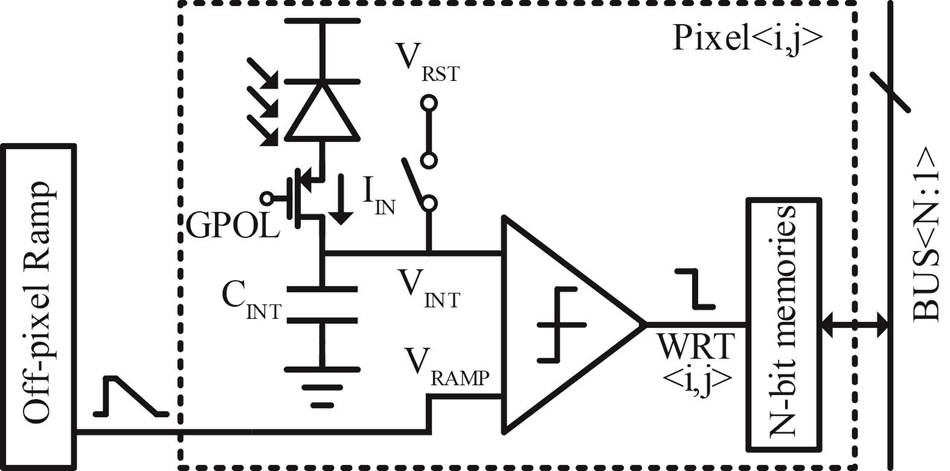

Fig. 1. Conventional digital pixel with SS-ADC

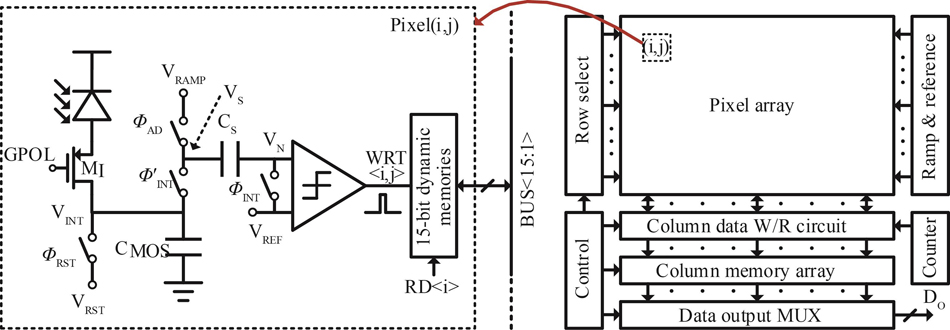

Fig. 2. Block diagram of the proposed DROIC with the novel pixel-level SS-ADC

Fig. 3. Timing diagram of the proposed DROIC

Fig. 4. (a)The circuit diagram,and(b)the timing diagram of proposed power-self-adaptive pulse comparator:(a)(b)

Fig. 5. Simulation results of

Fig. 6. The circuit diagram of the pixel dynamic memory and the column data W/R circuit

Fig. 7. (a)The microphotograph of the DROIC,(b)custom-designed PCB to test the DROIC

Fig. 8. the layout of 2×2 pixels

Fig. 9. Measured

Fig. 10. SNR histogram of the whole pixel array at the full well

Fig. 11. When

Fig. 12. The digital output versus the reset voltage

Fig. 13. The non-linearity versus the reset voltage

|

Table 1. Performance comparison of DROICs

Set citation alerts for the article

Please enter your email address