Yueer Shan, Zhengzhou Cao, Guozhu Liu. Research on eigenstate current control technology of Flash-based FPGA[J]. Journal of Semiconductors, 2022, 43(12): 122401

Search by keywords or author

- Journal of Semiconductors

- Vol. 43, Issue 12, 122401 (2022)

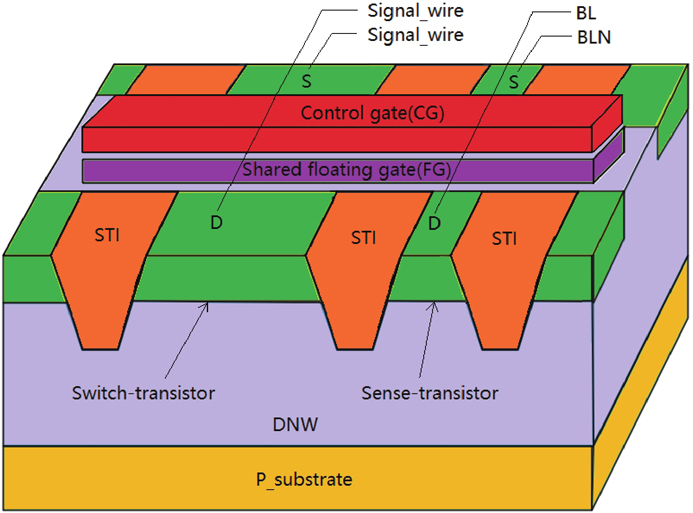

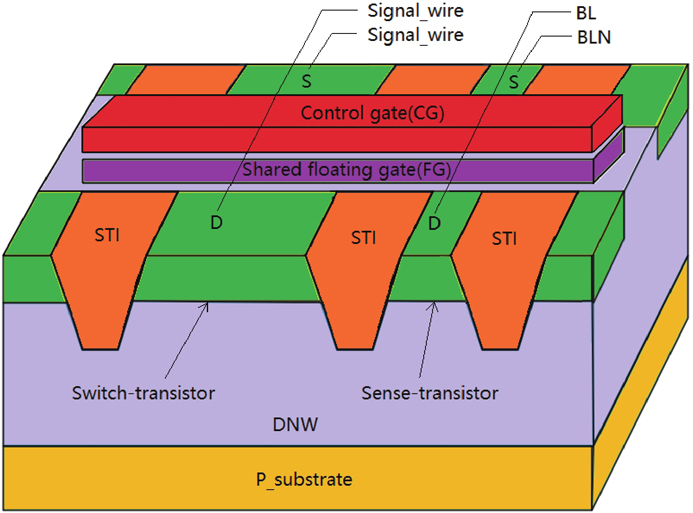

Fig. 1. (Color online) Structure of Flash switch unit.

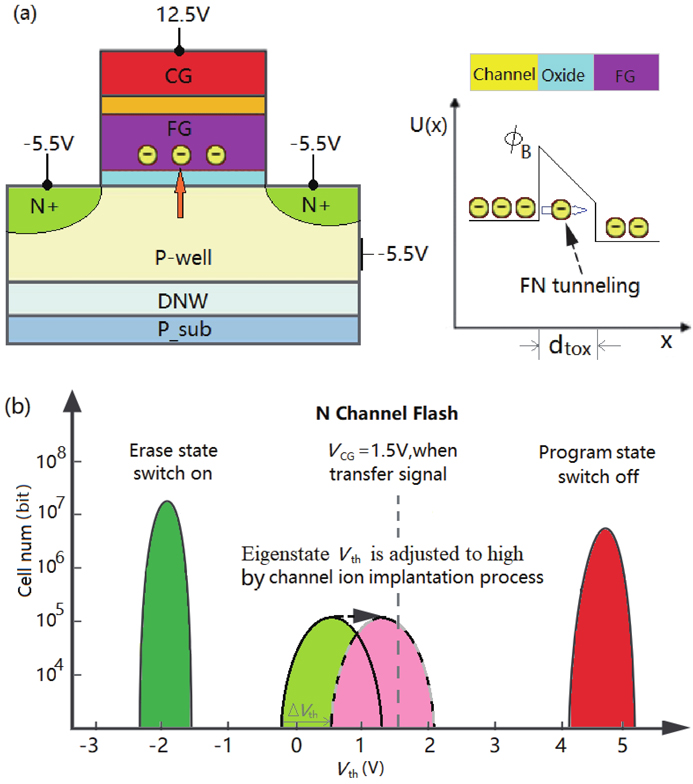

Fig. 2. (Color online) N-channel Flash. (a) Program(FN). (b) Threshold voltage distribution and adjust.

Fig. 3. (Color online) P-channel Flash. (a) Program(BTBTIHE). (b) Threshold voltage distribution and adjust.

Fig. 4. (Color online) Signal selector MUX use P-channel Flash.

Fig. 5. (Color online) Measured eigenstate threshold voltage of the Flash switch.

Fig. 6. (Color online) Energy band diagram of the Flash cell.

Fig. 7. (Color online) Spectrum of ultraviolet light.

Fig. 8. (Color online) Ultraviolet light erasing.

Fig. 9. (Color online) Metal wiring of Flash-based FPGA.

Fig. 10. (Color online) Relationship between threshold voltage drift and baking time.

Fig. 11. (Color online) Energy band diagram of floating gate structure under X-ray radiation ionization. (a) Programming state. (b) Erasing state.

Fig. 12. (Color online) Two logic control schemes for the first power-on. (a) Control the Flash gate. (b) Control the GND of core logic.

Fig. 13. (Color online) Voltage control of Flash cell gate.

Fig. 14. (Color online) GND to L_GND channel.

Fig. 15. (Color online) Control logic of L_GND channel switch.

Fig. 16. (Color online) Competition between voltage and current during power-on.

Fig. 17. Flash cell PCM.

Fig. 18. (Color online) A 3.5 million Flash-based FPGA.

Fig. 19. (Color online) UVC irradiation test. (a) Flash cell PCM. (b) Flash-based FPGA.

Fig. 20. (Color online) X-ray irradiation test. (a) Flash cell PCM. (b) Flash-based FPGA.

Fig. 21. (Color online) High temperature baking test. (a) Flash cell PCM. (b) Flash-based FPGA.

Fig. 22. (Color online) Power-on waveform. (a) Circuit without path control of power supply. (b) Circuit with path control of power supply.

Fig. 23. (Color online) Power-on current of the circuit with path control of power supply at –55, 25 and 125 °C.

|

Table 1. Comparison of four methods.

Set citation alerts for the article

Please enter your email address