Meng Zhang, Ruo-He Yao, Yu-Rong Liu. A channel thermal noise model of nanoscaled metal-oxide-semiconductor field-effect transistor [J]. Acta Physica Sinica, 2020, 69(5): 057101-1

Search by keywords or author

- Acta Physica Sinica

- Vol. 69, Issue 5, 057101-1 (2020)

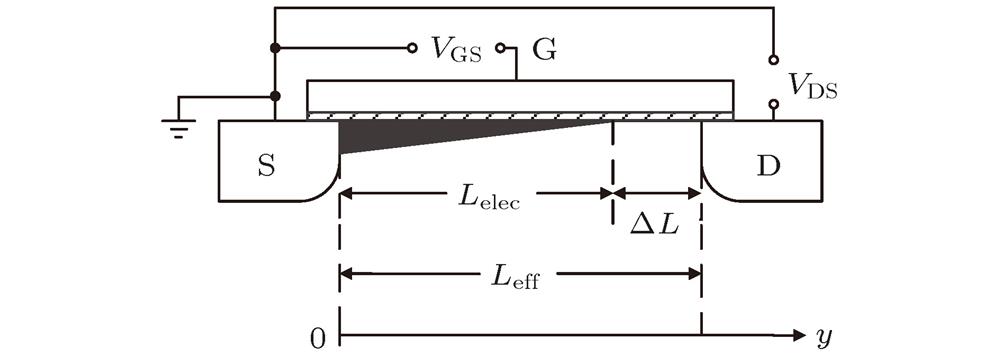

Fig. 1. Structure diagram of the NMOS device.

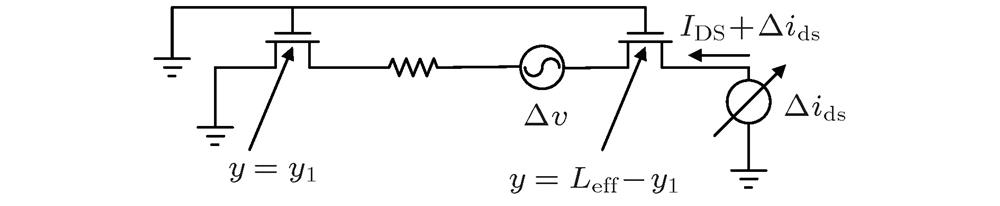

Fig. 2. Schematic of the transistor with a fictitious dc source placed at point y = y 1 in the channel.

Fig. 3. The channel thermal noise at different gate-source bias: (a) Comparison with the model only considering the channel length modulation effect; (b) comparison with the model using the existing temperature model.

Fig. 4. The channel thermal noise at different gate-source bias (L eff = 0.13 μm).

|

Table 1.

Parameters of NMOS.

NMOS的器件参数

Set citation alerts for the article

Please enter your email address