Hyunil Byun, Jinkwon Bok, Kwansik Cho, Keunyeong Cho, Hanmei Choi, Jinyong Choi, Sanghun Choi, Sangdeuk Han, Seokyong Hong, Seokhun Hyun, T. J. Jeong, Ho-Chul Ji, In-Sung Joe, Beomseok Kim, Donghyun Kim, Junghye Kim, Jeong-Kyoum Kim, Kiho Kim, Seong-Gu Kim, Duanhua Kong, Bongjin Kuh, Hyuckjoon Kwon, Beomsuk Lee, Hocheol Lee, Kwanghyun Lee, Shinyoung Lee, Kyoungwon Na, Jeongsik Nam, Amir Nejadmalayeri, Yongsang Park, Sunil Parmar, Junghyung Pyo, Dongjae Shin, Joonghan Shin, Yong-hwack Shin, Sung-Dong Suh, Honggoo Yoon, Yoondong Park, Junghwan Choi, Kyoung-Ho Ha, and Gitae Jeong, "Bulk-Si photonics technology for DRAM interface [Invited]," Photonics Res. 2, A25 (2014)

Search by keywords or author

- Photonics Research

- Vol. 2, Issue 3, A25 (2014)

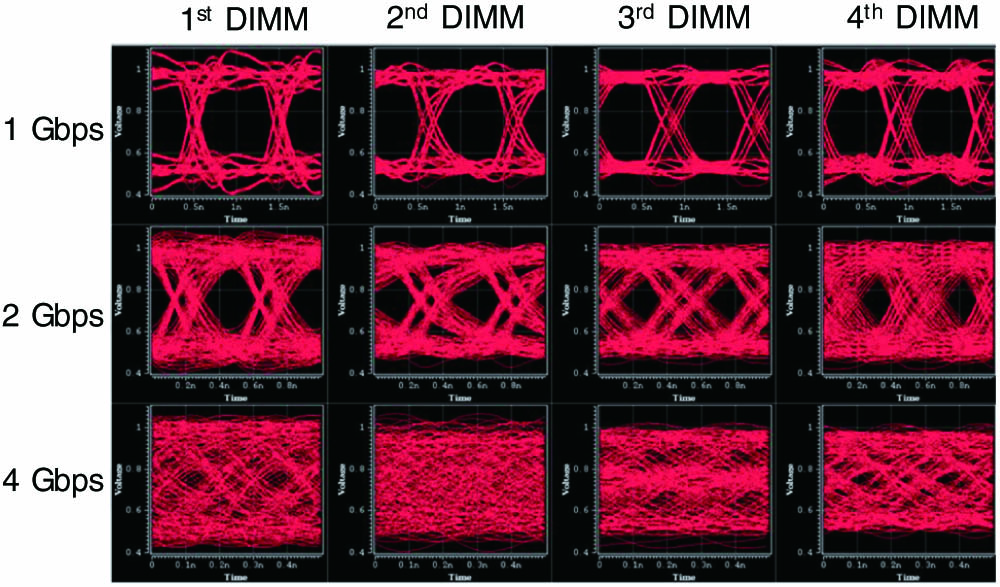

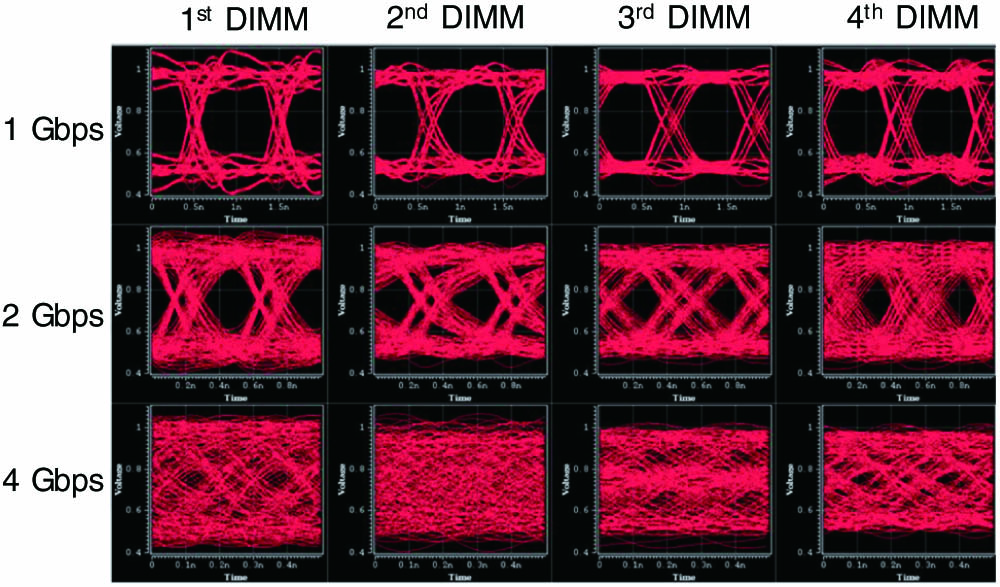

Fig. 1. Simulated eye diagrams of memory bus with 4 DIMMs in one DDR3 memory channel.

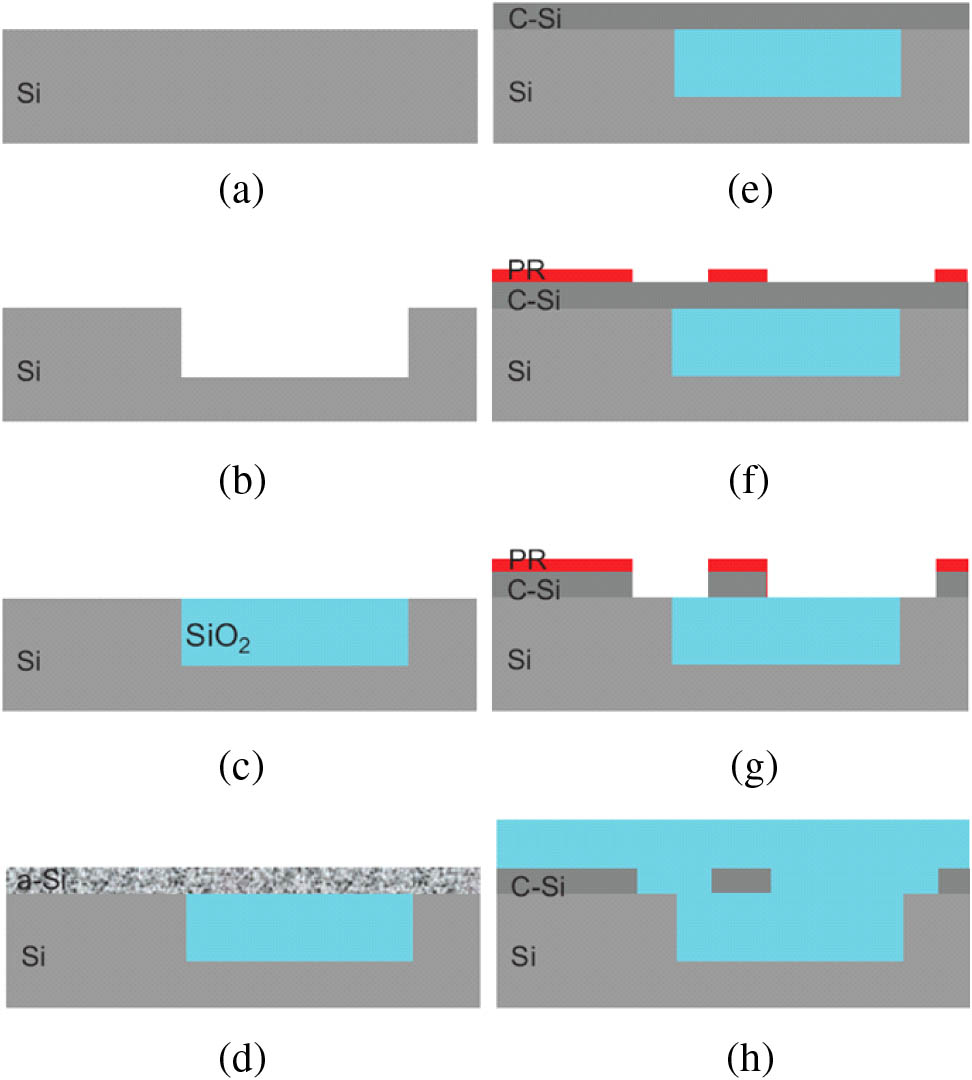

Fig. 2. Process steps for fabricating the waveguide on a bulk-Si substrate. C-Si: crystallized silicon, PR: photoresist.

Fig. 3. SEM images after crystallization of deposited a-Si depending on annealing condition: (a) low, (b) medium, and (c) high temperature.

Fig. 4. VSEM images of fabricated waveguide on the bulk-Si substrate.

Fig. 5. Cross section of inlaid structure for LEG process.

Fig. 6. High resolution TEM image and diffraction pattern: (a) SPE-Si and (b) LEG-Si.

Fig. 7. (a) Cross-sectional diagram of the active part of the bulk-Si MZI modulator. (b) SEM image of the dotted region in (a). The inclined arrows indicate the boundary of the local oxide undercladding formed underneath the active part. (c) Microscope image. Dotted line indicates the location of (a) and (b).

Fig. 8. Optical eye diagrams at NRZ 2 31 – 1 5 Gb / s 10 Gb / s

Fig. 9. (a) Lateral design of racetrack modulator with metal boundary illustrated. (b) Eye diagram at 1559.24 nm with 2.5 V pp

Fig. 10. (a) Microscope photography, (b) SEM image, and (c) 25 Gbp / s

Fig. 11. Schematic diagram of waveguide-type photodetector (a) along the light propagation, and (b) perpendicular to the light propagation. (c) VSEM image, (d) 15 Gb / s − 1 V 25 Gb / s − 7 V

Fig. 12. (a) Optical microscope image of EPIC, (b) schematic of EPIC vertical structure, and (c) SEM images of transistors, modulator, and Ge photodiode.

Fig. 13. Performance of the bulk-Si photonic devices integrated into the DRAM process.

Fig. 14. 1 × 4

Fig. 15. Electrical eye diagram measured at channel 1–4 receiver: (a) through (d) with the transmitter in a QFP package, (e) through (h) on a bare die.

Fig. 16. Block diagram of an optical interconnect transceiver. PD: photodiode, MOD: modulator.

Fig. 17. (a) Photograph of dies for PIC and EIC. (b) Photograph of copackaged optical transceiver chip.

Fig. 18. (a) Experiment setup to verify link operation using two optical transceivers. (b) and (c) Eye diagram at the output of optical amplifier at data rate of 1.5 and 2.5 Gb / s

Fig. 19. (a) Photograph and (b) block diagram of the experiment setup to verify optically interconnected DRAM interface. A: optical amplifier.

Fig. 20. (a) Block diagram of the experiment setup and (b) oscilloscope traces for DQ0 (blue) and DQS signals (red) at controller side and DRAM side with output enable signals (green).

Set citation alerts for the article

Please enter your email address