Jingjing Shi, Yadong Hu, Mengfan Li, Bin Sun, Gai Wang, Gaojun Chi, Xiangjing Wang, Jin Hong. Design and Implementation of Cloud Camera Control System[J]. Acta Optica Sinica, 2020, 40(20): 2001001

Search by keywords or author

- Acta Optica Sinica

- Vol. 40, Issue 20, 2001001 (2020)

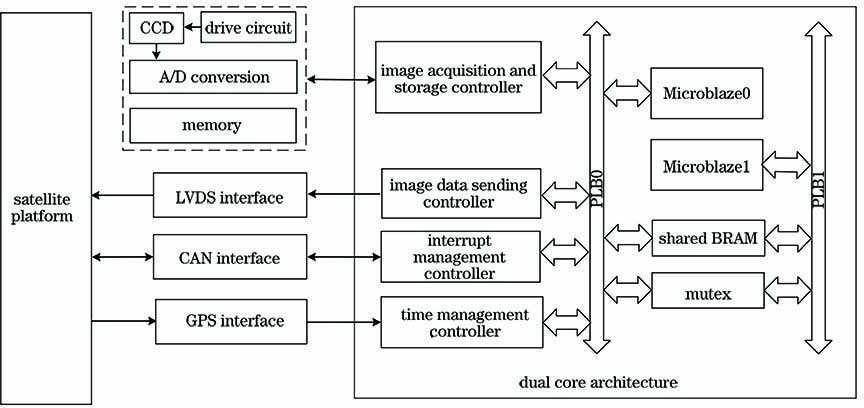

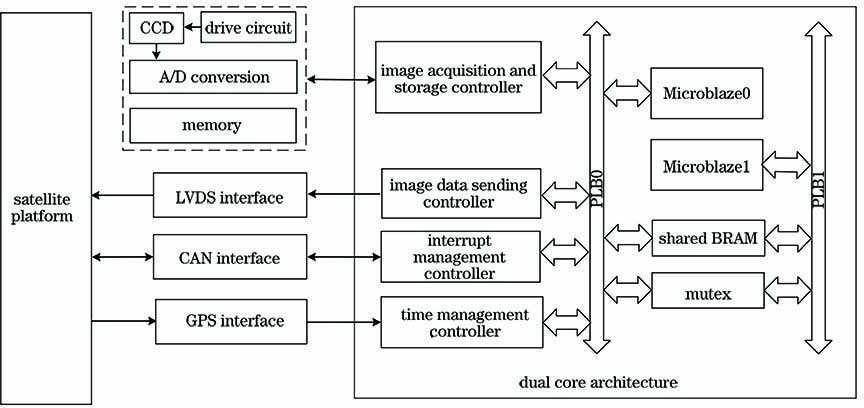

Fig. 1. Block diagram of cloud camera electronics system

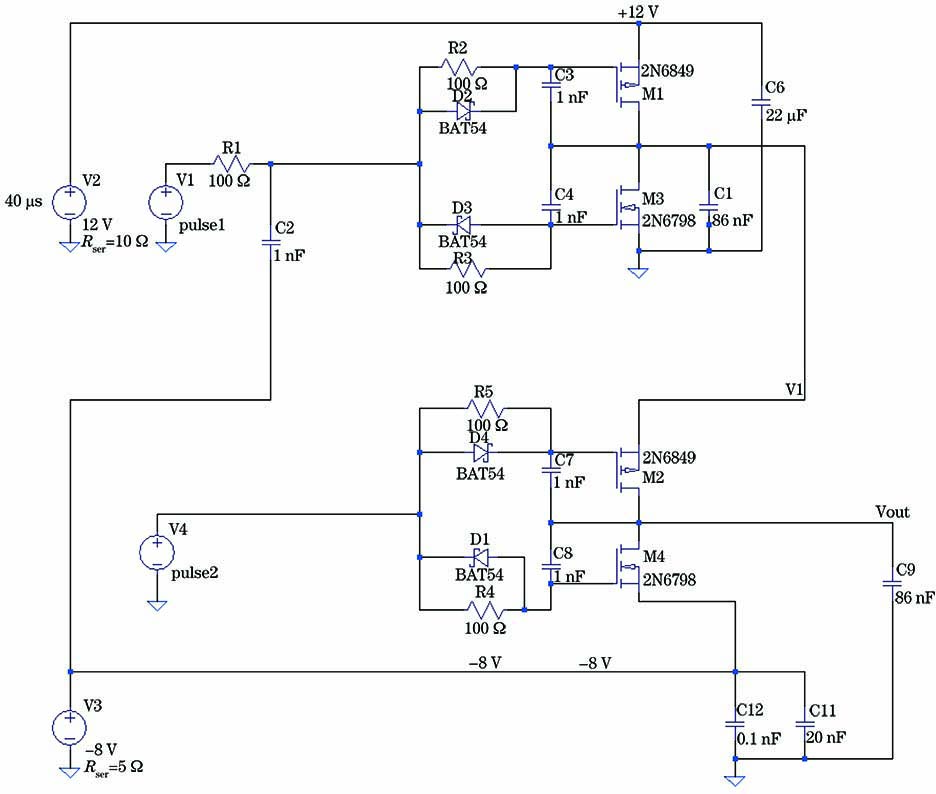

Fig. 2. Three-level pulse signal driving circuit

Fig. 3. Simulation diagram of three-level pulse signal

Fig. 4. Driving circuit of electronic shutter

Fig. 5. Frame transfer timing, pixel readout timing, and electronic shutter timing. (a) Frame transfer timing; (b) pixel readout timing; (c) electronic shutter timing

Fig. 6. Vertical clock, horizontal clock and reset signal,and electronic shutter. (a) Vertical clock; (b) horizontal clock and reset signal; (c) electronic shutter

Fig. 7. SDRAM initialization process, and diagram of working state transition. (a) SDRAM initialization process; (b) diagram of working state transition

Fig. 8. CCD data acquisition and storage IP core

Fig. 9. Block diagram of performance test

Fig. 10. Camera performance test site

Fig. 11. Measurement results of dark current noise

Fig. 12. Relationship between output signal value and exposure time

|

Table 1. CCD drive signal levels and equivalent capacitances

|

Table 2. Camera SNR at different exposure time

Set citation alerts for the article

Please enter your email address