Chunyou Su, Sheng Zhou, Liang Feng, Wei Zhang. Towards high performance low bitwidth training for deep neural networks[J]. Journal of Semiconductors, 2020, 41(2): 022404

Search by keywords or author

- Journal of Semiconductors

- Vol. 41, Issue 2, 022404 (2020)

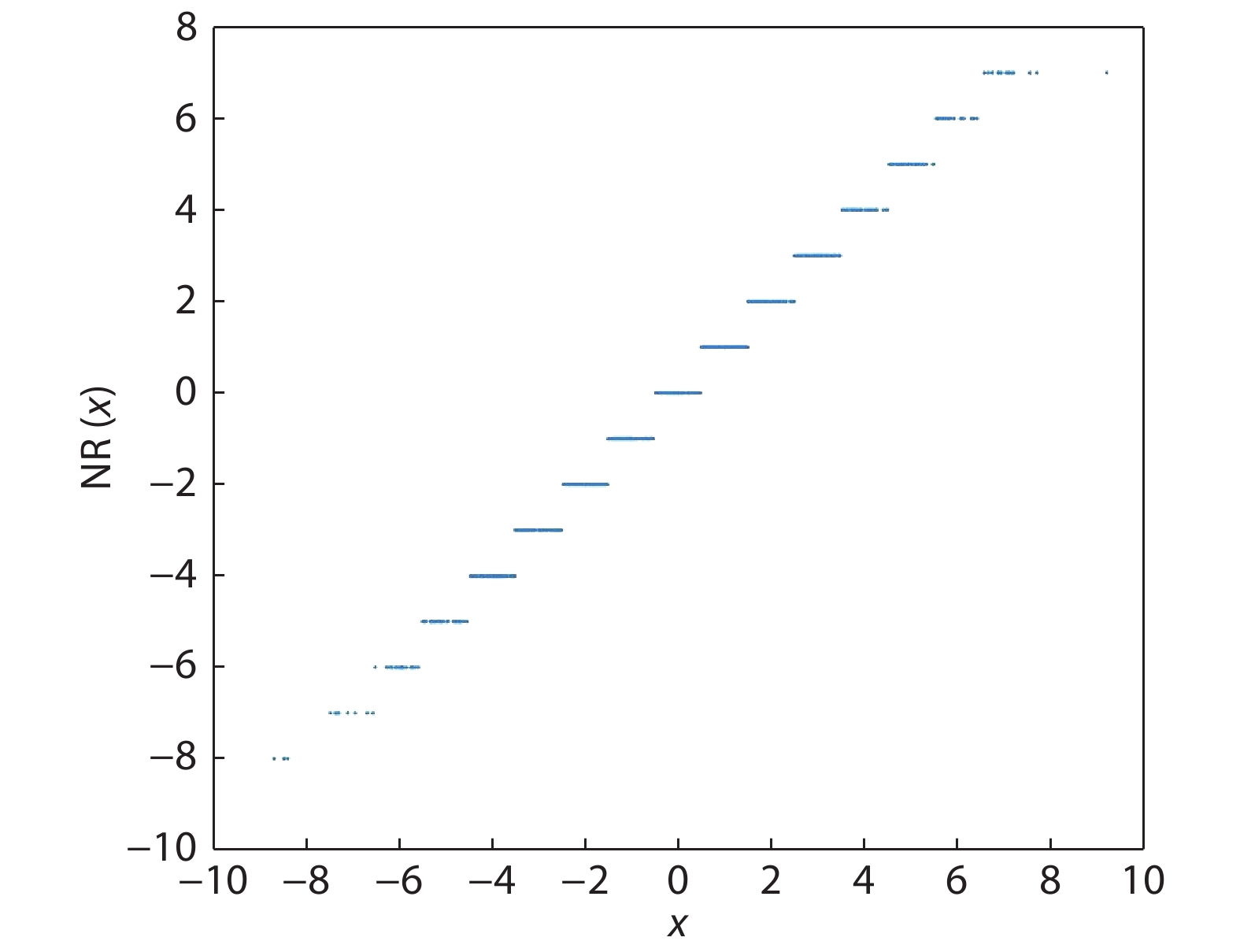

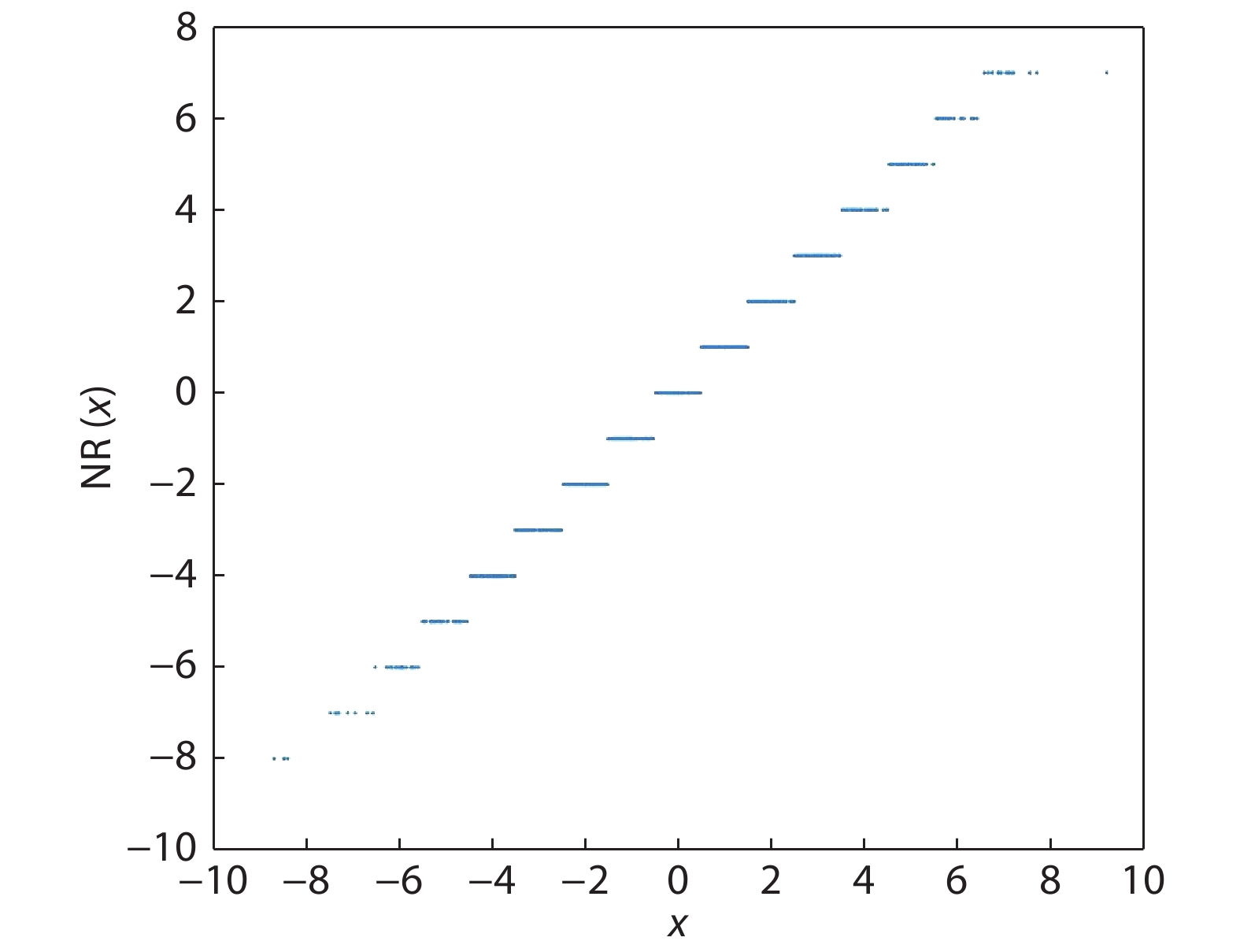

Fig. 1. NR simulation.

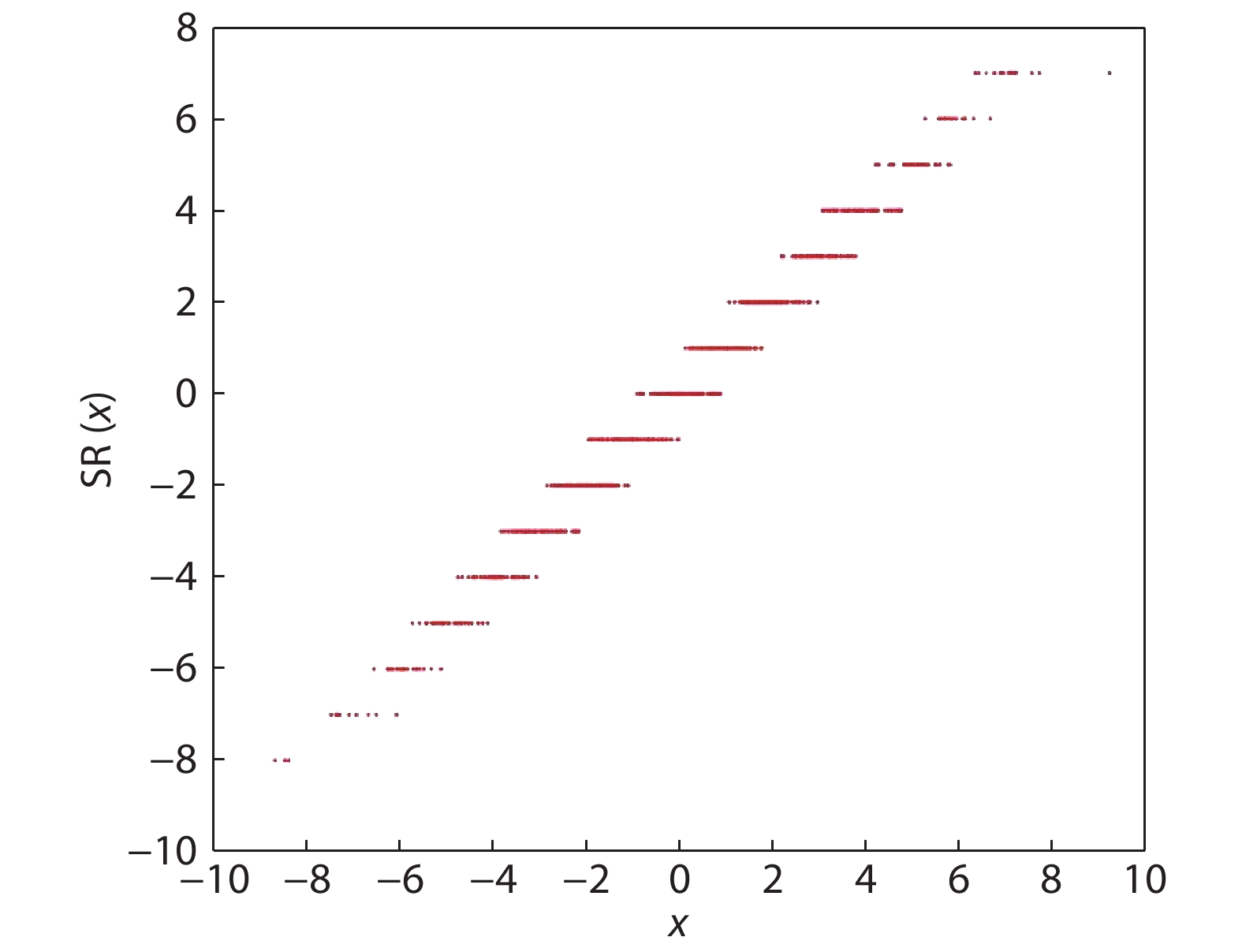

Fig. 2. SR simulation.

Fig. 3. Execution modules.

Fig. 4. Whole design structure.

Fig. 5. Module structure example.

Fig. 6. Random number generator.

|

Table 1. Top-1 accuracy of 8-bit AlexNet and ResNet18, SR versus NR.

|

Table 2. Top-1 accuracy on CIFAR-10 dataset.

|

Table 3. Top-1 accuracy on ImageNet dataset.

|

Table 4. Resource usage of FPGA prototyping.

Set citation alerts for the article

Please enter your email address