Peng Bao, Qixiang Cheng, Jinlong Wei, Giuseppe Talli, Maxim Kuschnerov, Richard V. Penty, "Harnessing self-heating effect for ultralow-crosstalk electro-optic Mach–Zehnder switches," Photonics Res. 11, 1757 (2023)

Search by keywords or author

- Photonics Research

- Vol. 11, Issue 10, 1757 (2023)

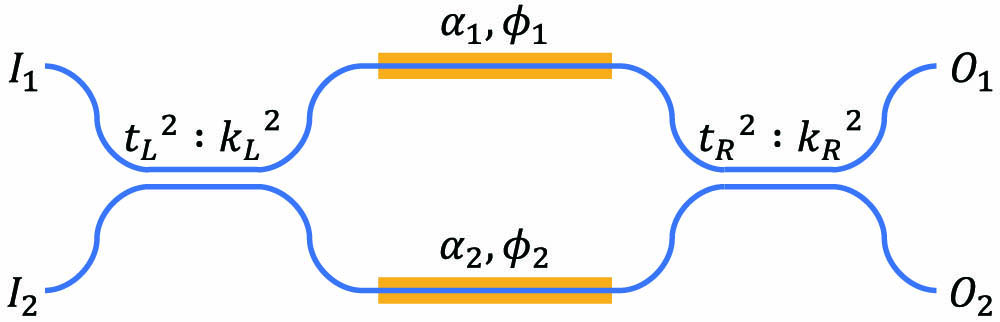

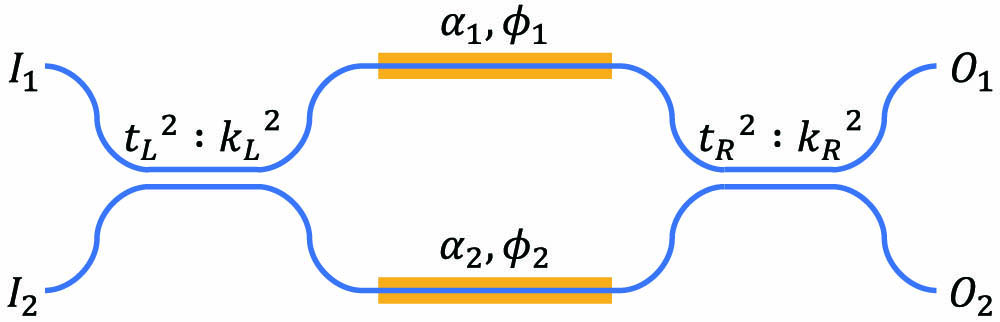

Fig. 1. Schematic of a 2 × 2

Fig. 2. Cross-section schematic of the differential E-O phase shifter pair.

Fig. 3. (a) Insertion loss for the E-O phase shifter with varying lightly doped region widths (0–2 μm) plotted against absolute phase shift for different device lengths. (b) and (c) Insertion loss and phase shift for 50-μm- and 1000-μm-long E-O phase shifters against bias voltage. Both phase shifters share a common lightly doped region width of 2 µm. (d) and (e) Insertion loss for the E-O phase shifter with a 50 μm length and 2 μm lightly doped region width, plotted against absolute phase shift for different doping concentrations. (f) Insertion loss for the E-O phase shifter with a 1000 μm length and no lightly doped region, plotted against phase shift for different doping concentrations. Note that the dark curves in (d)–(f) represent the projection of the original 3D curves onto the loss–bias plane.

Fig. 4. (a) Insertion loss of E-O phase shifters plotted against the provided phase shift, with the yellow dashed line representing PS2 at 30 μm length. (b) Insertion loss of the differential E-O phase shifter pair plotted against the provided phase shift, featuring a red dashed line for PS2 at the 30 μm length. (c) Current in the two E-O phase shifters plotted against the applied bias voltage.

Fig. 5. (a) τ rise τ rise τ rise τ fall

Fig. 6. (a) Schematic of the CTDC. (b) Wavelength response for the CTDC under different width variation values. (d) Cross-coupling ratio at 1.55 μm versus the power dissipated for the CTDC.

Fig. 7. (a)–(c) Schematics of the three configurations. (d)–(f) Transmission spectra for each configuration in the cross and bar states under different width variations.

Fig. 8. Distribution of crosstalk ratio at 1.55 μm (left) and bandwidth at crosstalk of − 30 dB

Fig. 9. (a) Overall power penalty histograms for PILOSS (top) and DLN (bottom) switches at different scales, featuring breakdowns of (b) insertion loss and (c) crosstalk-induced power penalty.

|

Table 1. Example Elementary Silicon MZI Cells by Direct Carrier Injection

|

Table 2. Loss and Crosstalk for Key Building Blocks

Set citation alerts for the article

Please enter your email address