Qinghua Sheng, Zhao Yu, Bin Lu, Zhu Li, Qing Ye, Zexin Zhang. Real-Time Phase-Sensitive Optical Time-Domain Reflectometry Signal Processing System Based on Heterogeneous Accelerated Computing[J]. Chinese Journal of Lasers, 2020, 47(1): 0104002

Search by keywords or author

- Chinese Journal of Lasers

- Vol. 47, Issue 1, 0104002 (2020)

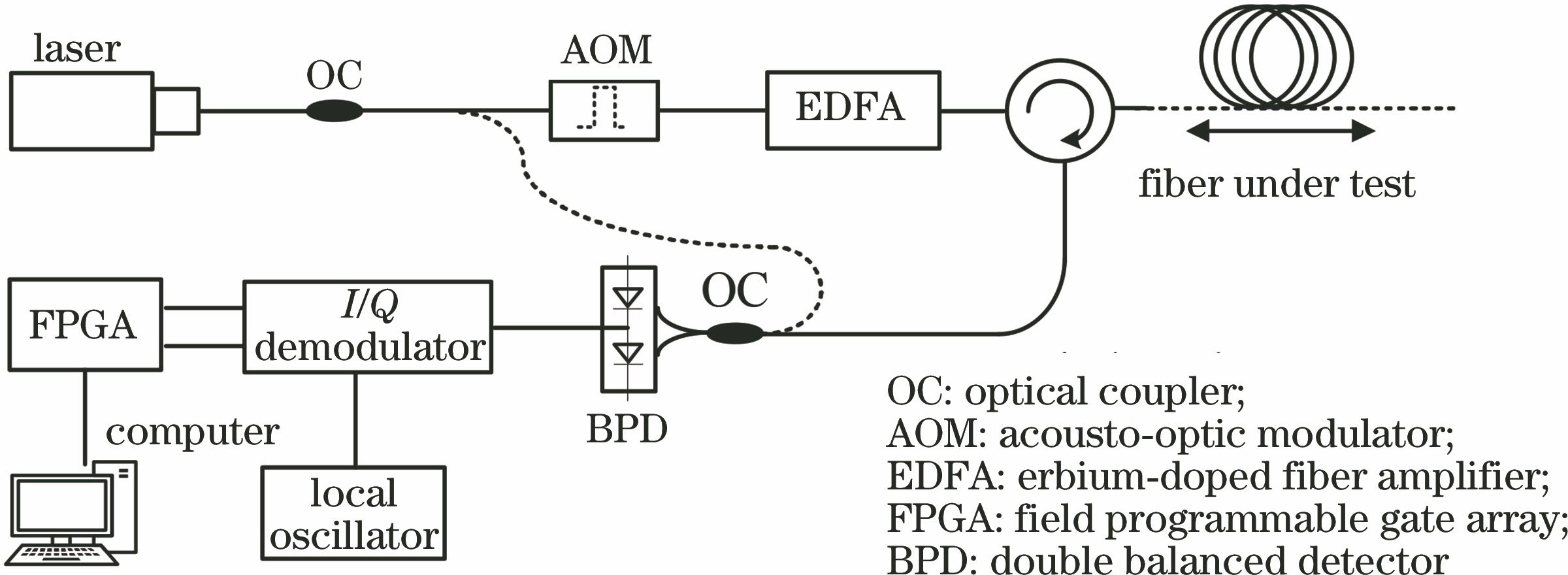

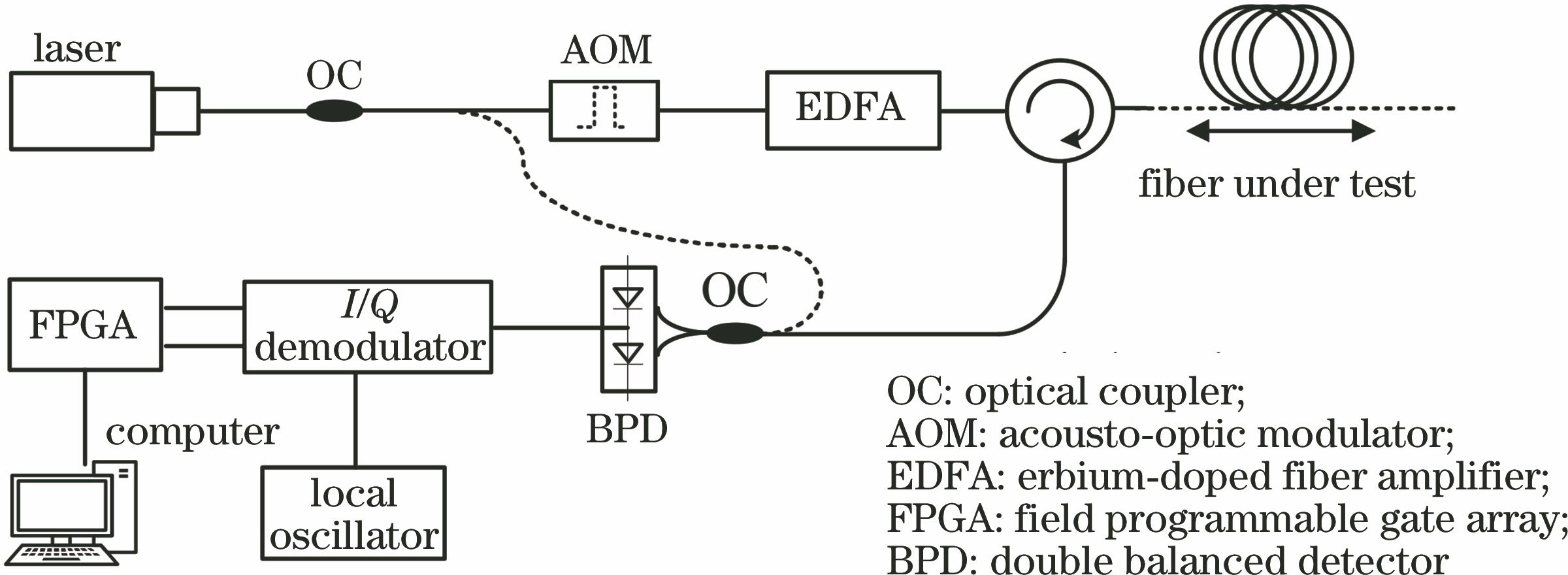

Fig. 1. Schematic of Φ-OTDR experimental system

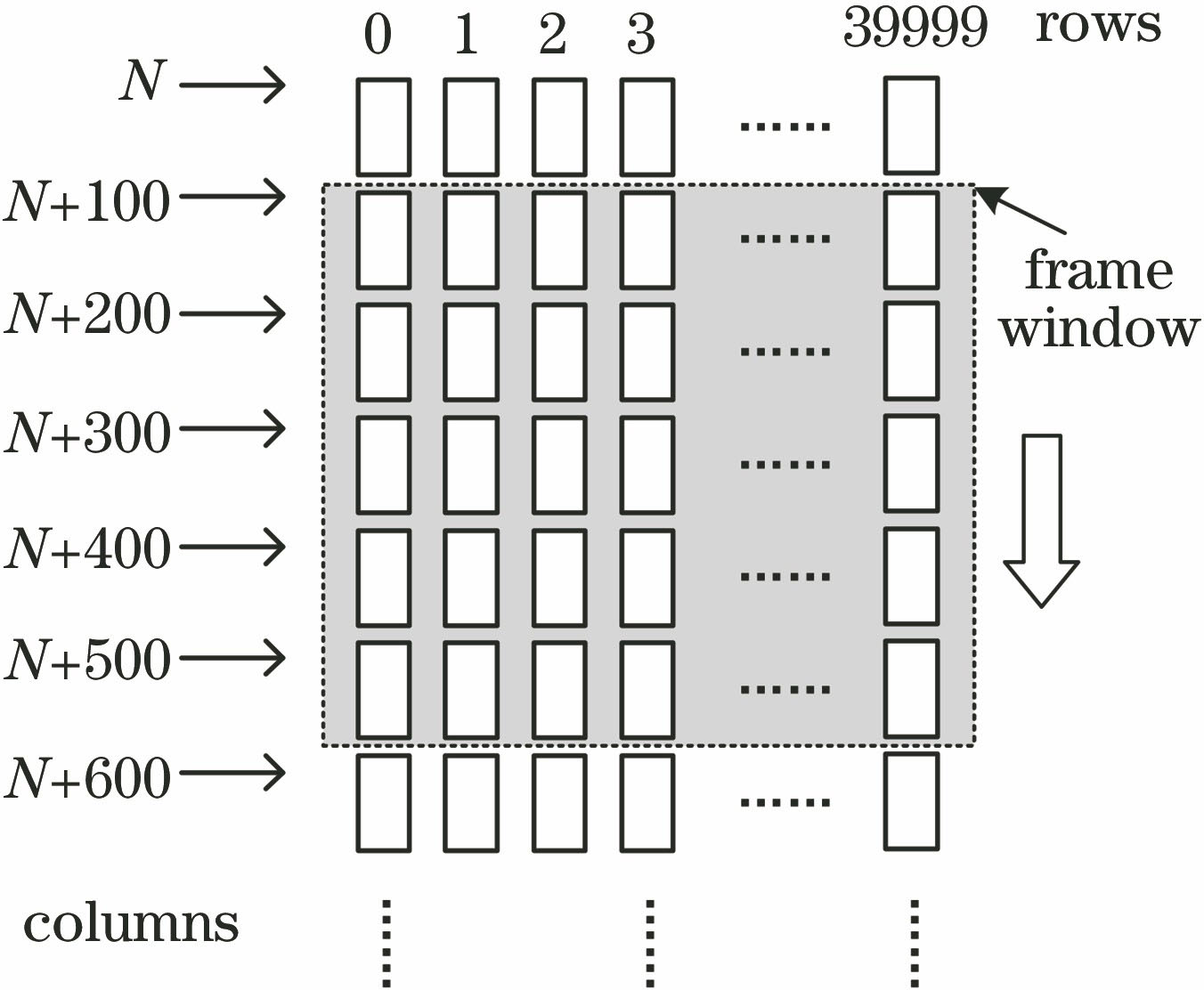

Fig. 2. Format of data frame

Fig. 3. Signal processing steps of Φ-OTDR system

Fig. 4. Schematic of FPGA implementation

Fig. 5. Pipeline using in system. (a) Structure of pipeline; (b) timing of FFT pipeline process

Fig. 6. Sliding read and combination of data frame

Fig. 7. Process of FFT calculation

Fig. 8. Process of filtering calculation

Fig. 9. Accuracy of FFT calculation

Fig. 10. Actual calculation results. (a) FPGA FFT;(b) MATLAB FFT

Fig. 11. Transition display of disturbance

Fig. 12. Disturbance andmagnified image of disturbance point

Fig. 13. Frequency spectrum analysis. (a) Frequency spectrum without disturbance point; (b) frequency spectrum with disturbance point

Fig. 14. Results of filtering. (a) Result before filtering; (b) result after filtering

|

Table 1. Resource utilization of FPGA

| |||||||||||||||||||||||||||||||||||||||||||||||

Table 2. Time differences of calculating FFT between FPGA and Matlab

|

Table 3. Real-time test results

|

Table 4. Time analysis of secondary pipeline

Set citation alerts for the article

Please enter your email address