Li Pei, Zeya Xi, Bing Bai, Jianshuai Wang, Jingjing Zheng, Jing Li, Tigang Ning, "Joint device architecture algorithm codesign of the photonic neural processing unit," Adv. Photon. Nexus 2, 036014 (2023)

Search by keywords or author

- Advanced Photonics Nexus

- Vol. 2, Issue 3, 036014 (2023)

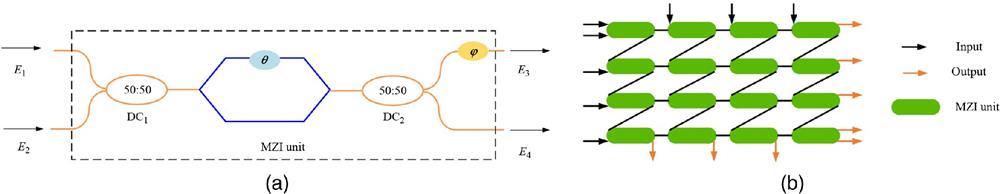

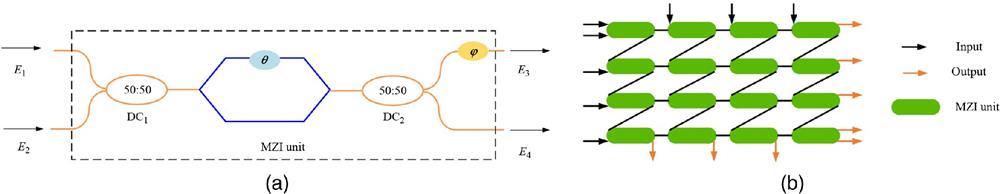

Fig. 1. (a) Schematic diagram of programmable MZI. (b) Silicon photonic neural network based on MZI array with eight input ports and eight output ports.

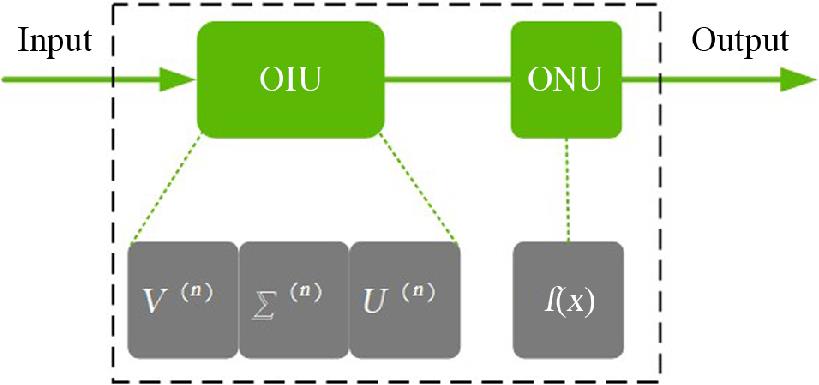

Fig. 2. Single-layer optical interference and nonlinear element on artificial neural network.

Fig. 3. Patching transform of the CONV to GEMM.

Fig. 4. CDC maps the CONV into the MZI unit.

Fig. 5. High-level architecture of a general-purpose scalable photonic MZI-based NPU system.

Fig. 6. CDC input for saving bandwidth.

Fig. 7. (a) CDC-output photonic chip architecture and (b) CDC-input photonic chip architecture.

Fig. 8. End-to-end full flow simulator architecture.

Fig. 9. (a) Utilization of different MZI array sizes. (b) Normalized bandwidth and normalized perf/power of the NPU for different MZI sizes. (c) The accuracies of different DAC control bits.

Fig. 10. The photonic chip.

Fig. 11. (a) Setup server. (b) Server application test.

|

Table 1. Summary of data set and DNN architecture.

Set citation alerts for the article

Please enter your email address