[1] H. H. Radamson, H. Zhu, Z. Wu, X. He, H. Lin, J. Liu, J. Xiang, Z. Kong, W. Xiong, J. Li, H. Cui, J. Gao, H. Yang, Y. Du, B. Xu, B. Li, X. Zhao, J. Yu, Y. Dang, G. Wang. State of the art and future perspectives in advanced CMOS technology. Nanomaterials, 10, 1555(2020).

[2] C. Sun, M. T. Wade, Y. Lee, J. S. Orcutt, L. Alloatti, M. S. Georgas, A. S. Waterman, J. M. Shainline, R. R. Avizienis, S. Lin, B. R. Moss, R. Kumar, F. Pavanello, A. H. Atabaki, H. M. Cook, A. J. Ou, J. C. Leu, Y.-H. Chen, K. Asanović, R. J. Ram, M. V. Popović, V. M. Stojanović. Single-chip microprocessor that communicates directly using light. Nature, 528, 534-538(2015).

[3] M. Smit, K. Williams, J. van der Tol. Past, present, and future of InP-based photonic integration. APL Photonics, 4, 050901(2019).

[4] IEEE Electronics. Heterogeneous Integration Roadmap 2019 Edition(2019).

[5] C. Batten, A. Joshi, J. Orcutt, A. Khilo, B. Moss, C. Holzwarth, M. Popovic, H. Li, H. Smith, J. Hoyt, F. Kartner, R. Ram, V. Stojanovic, K. Asanovic. Building manycore processor-to-DRAM networks with monolithic silicon photonics. 16th IEEE Symposium on High Performance Interconnects, 21-30(2008).

[6] D. A. B. Miller. Optical interconnects to electronic chips. Appl. Opt., 49, F59-F70(2010).

[7] D. A. B. Miller. Are optical transistors the logical next step?. Nat. Photonics, 4, 3-5(2010).

[8] C.-Z. Ning. Semiconductor nanolasers and the size-energy-efficiency challenge: a review. Adv. Photonics, 1, 014002(2019).

[9] S. Y. Chou, M. Y. Liu. Nanoscale tera-hertz metal-semiconductor-metal photodetectors. IEEE J. Quantum Electron., 28, 2358-2368(1992).

[10] J. K. Marmon, S. C. Rai, K. Wang, W. Zhou, Y. Zhang. Light-effect transistor (LET) with multiple independent gating controls for optical logic gates and optical amplification. Front. Phys., 4, 8(2016).

[11] Y. Zhang, J. K. Marmon. Light-effect transistor (LET). U.S. patent(2017).

[12] Y. Zhang. Light effect transistors for high speed and low energy switching and beyond. J. Phys. Conf. Ser., 1537, 012004(2020).

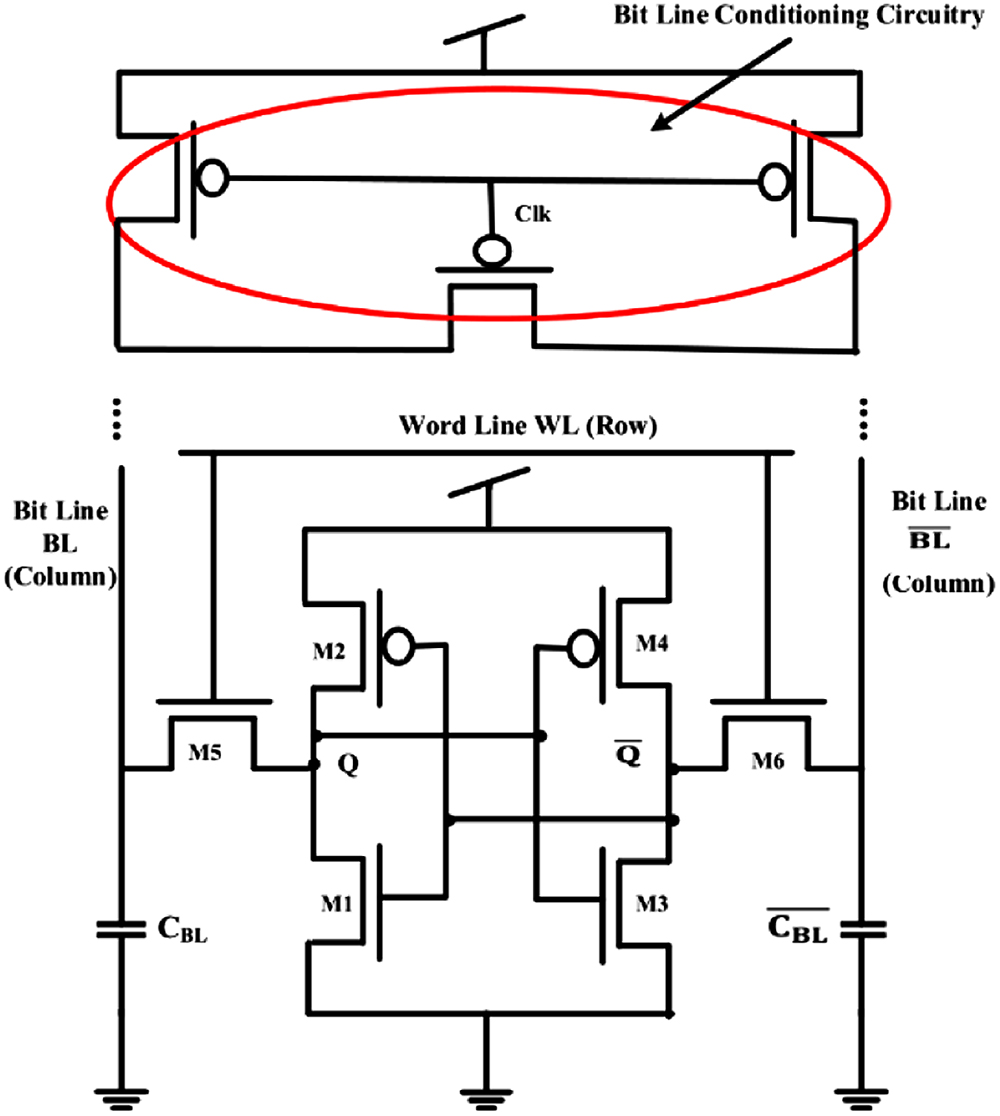

[13] S.-M. Kang, Y. Leblebici. CMOS Digital Integrated Circuits(1996).

[14] D. Hodges, H. Jackson, R. Saleh. Analysis and Design of Digital Integrated Circuits(2004).

[15] S. Panda, N. M. Kumar, C. K. Sarkar. Power, delay and noise optimization of a SRAM cell using a different threshold voltages and high performance output noise reduction circuit. 4th International Conference on Computers and Devices for Communication (CODEC), 1-4(2009).

[16] A. Garg, T. T. Kim. SRAM array structures for energy efficiency enhancement. IEEE Trans. Circuits Syst. II, 60, 351-355(2013).

[17] S. Gu, E. H. Sha, Q. Zhuge, Y. Chen, J. Hu. A time, energy, and area efficient domain wall memory-based SPM for embedded systems. IEEE Trans. Computer-Aided Design Integr. Circuits Syst., 35, 2008-2017(2016).

[18] D. Chang, I. Lin, L. Yong. ROHOM: requirement-aware online hybrid on-chip memory management for multicore systems. IEEE Trans. Computer-Aided Design Integr. Circuits Syst., 36, 357-369(2017).

[19] F. Menichelli, M. Olivieri. Static minimization of total energy consumption in memory subsystem for scratchpad-based systems-on-chips. IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 17, 161-171(2009).

[20] X. Zhang, D. Connelly, H. Takeuchi, M. Hytha, R. J. Mears, T. K. Liu. Comparison of SOI versus bulk FinFET technologies for 6T-SRAM voltage scaling at the 7-/8-nm node. IEEE Trans. Electron Devices, 64, 329-332(2017).

[21] S. Strangio, P. Palestri, D. Esseni, L. Selmi, F. Crupi. Analysis of TFET based 6T SRAM cells implemented with state of the art silicon nanowires. 44th European Solid State Device Research Conference (ESSDERC), 282-285(2014).

[22] Z. Jakšić, R. Canal. Enhancing 6T SRAM cell stability by back gate biasing techniques for 10 nm SOI FinFETs under process and environmental variations. 19th International Conference Mixed Design of Integrated Circuits and Systems (MIXDES), 103-108(2012).

[23] R. Sinha, P. Samanta. Analysis of stability and different speed boosting assist techniques towards the design and optimization of high speed SRAM cell. 19th International Symposium on VLSI Design and Test, 1-6(2015).

[24] D. Nagy, G. Indalecio, A. J. García-Loureiro, M. A. Elmessary, K. Kalna, N. Seoane. FinFET versus gate-all-around nanowire FET: performance, scaling, and variability. IEEE J. Electron Devices Soc., 6, 332-340(2018).

[25] A. Shafaei, H. Afzali-Kusha, M. Pedram. Minimizing the energy-delay product of SRAM arrays using a device-circuit-architecture co-optimization framework. 53rd ACM/EDAC/IEEE Design Automation Conference (DAC), 1-6(2016).

[26] R. J. Evans, P. D. Franzon. Energy consumption modeling and optimization for SRAM’s. IEEE J. Solid-State Circuits, 30, 571-579(1995).

[27] K. Ma, H. Liu, Y. Xiao, Y. Zhang, X. Li, S. K. Gupta, Y. Xie, V. Narayanan. Independently-controlled-gate FinFET 6T SRAM cell design for leakage current reduction and enhanced read access speed. IEEE Computer Society Annual Symposium on VLSI, 296-301(2014).

[28] R. M. Premavathi, Q. Tong, K. Choi, Y. Lee. A low power, high speed FinFET based 6T SRAM cell with enhanced write ability and read stability. International SoC Design Conference (ISOCC), 311-312(2016).

[29] H. Iwai. Roadmap for 22 nm and beyond (invited paper). Microelectron. Eng., 86, 1520-1528(2009).

[30] Semiconductor Industry Association. 2007 International Technology Roadmap for Semiconductors (ITRS): Interconnect(2007).

[31] D. M. H. Neil, H. E. Weste. CMOS VLSI Design A Circuit and Systems Perspective(2011).

[32] http://ptm.asu.edu/latest.html. http://ptm.asu.edu/latest.html

[33] A. Calimera, A. Macii, E. Macii, M. Poncino. Design techniques and architectures for low-leakage SRAMs. IEEE Trans. Circuits Syst. I, 59, 1992-2007(2012).

[34] P. K. Bikki, P. Karupannan. SRAM cell leakage control techniques for ultra low power application: a survey. Circuits Syst., 8, 23-52(2017).

[35] N. F. G. Mott, R. W. Gurney. Electronic Processes in Ionic Crystals(1948).

[36] T. Shinada, S. Okamoto, T. Kobayashi, I. Ohdomari. Enhancing semiconductor device performance using ordered dopant arrays. Nature, 437, 1128-1131(2005).

[37] H. P. Wong. Beyond the conventional transistor. IBM J. Res. Dev., 46, 133-168(2002).

[38] O. Madelung. Semiconductors: Data Handbook(2004).

[39] M. E. Levinstein, M. Shur, S. L. Rumyantsev. Handbook Series on Semiconductor Parameters(1996).

[40] R. Landauer. Spatial variation of currents and fields due to localized scatterers in metallic conduction. IBM J. Res. Dev., 1, 223-231(1957).

[41] Semiconductor Industry Association. 2013 International Technology Roadmap for Semiconductors (ITRS)(2013).

[42] K. Das, S. Samanta, P. Kumar, K. S. Narayan, A. K. Raychaudhuri. Fabrication of single Si nanowire metal–semiconductor–metal device for photodetection. IEEE Trans. Electron. Devices, 61, 1444-1450(2014).

[43] C. Soci, A. Zhang, X.-Y. Bao, H. Kim, Y. Lo, D. Wang. Nanowire photodetectors. J. Nanosci. Nanotechnol., 10, 1430-1449(2010).

[44] H. Zhang, A. V. Babichev, G. Jacopin, P. Lavenus, F. H. Julien, A. Y. Egorov, J. Zhang, T. Pauporté, M. Tchernycheva. Characterization and modeling of a ZnO nanowire ultraviolet photodetector with graphene transparent contact. J. Appl. Phys., 114, 234505(2013).

[45] A. N. Bhoj, N. K. Jha. Parasitics-aware design of symmetric and asymmetric gate-workfunction FinFET SRAMs. IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 22, 548-561(2014).

[46] E. Sicard. Introducing 10-nm FinFET technology in Microwind(2017).

[47] R. W. Mann, B. H. Calhoun. New category of ultra-thin notchless 6T SRAM cell layout topologies for sub-22 nm. 12th International Symposium on Quality Electronic Design, 1-6(2011).

[48] M. Q. Do, M. Drazdziulis, P. Larsson-Edefors, L. Bengtsson. Parameterizable architecture-level SRAM power model using circuit-simulation backend for leakage calibration. 7th International Symposium on Quality Electronic Design (ISQED), 557-563(2006).

[49] B. Nikolić. EE241B: advanced digital circuits lecture 2–scaling trends(2020).

[50] W. C. Jeong, S. Maeda, H. J. Lee, K. W. Lee, T. J. Lee, D. W. Park, B. S. Kim, J. H. Do, T. Fukai, D. J. Kwon, K. J. Nam, W. J. Rim, M. S. Jang, H. T. Kim, Y. W. Lee, J. S. Park, E. C. Lee, D. W. Ha, C. H. Park, H. Cho, S. Jung, H. K. Kang. True 7 nm platform technology featuring smallest FinFET and smallest SRAM cell by EUV, special constructs and 3rd generation single diffusion break. IEEE Symposium on VLSI Technology, 59-60(2018).

[51] T. Tsuchizawa, K. Yamada, H. Fukuda, T. Watanabe, J. Takahashi, M. Takahashi, T. Shoji, E. Tamechika, S. Itabashi, H. Morita. Microphotonics devices based on silicon microfabrication technology. IEEE J. Sel. Top. Quantum Electron., 11, 232-240(2005).

[52] J. T. Kim, S. Park. The design and analysis of monolithic integration of CMOS-compatible plasmonic waveguides for on-chip electronic–photonic integrated circuits. J. Lightwave Technol., 31, 2974-2981(2013).

[53] T. Spuesens, J. Bauwelinck, P. Regreny, D. V. Thourhout. Realization of a compact optical interconnect on silicon by heterogeneous integration of III–V. IEEE Photonics Technol. Lett., 25, 1332-1335(2013).

[54] P. Shen, C.-T. Chen, C.-H. Chang, C.-Y. Chiu, S.-L. Li, C.-C. Chang, M.-L. Wu. Implementation of chip-level optical interconnect with laser and photodetector using SOI-based 3-D guided-wave path. IEEE Photonics J., 6, 2500310(2014).

[55] L. Czornomaz, V. Djara, V. Deshpande, E. O’Connor, M. Sousa, D. Caimi, K. Cheng, J. Fompeyrine. First demonstration of InGaAs/SiGe CMOS inverters and dense SRAM arrays on Si using selective epitaxy and standard FEOL processes. IEEE Symposium on VLSI Technology, 1-2(2016).

[56] M. Li, J. Ling, Y. He, U. A. Javid, S. Xue, Q. Lin. Lithium niobate photonic-crystal electro-optic modulator. Nat. Commun., 11, 4123(2020).

[57] W. Xiong, G. Wang, Y. Du, H. Lin, X. Zhao, J. Yu, Z. Kong, Y. Dong, H. Jiang, Y. Tao, J. Li, W. Wang, H. H. Radamson. Integration of silicon nitride waveguide in Ge-on-insulator substrates for monolithic solutions in optoelectronics. J. Mater. Sci. Mater. Electron., 32, 6133-6140(2021).