- Chinese Optics Letters

- Vol. 19, Issue 10, 101302 (2021)

Abstract

1. Introduction

Optical switches with multiple input/output ports perform optical signal routing in various optical networks[

Therefore, it is highly demanded to design a large-scale polarization-insensitive silicon optical switch. Two methods have been widely adopted. One is to make all the optical elements insensitive to polarization by optimizing waveguide dimensions[

Previously, on-chip polarization controllers (PCs) have been proposed and demonstrated for polarization receivers[

Sign up for Chinese Optics Letters TOC. Get the latest issue of Chinese Optics Letters delivered right to you!Sign up now

2. Principle and Design

The proposed

![]()

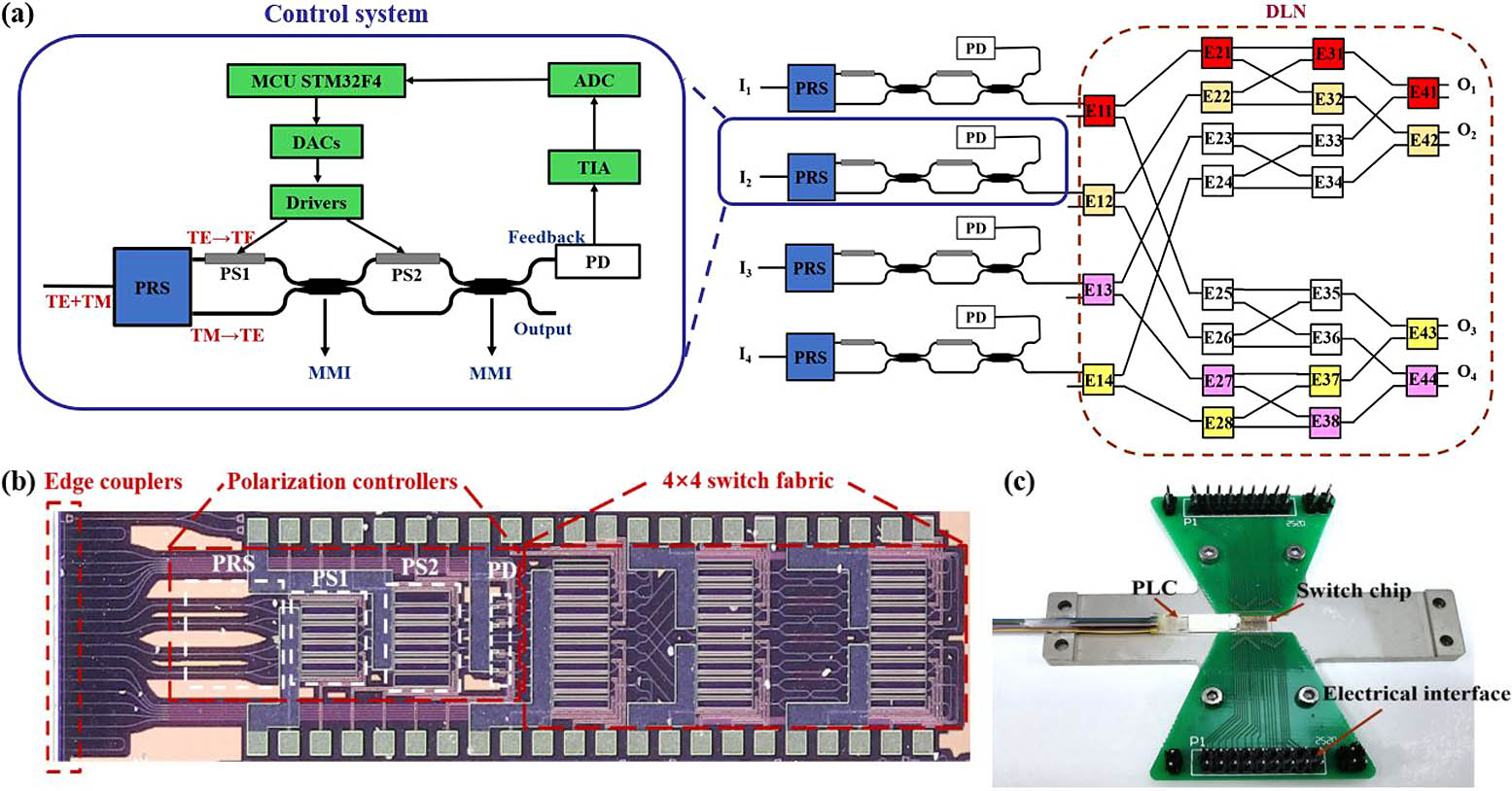

Figure 1.(a) Schematic structure of the polarization-insensitive 4 × 4 MZI switch chip. The inset shows the on-chip polarization controller and the control system. (b) Microscope image of the fabricated silicon 4 × 4 optical switch chip. (c) Photo of the packaged chip.

The

The detailed structure of the on-chip PC is illustrated in the inset of Fig. 1(a). It is constructed by a PR splitter (PRS)[

The control system to perform automated polarization adjustment consists of transimpedance amplifiers (TIAs), analog-to-digital converters (ADCs), a micro-control unit (MCU, STM32F4), digital-to-analog converters (DACs), and drivers. The optical signal from the idle output port of the MZI coupler is converted to a photocurrent by the on-chip PD, and then it is amplified by the TIA and sampled by the 12 bit ADC before feedback to the MCU. In the MCU, a polarization control algorithm based on a gradient descent method is implemented to achieve real-time feedback control.

Figure 1(b) shows the microscope image of the fabricated silicon optical switch chip. The footprint of the chip is

3. Simulation and Algorithm

Using the transfer matrix method, we can derive the normalized optical power at the feedback port of the on-chip PC as a function of phase changes (

![]()

Figure 2.Normalized feedback port power Pf as a function of Δφ1 and Δφ2 with different combinations of input polarizations: (a) TE 25%, TM 75%; (b) TE 50%, TM 50%; (c) TE 75%, TM 25%; and (d) TE 100%.

We used a polarization control algorithm based on a gradient descent method to search for the global minimum[

![]()

Figure 3.Flow chart of the polarization control algorithm.

4. Experiments

To characterize the polarization adjustment of our chip, we first adjusted the on-chip PC in the

![]()

Figure 4.(a), (b) Polarization tuning process for two random polarization states. (c), (d) Recorded TIA voltages with randomly changed input polarization when the algorithm is (c) turned off and (d) turned on.

Figure 5 shows the measured transmission spectra of the

![]()

Figure 5.Measured transmission spectra of the I2−O2 path for different input polarization states after polarization adjustment.

Figure 6 shows the measured transmission spectra of one switching state of the optical switch. The four routing paths are

![]()

Figure 6.Measured transmission spectra of one switching state at (a) port O1, (b) port O2, (c) port O3, and (d) port O4.

We performed a high-speed on–off keying (OOK) signal transmission experiment with various input polarization states for the

![]()

Figure 7.Optical transmission measurement of a 32 Gbit/s OOK signal for various input polarization states: (a) eye diagrams and (b) BER as a function of received optical power.

To evaluate the optical signal transmission through our optical switch with different input polarization states, we also measured the error-free operation at a bit error rate (BER) of

5. Conclusion

In conclusion, we have demonstrated a

References

[1] B. G. Lee, N. Dupuis, P. Pepeljugoski, L. Schares, R. Budd, J. R. Bickford, C. L. Schow. Silicon photonic switch fabrics in computer communications systems. J. Lightwave Technol., 33, 768(2015).

[2] R. Soref. Tutorial: integrated-photonic switching structures. APL Photon., 3, 021101(2018).

[3] M. Ma, A. H. K. Park, Y. Wang, H. Shoman, F. Zhang, N. A. F. Jaeger, L. Chrostowski. Sub-wavelength grating-assisted polarization splitter-rotators for silicon-on-insulator platforms. Opt. Express, 27, 17581(2019).

[4] X. Wang, G. Zhou, Z. Jin, L. Lu, G. Wu, L. Zhou, J. Chen. Wavelength-mode pulse interleaver on the silicon photonics platform. Chin. Opt. Lett., 18, 031301(2020).

[5] S. Li, R. Cong, Z. He, T. Wang, F. Zhang, S. Pan. Switchable microwave photonic filter using a phase modulator and a silicon-on-insulator micro-ring resonator. Chin. Opt. Lett., 18, 052501(2020).

[6] Y. Yue, H. Zhu, Z. Cao, J. He, M. Li. Wide-range optical sensors based on a single ring resonator with polarization multiplexing. Chin. Opt. Lett., 17, 031301(2019).

[7] P. Cheben, R. Halir, J. H. Schmid, H. A. Atwater, D. R. Smith. Subwavelength integrated photonics. Nature, 560, 565(2018).

[8] Y. Wang, D. Dai. Multimode silicon photonic waveguide corner-bend. Opt. Express, 28, 9062(2020).

[9] Y. Guo, M. Pu, X. Li, X. Ma, S. Song, Z. Zhao, X. Luo. Chip-integrated geometric metasurface as a novel platform for directional coupling and polarization sorting by spin–orbit interaction. IEEE J. Sel. Top. Quantum Electron., 24, 4700107(2018).

[10] L. Lu, S. Zhao, L. Zhou, D. Li, Z. Li, M. Wang, X. Li, J. Chen. 16 × 16 non-blocking silicon optical switch based on electro-optic Mach–Zehnder interferometers. Opt. Express, 24, 9295(2016).

[11] L. Lu, X. Li, W. Gao, X. Li, L. Zhou, J. Chen. Silicon non-blocking 4 × 4 optical switch chip integrated with both thermal and electro-optic tuners. IEEE Photon. J., 11, 6603209(2019).

[12] K. Tanizawa, K. Suzuki, M. Toyama, M. Ohtsuka, N. Yokoyama, K. Matsumaro, M. Seki, K. Koshino, T. Sugaya, S. Suda, G. Cong, T. Kimura, K. Ikeda, S. Namiki, H. Kawashima. Ultra-compact 32 × 32 strictly-non-blocking Si-wire optical switch with fan-out LGA interposer. Opt. Express, 23, 17599(2015).

[13] N. Dupuis, B. G. Lee, A. V. Rylyakov, D. M. Kuchta, C. W. Baks, J. S. Orcutt, D. M. Gill, W. M. J. Green, C. L. Schow. Modeling and characterization of a nonblocking 4×4 Mach–Zehnder silicon photonic switch fabric. J. Lightwave Technol., 33, 4329(2015).

[14] L. Qiao, W. Tang, T. Chu. 32 × 32 silicon electro-optic switch with built-in monitors and balanced-status units. Sci. Rep., 7, 42306(2017).

[15] N. Sherwood-Droz, H. Wang, L. Chen, B. G. Lee, A. Biberman, K. Bergman, M. Lipson. Optical 4×4 hitless silicon router for optical networks-on-chip (NoC). Opt. Express, 16, 15915(2008).

[16] D. Nikolova, D. M. Calhoun, Y. Liu, S. Rumley, A. Novack, T. Baehr-Jones, M. Hochberg, K. Bergman. Modular architecture for fully non-blocking silicon photonic switch fabric. Microsyst. Nanoeng., 3, 16071(2017).

[17] M. Mizukami, J. Yamaguchi, N. Nemoto, Y. Kawajiri, H. Hirata, S. Uchiyama, M. Makihara, T. Sakata, N. Shimoyama, K. Oda. 128×128 three-dimensional MEMS optical switch module with simultaneous optical path connection for optical cross-connect systems. Appl. Opt., 50, 4037(2011).

[18] T. J. Seok, N. Quack, S. Han, R. S. Muller, M. C. Wu. Large-scale broadband digital silicon photonic switches with vertical adiabatic couplers. Optica, 3, 64(2016).

[19] T. J. Seok, K. Kwon, J. Henriksson, J. Luo, M. C. Wu. Wafer-scale silicon photonic switches beyond die size limit. Optica, 6, 490(2019).

[20] S. Han, T. J. Seok, K. Yu, N. Quack, R. S. Muller, M. C. Wu. Large-scale polarization-insensitive silicon photonic MEMS switches. J. Lightwave Technol., 36, 1824(2018).

[21] H. Fukuda, K. Yamada, T. Tsuchizawa, T. Watanabe, H. Shinojima, S. Itabashi. Silicon photonic circuit with polarization diversity. Opt. Express, 16, 4872(2008).

[22] D. Dai, L. Liu, S. Gao, D. Xu, S. He. Polarization management for silicon photonic integrated circuits. Las. Photon. Rev., 7, 303(2013).

[23] K. Suzuki, K. Tanizawa, S.-H. Kim, S. Suda, G. Cong, K. Ikeda, S. Namiki, H. Kawashima. Polarization-rotator-free polarization-diversity 4 × 4 Si-wire optical switch. IEEE Photon. J., 8, 0600707(2016).

[24] K. Tanizawa, K. Suzuki, K. Ikeda, S. Namiki, H. Kawashima. Non-duplicate polarization-diversity 8 × 8 Si-wire PILOSS switch integrated with polarization splitter-rotators. Opt. Express, 25, 10885(2017).

[25] A. E. Willner, S. M. R. M. Nezam, L. Yan, Pan Zhongqi, M. C. Hauer. Monitoring and control of polarization-related impairments in optical fiber systems. J. Lightwave Technol., 22, 106(2004).

[26] D.-X. Xu, P. Cheben, D. Dalacu, A. Delâge, S. Janz, B. Lamontagne, M. J. Picard, W. N. Ye. Eliminating the birefringence in silicon-on-insulator ridge waveguides by use of cladding stress. Opt. Lett., 29, 2384(2004).

[27] S. Nakamura, S. Yanagimachi, H. Takeshita, A. Tajima, T. Hino, K. Fukuchi. Optical switches based on silicon photonics for ROADM application. IEEE J. Sel. Top. Quantum Electron., 22, 3600609(2016).

[28] W. N. Ye, D.-X. Xu, S. Janz, P. Cheben, M.-J. Picard, B. Lamontagne, N. G. Tarr. Birefringence control using stress engineering in silicon-on-insulator (SOI) waveguides. J. Lightwave Technol., 23, 1308(2005).

[29] X. Wang, K. S. Chiang. Polarization-insensitive mode-independent thermo-optic switch based on symmetric waveguide directional coupler. Opt. Express, 27, 35385(2019).

[30] H. Yang, Q. Cheng, R. Chen, K. Bergman. Polarization-diversity microring-based optical switch fabric in a switch-and-select architecture, Th3B.2(2020).

[31] K. Suzuki, R. Konoike, N. Yokoyama, M. Seki, M. Ohtsuka, S. Saitoh, S. Suda, H. Matsuura, K. Yamada, S. Namiki, H. Kawashima, K. Ikeda. Nonduplicate polarization-diversity 32 × 32 silicon photonics switch based on a SiN/Si double-layer platform. J. Lightwave Technol., 38, 226(2020).

[32] K. Sugiyama, T. Chiba, K. Tanizawa, K. Suzuki, T. Kawashima, S. Kawakami, K. Ikeda, H. Kawashima, H. Takahashi, H. Tsuda. Polarization diversity circuit based on silica waveguides and photonic crystal waveplates for a 4×4 silicon optical switch. IEICE Electron. Express, 14, 20170252(2017).

[33] K. Tanizawa, K. Suzuki, K. Ikeda, S. Namiki, H. Kawashima. Novel polarization diversity without switch duplication of a Si-wire PILOSS optical switch. Opt. Express, 24, 6861(2016).

[34] M. Ma, H. Shoman, K. Tang, S. Shekhar, N. A. F. Jaeger, L. Chrostowski. Automated control algorithms for silicon photonic polarization receiver. Opt. Express, 28, 1885(2020).

[35] W. D. Sacher, T. Barwicz, B. J. F. Taylor, J. K. S. Poon. Polarization rotator-splitters in standard active silicon photonics platforms. Opt. Express, 22, 3777(2014).

[36] R. Cao, Y. He, Q. Zhu, J. Li, S. An, Y. Zhang, Y. Su. Multi-channel 28-GHz millimeter-wave signal generation on a silicon photonic chip with automated polarization control. J. Semiconductors, 40, 052301(2019).

Set citation alerts for the article

Please enter your email address